# 32-Bit Microcontroller FM3 Family Peripheral Manual

Doc. No. 002-05586 Rev. \*A

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709

Phone (USA): 800.858.1810 Phone (Intnl): 408.943.2600 http://www.cypress.com

## **How to Use This Manual**

### **Finding a Function**

The following methods can be used to search for the explanation of a desired function in this manual:

Search from the table of the contents

The table of the contents lists the manual contents in the order of description.

Search from the register

The address where each register is located is not described in the text. To verify the address of a register, see "A. Register Map" in "Appendixes".

#### **About the Chapters**

Basically, this manual explains Timer Part..

#### **Terminology**

This manual uses the following terminology.

| Term      | Explanation                           |

|-----------|---------------------------------------|

| Word      | Indicates access in units of 32 bits. |

| Half word | Indicates access in units of 16 bits. |

| Byte      | Indicates access in units of 8 bits.  |

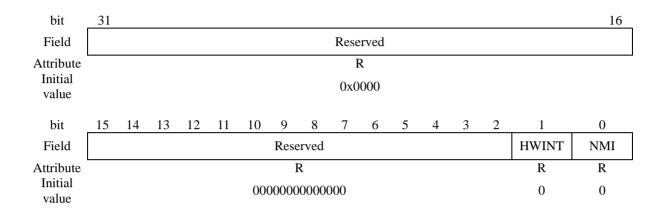

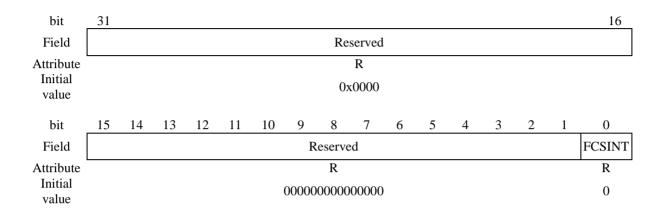

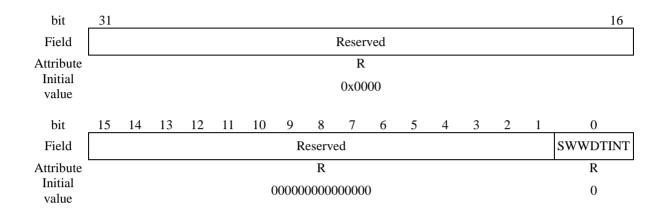

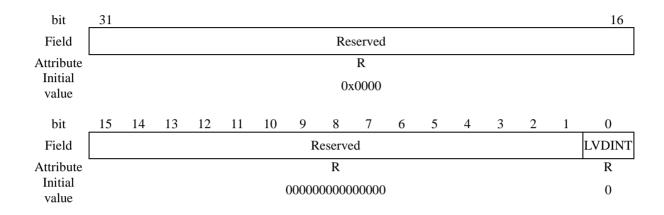

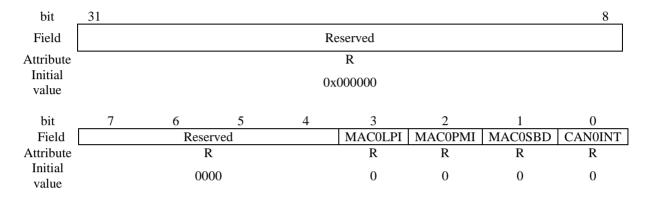

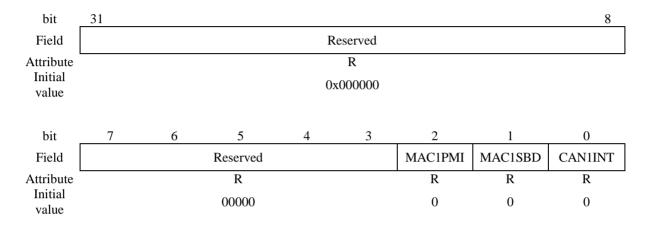

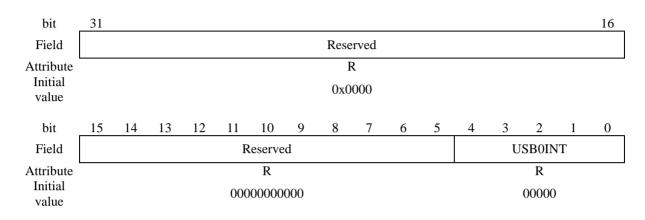

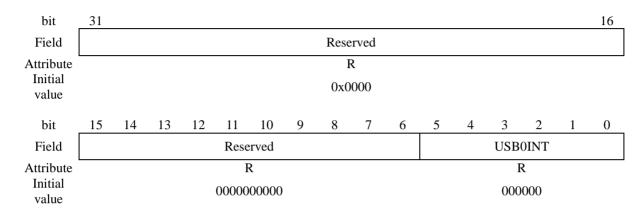

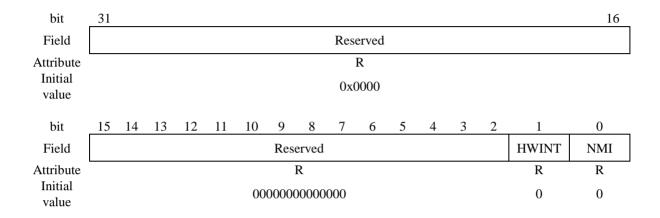

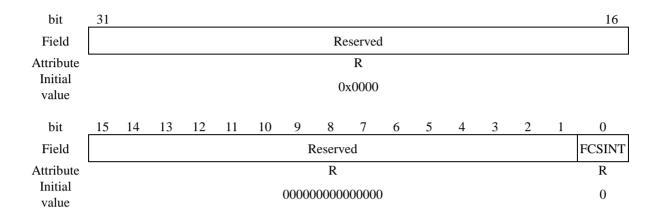

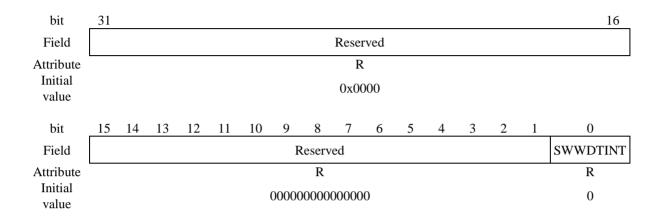

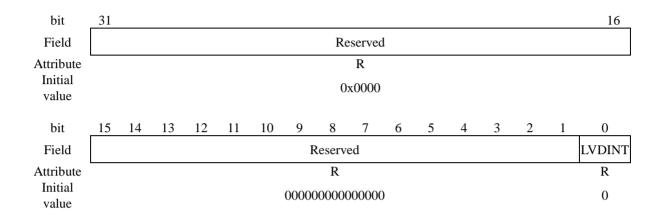

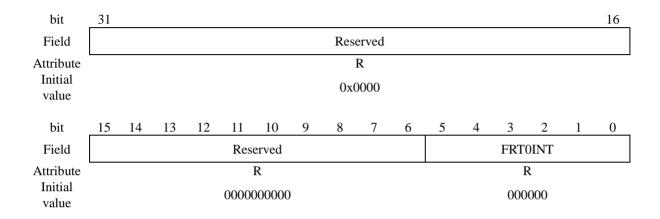

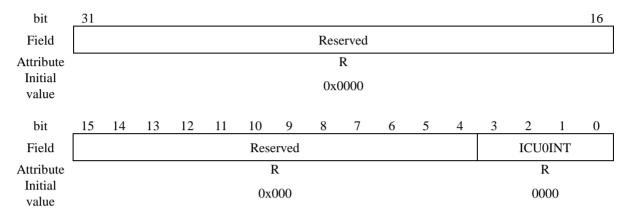

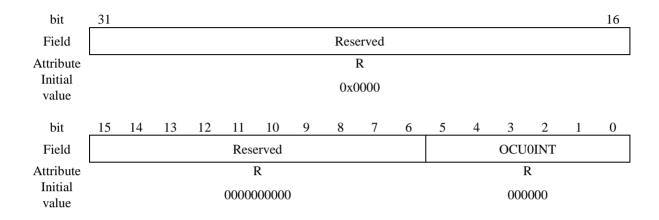

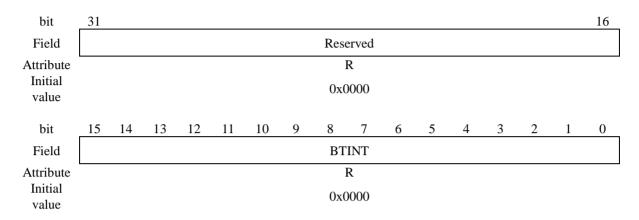

#### **Notations**

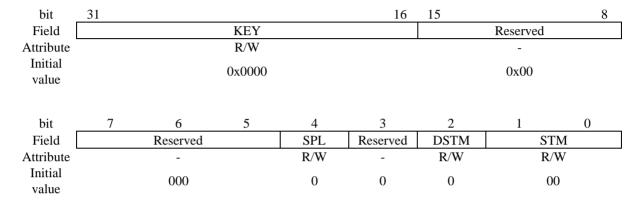

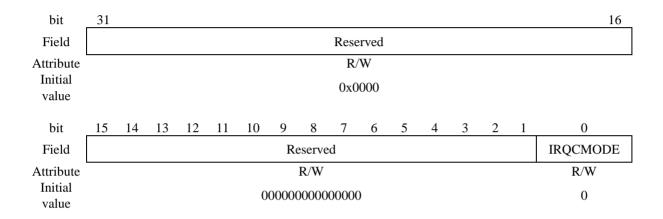

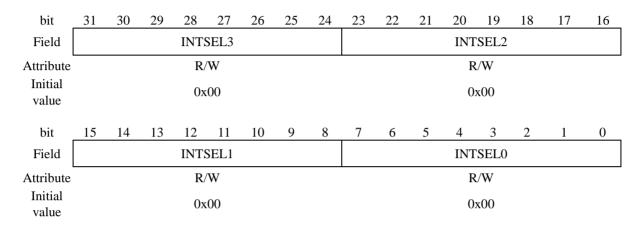

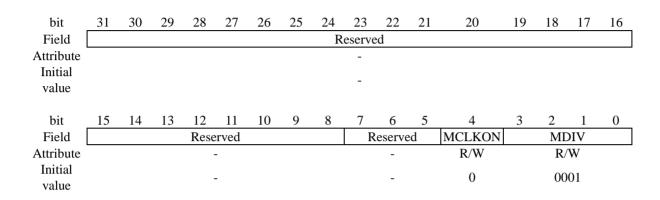

The notations in bit configuration of the register explanation of this manual are written as follows.

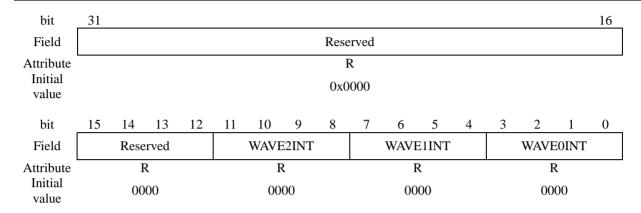

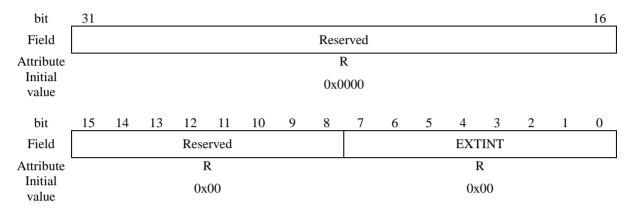

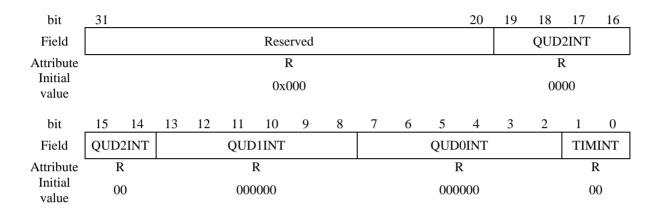

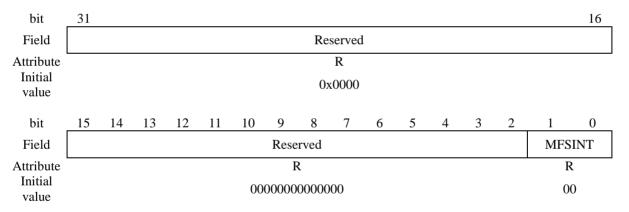

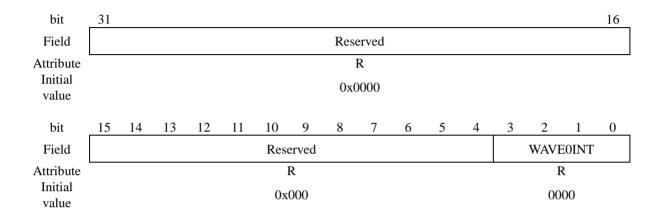

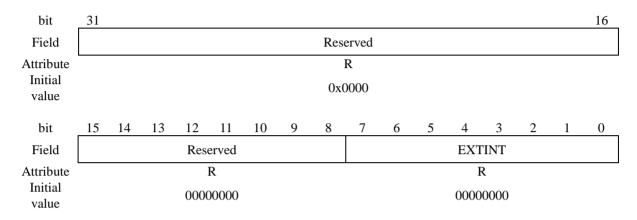

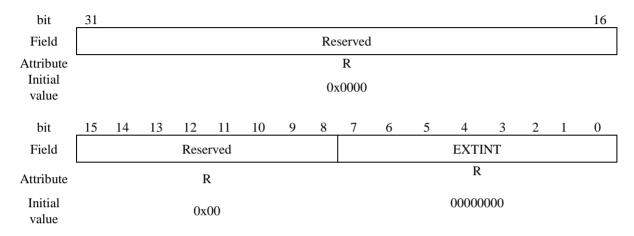

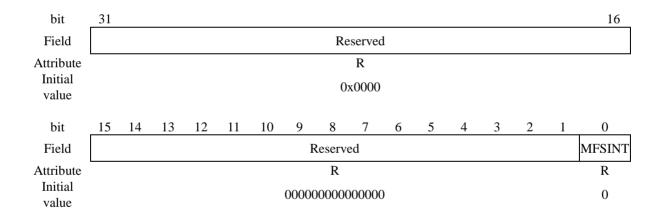

bit: bit number Field: bit field name

Attribute: Attributes for read and write of each bit

R: Read only W: Write only

R/W: Readable/Writable

-: Undefined

Initial value: Initial value of the register after reset

0: Initial value is 01: Initial value is 1

X: Initial value is undefined

The multiple bits are written as follows in this manual.

Example: bit7:0 indicates the bits from bit7 to bit0

The values such as for addresses are written as follows in this manual.

Hexadecimal number: "0x" is attached in the beginning of a value as a prefix (example: 0xFFFF) Binary number: "0b" is attached in the beginning of a value as a prefix (example: 0b1111)

Decimal number: Written using numbers only (example: 1000)

### The target products in this manual

In this manual, the products are classified into the following groups and are described as follows. For the descriptions such as "TYPEO", see the relevant items of the target product in the list below.

Table 1 TYPE0 Product list

| Description in |            | Flash me   | mory size  |              |

|----------------|------------|------------|------------|--------------|

| this manual    | 512 Kbytes | 384 Kbytes | 256 Kbytes | 128 Kbytes   |

|                | MB9BF506N  | MB9BF505N  | MB9BF504N  |              |

|                | MB9BF506R  | MB9BF505R  | MB9BF504R  |              |

|                | MB9BF506NA | MB9BF505NA | MB9BF504NA |              |

|                | MB9BF506RA | MB9BF505RA | MB9BF504RA | -            |

|                | MB9BF506NB | MB9BF505NB | MB9BF504NB |              |

|                | MB9BF506RB | MB9BF505RB | MB9BF504RB |              |

|                | MB9BF406N  | MB9BF405N  | MB9BF404N  |              |

|                | MB9BF406R  | MB9BF405R  | MB9BF404R  |              |

|                | MB9BF406NA | MB9BF405NA | MB9BF404NA | -            |

|                | MB9BF406RA | MB9BF405RA | MB9BF404RA |              |

|                | MB9BF306N  | MB9BF305N  | MB9BF304N  |              |

| TYPE0          | MB9BF306R  | MB9BF305R  | MB9BF304R  |              |

| TTPEU          | MB9BF306NA | MB9BF305NA | MB9BF304NA |              |

|                | MB9BF306RA | MB9BF305RA | MB9BF304RA | <del>-</del> |

|                | MB9BF306NB | MB9BF305NB | MB9BF304NB |              |

|                | MB9BF306RB | MB9BF305RB | MB9BF304RB |              |

|                | MB9BF106N  | MB9BF105N  | MB9BF104N  | MB9BF102N    |

|                | MB9BF106R  | MB9BF105R  | MB9BF104R  | MB9BF102R    |

|                | MB9BF106NA | MB9BF105NA | MB9BF104NA | MB9BF102NA   |

|                | MB9BF106RA | MB9BF105RA | MB9BF104RA | MB9BF102RA   |

|                |            | MB9AF105N  | MB9AF104N  | MB9AF102N    |

|                |            | MB9AF105R  | MB9AF104R  | MB9AF102R    |

|                | -          | MB9AF105NA | MB9AF104NA | MB9AF102NA   |

|                |            | MB9AF105RA | MB9AF104RA | MB9AF102RA   |

#### **Table 2 TYPE1 Product list**

| Description in this | Flash memory size |            |            |            |            |

|---------------------|-------------------|------------|------------|------------|------------|

| manual              | 512 Kbytes        | 384 Kbytes | 256 Kbytes | 128 Kbytes | 64 Kbytes  |

|                     |                   |            | MB9AF314L  | MB9AF312L  | MB9AF311L  |

|                     | MB9AF316M         | MB9AF315M  | MB9AF314M  | MB9AF312M  | MB9AF311M  |

|                     | MB9AF316N         | MB9AF315N  | MB9AF314N  | MB9AF312N  | MB9AF311N  |

|                     | MB9AF316MA        | MB9AF315MA | MB9AF314L  | MB9AF312LA | MB9AF311LA |

|                     | MB9AF316NA        | MB9AF315NA | MB9AF314M  | MB9AF312MA | MB9AF311MA |

| TVDE4               |                   |            | MB9AF314N  | MB9AF312NA | MB9AF311NA |

| TYPE1               |                   |            | MB9AF114L  | MB9AF112L  | MB9AF111L  |

|                     | MB9AF116M         | MB9AF115M  | MB9AF114M  | MB9AF112M  | MB9AF111M  |

|                     | MB9AF116N         | MB9AF115N  | MB9AF114N  | MB9AF112N  | MB9AF111N  |

|                     | MB9AF116MA        | MB9AF115MA | MB9AF114LA | MB9AF112LA | MB9AF111LA |

|                     | MB9AF116NA        | MB9AF115NA | MB9AF114MA | MB9AF112MA | MB9AF111MA |

|                     |                   |            | MB9AF114NA | MB9AF112NA | MB9AF111NA |

#### **Table 3 TYPE2 Product list**

| Description in |           | Flash memory size |            |

|----------------|-----------|-------------------|------------|

| this manual    | 1 Mbytes  | 768 Kbytes        | 512 Kbytes |

|                | MB9BFD18S | MB9BFD17S         | MB9BFD16S  |

|                | MB9BFD18T | MB9BFD17T         | MB9BFD16T  |

|                | MB9BF618S | MB9BF617S         | MB9BF616S  |

|                | MB9BF618T | MB9BF617T         | MB9BF616T  |

|                | MB9BF518S | MB9BF517S         | MB9BF516S  |

|                | MB9BF518T | MB9BF517T         | MB9BF516T  |

|                | MB9BF418S | MB9BF417S         | MB9BF416S  |

| TYPE2          | MB9BF418T | MB9BF417T         | MB9BF416T  |

|                | MB9BF318S | MB9BF317S         | MB9BF316S  |

|                | MB9BF318T | MB9BF317T         | MB9BF316T  |

|                | MB9BF218S | MB9BF217S         | MB9BF216S  |

|                | MB9BF218T | MB9BF217T         | MB9BF216T  |

|                | MB9BF118S | MB9BF117S         | MB9BF116S  |

|                | MB9BF118T | MB9BF117T         | MB9BF116T  |

#### **Table 4 TYPE3 Product list**

| Description in | Flash me                 | mory size                |

|----------------|--------------------------|--------------------------|

| this manual    | 128 Kbytes               | 64 Kbytes                |

|                | MB9AF132K<br>MB9AF132L   | MB9AF131K<br>MB9AF131L   |

| TYPE3          | MB9AF132KA<br>MB9AF132LA | MB9AF131KA<br>MB9AF131LA |

|                | MB9AF132KB<br>MB9AF132LB | MB9AF131KB<br>MB9AF131LB |

#### **Table 5 TYPE4 Product list**

| Description in | Flash memory size      |                        |                        |                        |

|----------------|------------------------|------------------------|------------------------|------------------------|

| this manual    | 512 Kbytes             | 384 Kbytes             | 256 Kbytes             | 128 Kbytes             |

| TYPE4          | MB9BF516N<br>MB9BF516R | MB9BF515N<br>MB9BF515R | MB9BF514N<br>MB9BF514R | MB9BF512N<br>MB9BF512R |

|                | MB9BF416N<br>MB9BF416R | MB9BF415N<br>MB9BF415R | MB9BF414N<br>MB9BF414R | MB9BF412N<br>MB9BF412R |

|                | MB9BF316N<br>MB9BF316R | MB9BF315N<br>MB9BF315R | MB9BF314N<br>MB9BF314R | MB9BF312N<br>MB9BF312R |

|                | MB9BF116N<br>MB9BF116R | MB9BF115N<br>MB9BF115R | MB9BF114N<br>MB9BF114R | MB9BF112N<br>MB9BF112R |

## **Table 6 TYPE5 Product list**

| Description in this | Flash me   | mory size |

|---------------------|------------|-----------|

| manual              | 128 Kbytes | 64 Kbytes |

| TYPE5               | MB9AF312K  | MB9AF311K |

|                     | MB9AF112K  | MB9AF111K |

Table 7 TYPE6 product list

| Description in |            | Flash memory size |            |

|----------------|------------|-------------------|------------|

| this manual    | 256 Kbytes | 128 Kbytes        | 64 Kbytes  |

|                | MB9AFB44L  | MB9AFB42L         | MB9AFB41L  |

|                | MB9AFB44M  | MB9AFB42M         | MB9AFB41M  |

|                | MB9AFB44N  | MB9AFB42N         | MB9AFB41N  |

|                | MB9AFB44LA | MB9AFB42LA        | MB9AFB41LA |

|                | MB9AFB44MA | MB9AFB42MA        | MB9AFB41MA |

|                | MB9AFB44NA | MB9AFB42NA        | MB9AFB41NA |

|                | MB9AFB44LB | MB9AFB42LB        | MB9AFB41LB |

|                | MB9AFB44MB | MB9AFB42MB        | MB9AFB41MB |

|                | MB9AFB44NB | MB9AFB42NB        | MB9AFB41NB |

|                | MB9AFA44L  | MB9AFA42L         | MB9AFA41L  |

|                | MB9AFA44M  | MB9AFA42M         | MB9AFA41M  |

|                | MB9AFA44N  | MB9AFA42N         | MB9AFA41N  |

|                | MB9AFA44LA | MB9AFA42LA        | MB9AFA41LA |

|                | MB9AFA44MA | MB9AFA42MA        | MB9AFA41MA |

|                | MB9AFA44NA | MB9AFA42NA        | MB9AFA41NA |

|                | MB9AFA44LB | MB9AFA42LB        | MB9AFA41LB |

|                | MB9AFA44MB | MB9AFA42MB        | MB9AFA41MB |

| T) (DE 0       | MB9AFA44NB | MB9AFA42NB        | MB9AFA41NB |

| TYPE6          | MB9AF344L  | MB9AF342L         | MB9AF341L  |

|                | MB9AF344M  | MB9AF342M         | MB9AF341M  |

|                | MB9AF344N  | MB9AF342N         | MB9AF341N  |

|                | MB9AF344LA | MB9AF342LA        | MB9AF341LA |

|                | MB9AF344MA | MB9AF342MA        | MB9AF341MA |

|                | MB9AF344NA | MB9AF342NA        | MB9AF341NA |

|                | MB9AF344LB | MB9AF342LB        | MB9AF341LB |

|                | MB9AF344MB | MB9AF342MB        | MB9AF341MB |

|                | MB9AF344NB | MB9AF342NB        | MB9AF341NB |

|                | MB9AF144L  | MB9AF142L         | MB9AF141L  |

|                | MB9AF144M  | MB9AF142M         | MB9AF141M  |

|                | MB9AF144N  | MB9AF142N         | MB9AF141N  |

|                | MB9AF144LA | MB9AF142LA        | MB9AF141LA |

|                | MB9AF144MA | MB9AF142MA        | MB9AF141MA |

|                | MB9AF144NA | MB9AF142NA        | MB9AF141NA |

|                | MB9AF144LB | MB9AF142LB        | MB9AF141LB |

|                | MB9AF144MB | MB9AF142MB        | MB9AF141MB |

|                | MB9AF144NB | MB9AF142NB        | MB9AF141NB |

## Table 8 TYPE7 product list

| Description in | Flash mem  | nory size |

|----------------|------------|-----------|

| this manual    | 128 Kbytes | 64 Kbytes |

|                | MB9AFA32L  | MB9AFA31L |

|                | MB9AFA32M  | MB9AFA31M |

|                | MB9AFA32N  | MB9AFA31N |

|                | MB9AF132M  | MB9AF131M |

| TYPE7          | MB9AF132N  | MB9AF131N |

| ITFE/          | MB9AFAA2L  | MB9AFAA1L |

|                | MB9AFAA2M  | MB9AFAA1M |

|                | MB9AFAA2N  | MB9AFAA1N |

|                | MB9AF1A2M  | MB9AF1A1M |

|                | MB9AF1A2N  | MB9AF1A1N |

## Table 9 TYPE8 product list

| Description in |            | Flash memory size |            |

|----------------|------------|-------------------|------------|

| this manual    | 512 Kbytes | 384 Kbytes        | 256 Kbytes |

|                | MB9AF156M  | MB9AF155M         | MB9AF154M  |

|                | MB9AF156N  | MB9AF155N         | MB9AF154N  |

|                | MB9AF156R  | MB9AF155R         | MB9AF154R  |

|                | MB9AF156MA | MB9AF155MA        | MB9AF154MA |

| TYPE8          | MB9AF156NA | MB9AF155NA        | MB9AF154NA |

|                | MB9AF156RA | MB9AF155RA        | MB9AF154RA |

|                | MB9AF156MB | MB9AF155MB        | MB9AF154MB |

|                | MB9AF156NB | MB9AF155NB        | MB9AF154NB |

|                | MB9AF156RB | MB9AF155RB        | MB9AF154RB |

## Table 10 TYPE9 product list

| Description in |            | Flash memory size |           |

|----------------|------------|-------------------|-----------|

| this manual    | 256 Kbytes | 128 Kbytes        | 64 Kbytes |

|                | MB9BF524K  | MB9BF522K         | MB9BF521K |

|                | MB9BF524L  | MB9BF522L         | MB9BF521L |

|                | MB9BF524M  | MB9BF522M         | MB9BF521M |

|                | MB9BF324K  | MB9BF322K         | MB9BF321K |

| TYPE9          | MB9BF324L  | MB9BF322L         | MB9BF321L |

|                | MB9BF324M  | MB9BF322M         | MB9BF321M |

|                | MB9BF124K  | MB9BF122K         | MB9BF121K |

|                | MB9BF124L  | MB9BF122L         | MB9BF121L |

|                | MB9BF124M  | MB9BF122M         | MB9BF121M |

## Table 11 TYPE10 product list

| Description in | Flash memory size |

|----------------|-------------------|

| this manual    | 64 Kbytes         |

| TYPE10         | MB9BF121J         |

## Table 12 TYPE11 product list

| Description in | Flash memory size |

|----------------|-------------------|

| this manual    | 64 Kbytes         |

|                | MB9AF421K         |

| TYPE11         | MB9AF421L         |

| 'ב             | MB9AF121K         |

|                | MB9AF121L         |

## Table 13 TYPE12 product list

| this manual 1.5 Mbytes 1 Mbytes                                                                                                                                                                                                                                                                                                                                                                      |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| MB9BF529S MB9BF529T MB9BF528T MB9BF528A MB9BF528A MB9BF528TA MB9BF428S MB9BF429S MB9BF428S MB9BF428T MB9BF428A MB9BF428A MB9BF429TA MB9BF329S MB9BF329S MB9BF329T MB9BF329SA MB9BF329TA MB9BF329TA MB9BF328TA MB9BF129S MB9BF129S MB9BF128S MB9BF128T MB9BF128TA MB9BF128TA |  |

| CHAPTER 1: System Overview                                       | 21 |

|------------------------------------------------------------------|----|

| 1. Bus Architecture                                              | 22 |

| 1.1. Bus Block Diagram                                           | 24 |

| 1.2. Memory Architecture                                         | 25 |

| 1.3. Memory Map                                                  | 26 |

| 1.4. Peripheral Address Map                                      | 27 |

| 2. Cortex-M3 Architecture                                        | 30 |

| 2.1. Option configuration                                        | 32 |

| 3. Mode                                                          | 34 |

| CHAPTER 2-1: Clock                                               |    |

| Clock Generation Unit Overview                                   | 38 |

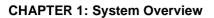

| 2. Clock Generation Unit Configuration/Block Diagram             | 39 |

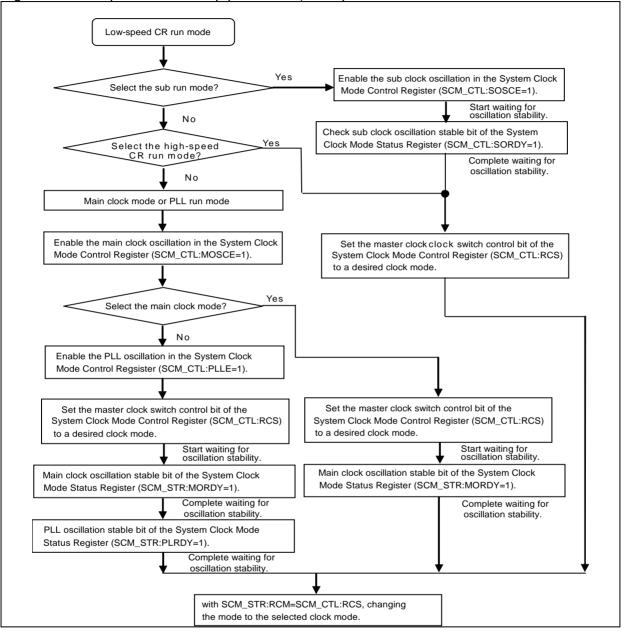

| 3. Clock Generation Unit Operations                              | 43 |

| 3.1. Selecting the clock mode                                    | 43 |

| 3.2. Internal bus clock frequency division control               | 44 |

| 3.3. PLL clock control                                           | 45 |

| 3.4. Oscillation stabilization wait time                         | 50 |

| 3.5. Interrupt Factors                                           | 52 |

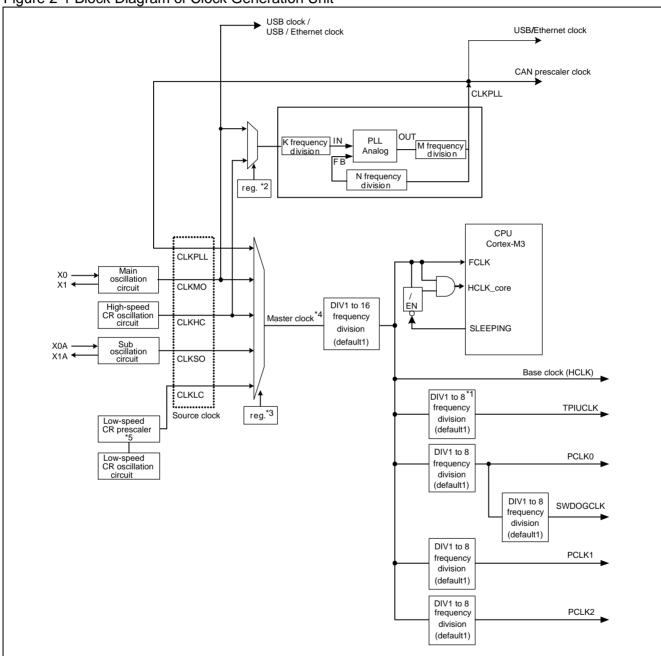

| Clock Setup Procedure Examples                                   | 53 |

| 5. List of Clock Generation Unit Registers                       |    |

| 5.1. System Clock Mode Control Register (SCM_CTL)                | 56 |

| 5.2. System Clock Mode Status Register (SCM_STR)                 | 58 |

| 5.3. Base Clock Prescaler Register (BSC_PSR)                     | 60 |

| 5.4. APB0 Prescaler Register (APBC0_PSR)                         |    |

| 5.5. APB1 Prescaler Register (APBC1_PSR)                         | 62 |

| 5.6. APB2 Prescaler Register (APBC2_PSR)                         |    |

| 5.7. Software Watchdog Clock Prescaler Register (SWC_PSR)        |    |

| 5.8. Trace Clock Prescaler Register (TTC_PSR)                    |    |

| 5.9. Clock Stabilization Wait Time Register (CSW_TMR)            |    |

| 5.10. PLL Clock Stabilization Wait Time Setup Register (PSW_TMR) | 68 |

| 5.11. PLL Control Register 1 (PLL_CTL1)                          |    |

| 5.12. PLL Control Register 2 (PLL_CTL2)                          |    |

| 5.13. Debug Break Watchdog Timer Control Register (DBWDT_CTL)    | 73 |

| 5.14. Interrupt Enable Register (INT_ENR)                        |    |

| 5.15. Interrupt Status Register (INT_STR)                        |    |

| 5.16. Interrupt Clear Register (INT_CLR)                         | 76 |

| 6. Clock Generation Unit Usage Precautions                       | 78 |

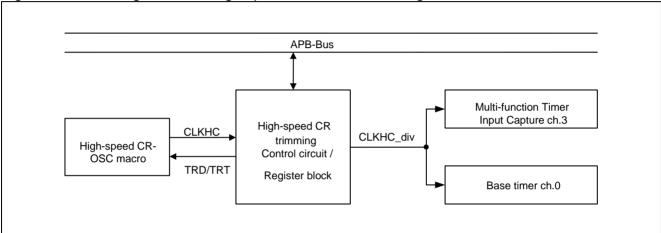

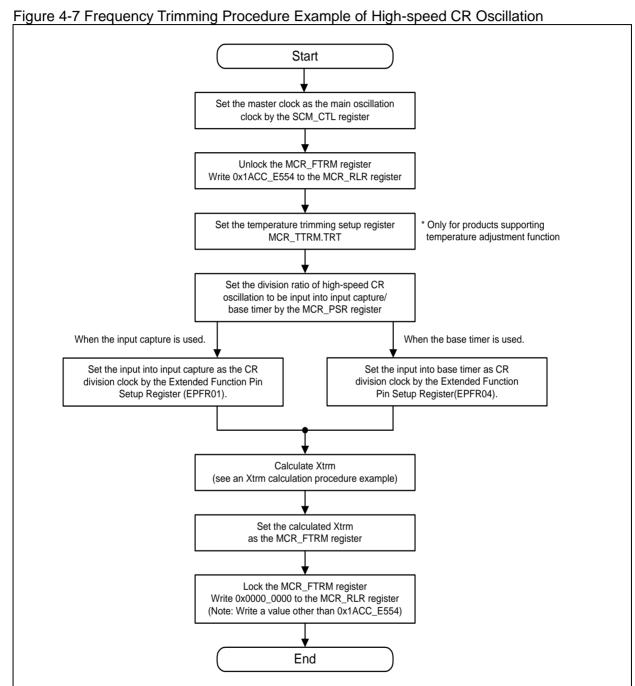

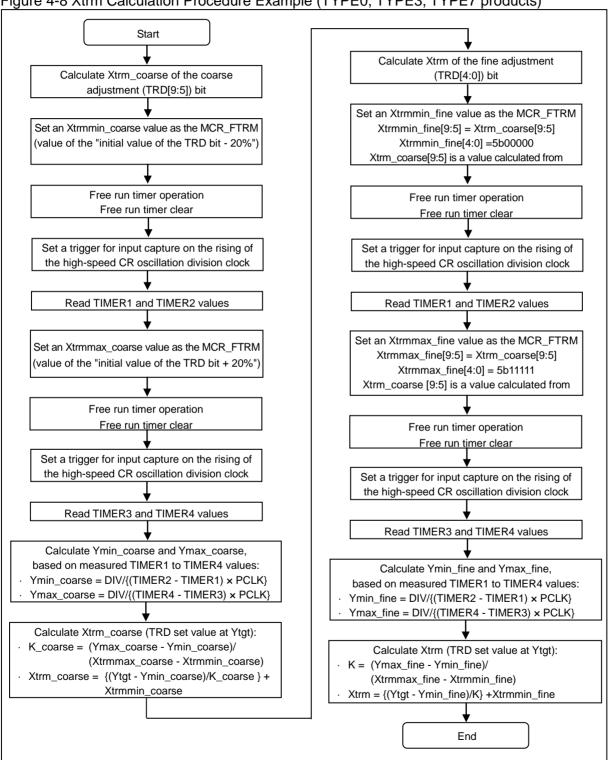

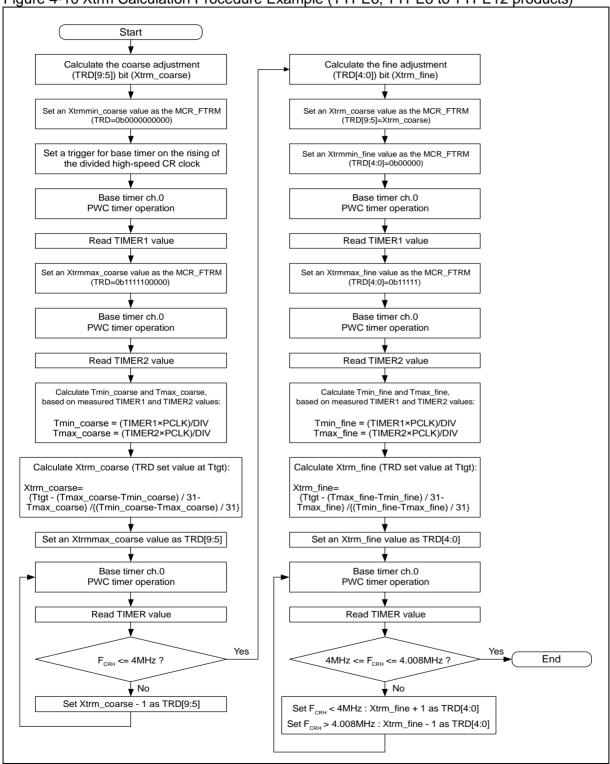

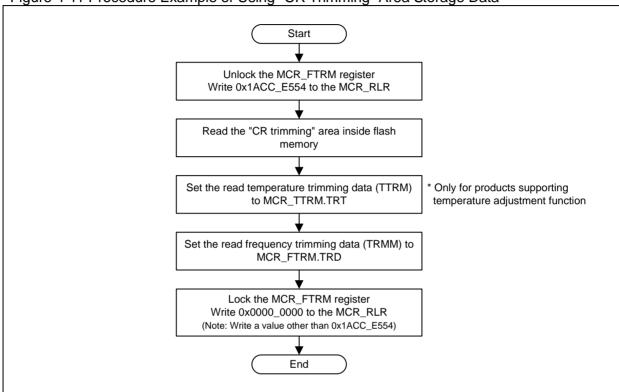

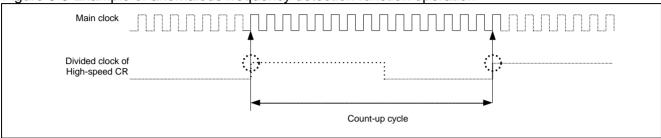

| CHAPTER 2-2: High-Speed CR Trimming                                        |            |

|----------------------------------------------------------------------------|------------|

| High-Speed CR Trimming Function Overview                                   |            |

| 2. High-Speed CR Trimming Function Configuration and Block Diagram         | 83         |

| 3. High-Speed CR Trimming Function Operation                               | 84         |

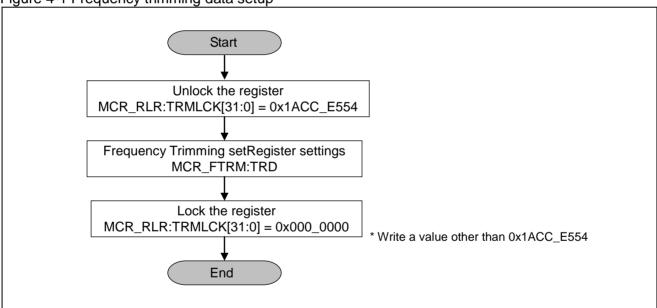

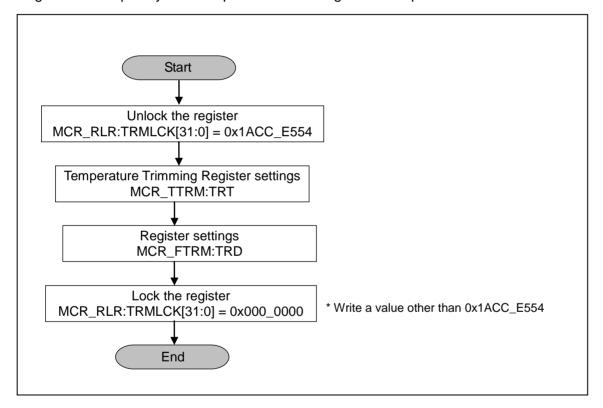

| 4. High-Speed CR Trimming Function Setup Procedure Example                 | 85         |

| 5. High-Speed CR Trimming Function Register List                           | 98         |

| 5.1. High-speed CR oscillation Frequency Division Setup Register (MCR_PSR) | 99         |

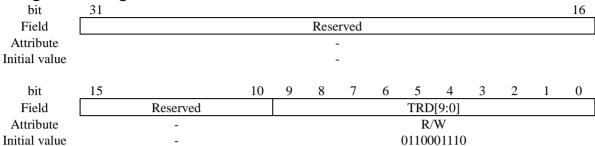

| 5.2. High-speed CR oscillation Frequency Trimming Register (MCR_FTRM)      | 101        |

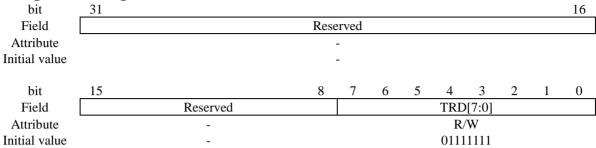

| 5.3. High-speed CR oscillation Frequency Trimming Register (MCR_TTRM)      |            |

| 5.4. High-Speed CR Oscillation Register Write-Protect Register (MCR_RLR)   |            |

| 6. High-Speed CR Trimming Function Usage Precautions                       |            |

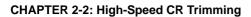

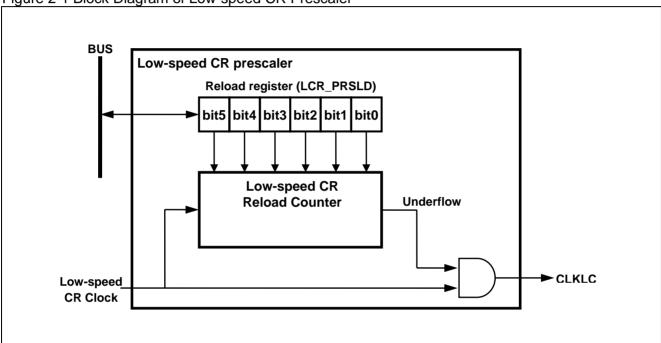

| CHAPTER 2-3: Low-Speed CR Prescaler                                        |            |

| 1. Low-Speed CR Prescaler Overview                                         |            |

| 2. Low-Speed CR Prescaler Configuration                                    |            |

| Low-Speed CR Prescaler Operation amd Setup Procedure Example               |            |

| 4. Low-Speed CR Prescaler Register                                         |            |

| 4.1. Low-speed CR Prescaler Control Register (LCR_PRSLD)                   |            |

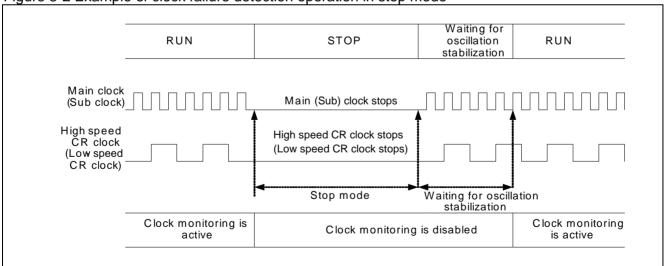

| CHAPTER 3: Clock supervisor                                                |            |

| 1. Overview                                                                |            |

| Configurations and Block Diagrams                                          |            |

| Explanation of Operations                                                  |            |

| Setup Procedure Examples                                                   |            |

| Operation Examples                                                         |            |

| 6. Register list                                                           |            |

| 6.1. CSV control register (CSV_CTL)                                        |            |

| 6.2. CSV status register (CSV_STR)                                         |            |

| 6.3. Frequency detection window setting register (Upper) (FCSWH_CTL)       |            |

| 6.4. Frequency detection window setting register (Lower) (FCSWL_CTL)       |            |

| 6.5. Frequency detection counter register (FCSWD_CTL)                      |            |

| 7. Usage Precautions                                                       |            |

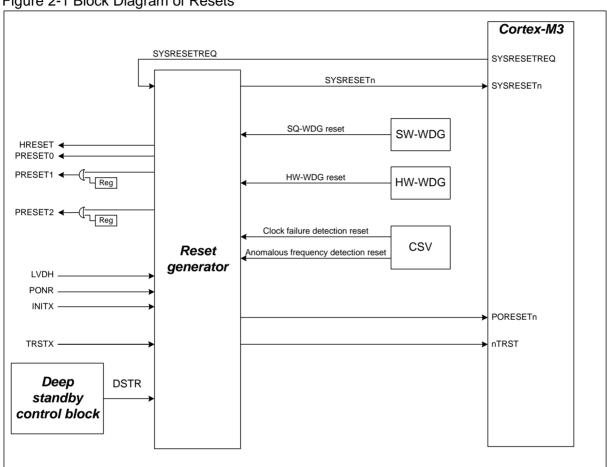

| CHAPTER 4: Resets                                                          |            |

| 1. Overview                                                                |            |

| 2. Configuration                                                           |            |

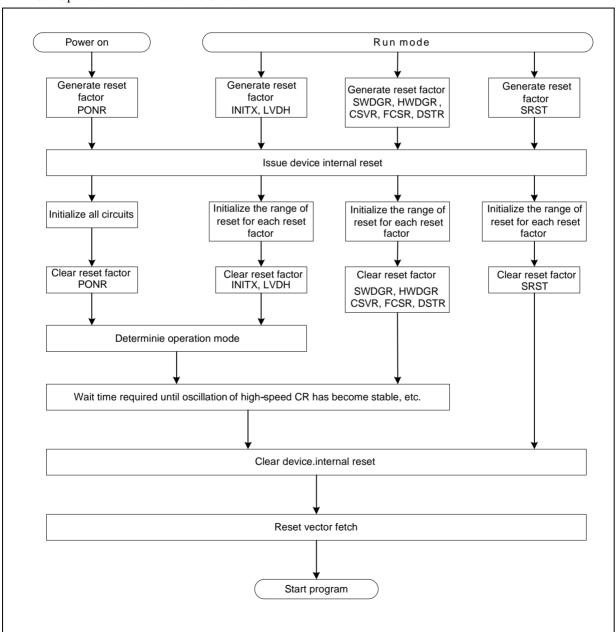

| Explanation of Operations                                                  |            |

| 3.1. Reset Factors                                                         |            |

| 3.2. Resetting Inside the Device                                           |            |

| 3.2.1. Resetts to Cortex-M3                                                |            |

| 3.2.2. Resets to Peripheral Circuit                                        |            |

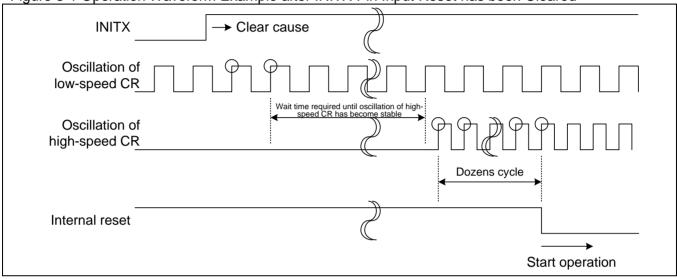

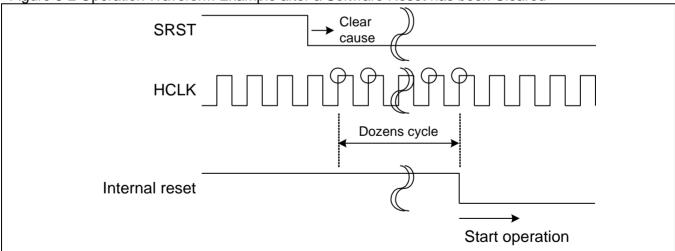

| 3.3. Reset Sequence                                                        |            |

| 3.4. Operations After Resets are Cleared                                   |            |

| 4. Registers                                                               |            |

| 4.1. Reset Factor Register (RST_STR)                                       |            |

| <del>-</del>                                                               |            |

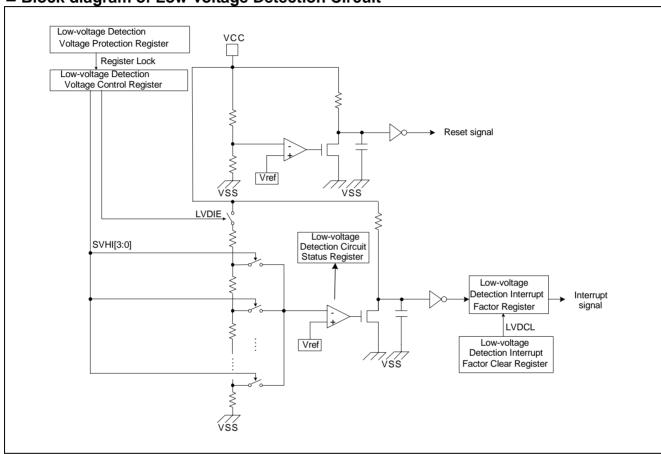

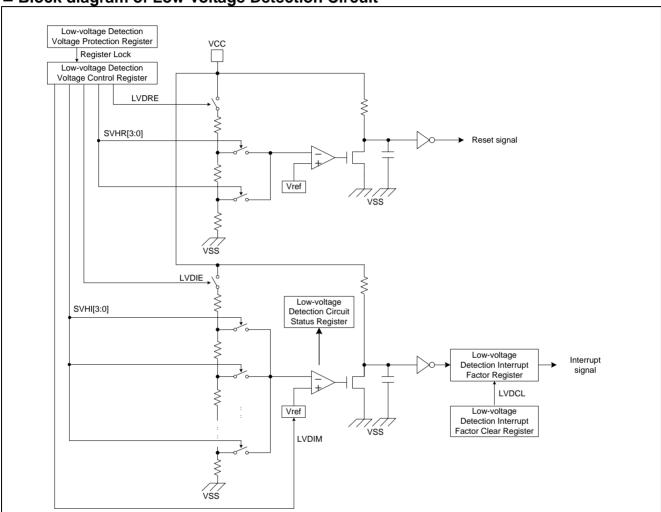

| CHAPTER 5-1: Low-voltage Detection Configuration                           |            |

| 1. Configuration                                                           |            |

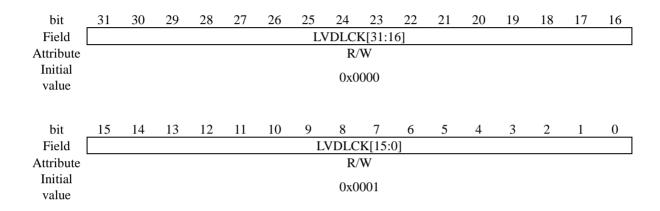

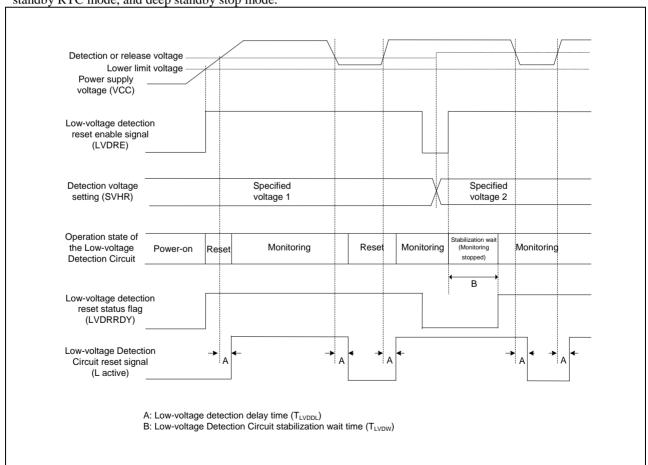

| CHAPTER 5-2: Low-voltage Detection (A)                                     |            |

| 1. Overview                                                                |            |

| · · · · · · · · · · · · · · · · · · ·                                      |            |

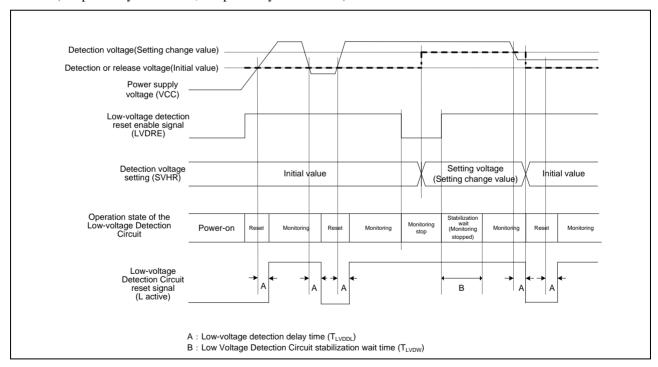

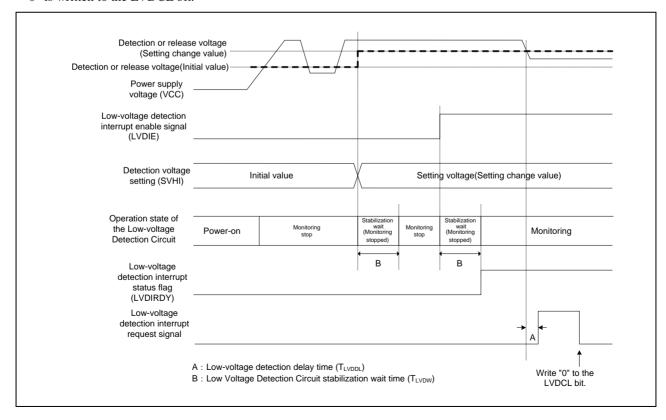

| Explanation of Operations                                                  | 163<br>166 |

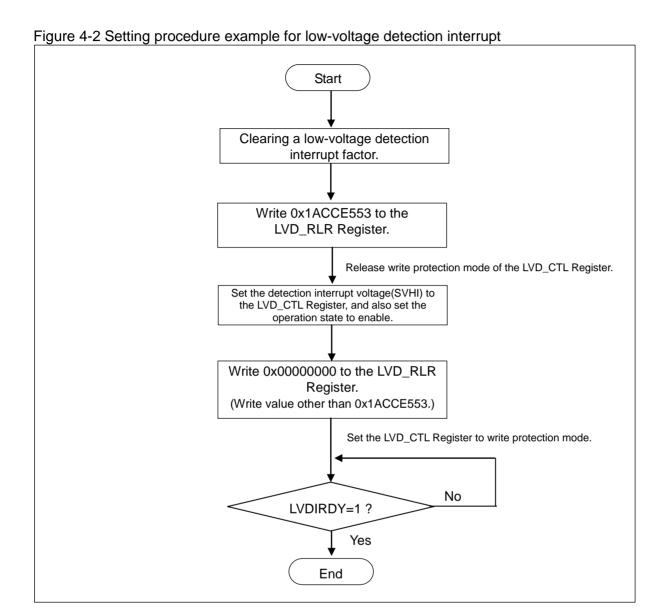

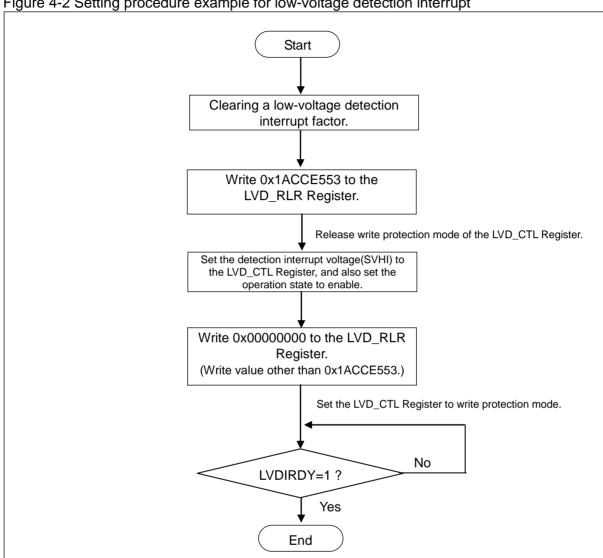

| 4 Deno Procedure Examples                                                  | Inh        |

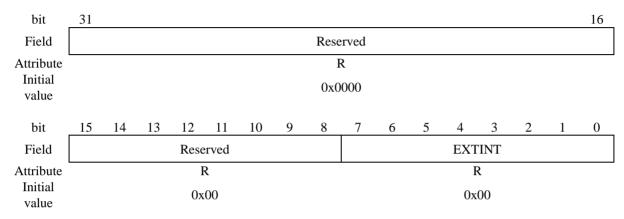

| 5. Registers                                                                          | 167  |

|---------------------------------------------------------------------------------------|------|

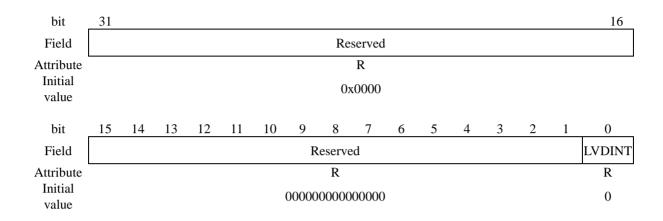

| 5.1. Low-voltage Detection Voltage Control Register (LVD_CTL)                         | 168  |

| 5.2. Low-voltage Detection Interrupt Register (LVD_STR)                               | 170  |

| 5.3. Low-voltage Detection Interrupt Clear Register (LVD_CLR)                         | 171  |

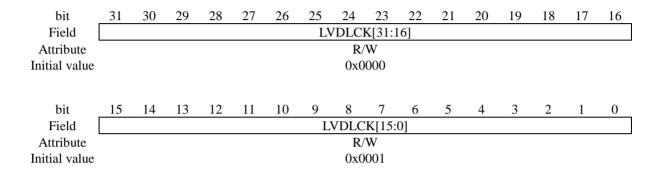

| 5.4. Low-voltage Detection Voltage Protection Register (LVD_RLR)                      |      |

| 5.5. Low-voltage Detection Circuit Status Register (LVD_STR2)                         |      |

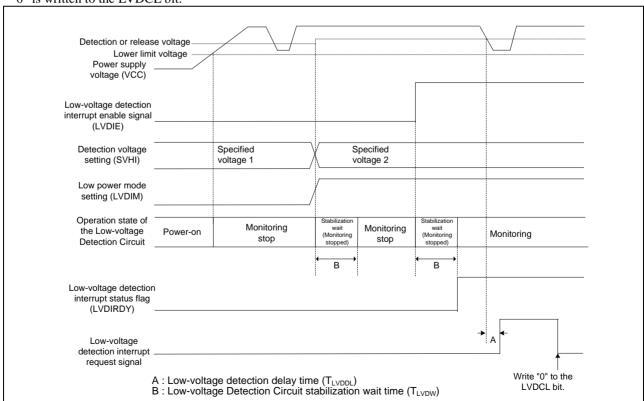

| CHAPTER 5-3: Low-voltage Detection (B)                                                |      |

| 1. Overview                                                                           | 176  |

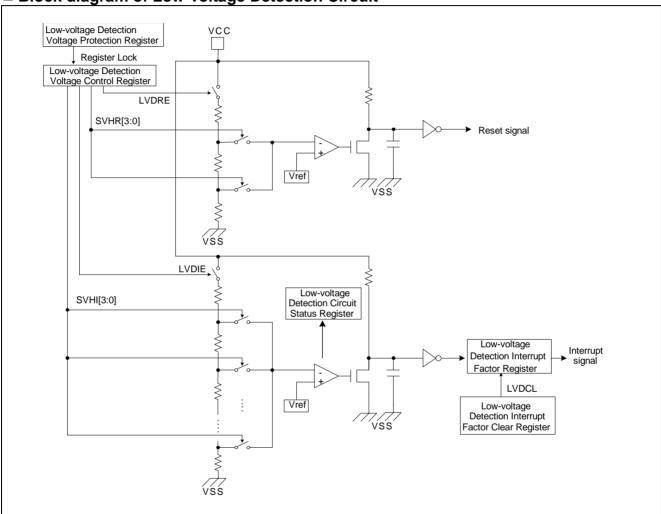

| 2. Configuration                                                                      | 177  |

| 3. Explanation of Operations                                                          | 179  |

| 4. Setup Procedure Examples                                                           | 183  |

| 5. Registers                                                                          | 185  |

| 5.1. Low-voltage Detection Voltage Control Register (LVD_CTL)                         | 186  |

| 5.2. Low-voltage Detection Interrupt Register (LVD_STR)                               | 189  |

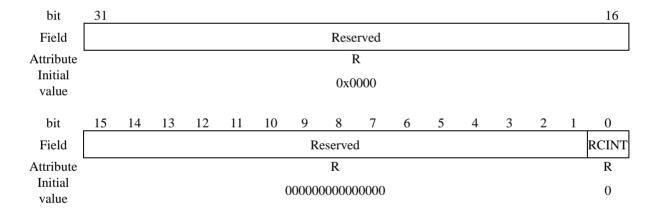

| 5.3. Low-voltage Detection Interrupt Clear Register (LVD_CLR)                         | 190  |

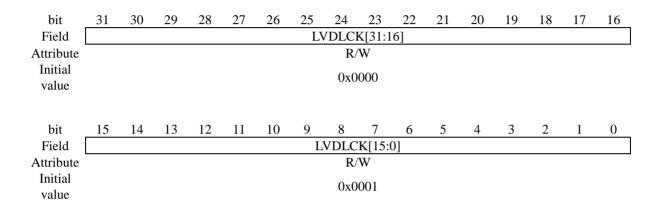

| 5.4. Low-voltage Detection Voltage Protection Register (LVD_RLR)                      | 191  |

| 5.5. Low-voltage Detection Circuit Status Register (LVD_STR2)                         | 192  |

| 6. Usage Precautions                                                                  | 193  |

| CHAPTER 5-4: Low-voltage Detection (C)                                                | 195  |

| 1. Overview                                                                           | 196  |

| 2. Configuration                                                                      | 197  |

| 3. Explanation of Operations                                                          | 199  |

| 4. Setup Procedure Examples                                                           | 202  |

| 5. Registers                                                                          | 204  |

| 5.1. Low-voltage Detection Voltage Control Register (LVD_CTL)                         | 205  |

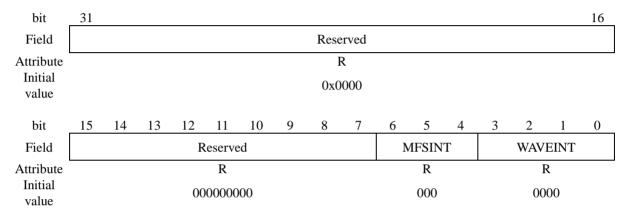

| 5.2. Low-voltage Detection Interrupt Register (LVD_STR)                               | 209  |

| 5.3. Low-voltage Detection Interrupt Clear Register (LVD_CLR)                         | 210  |

| 5.4. Low-voltage Detection Voltage Protection Register (LVD_RLR)                      |      |

| 5.5. Low-voltage Detection Circuit Status Register (LVD_STR2)                         | 212  |

| 6. Usage Precautions                                                                  | 213  |

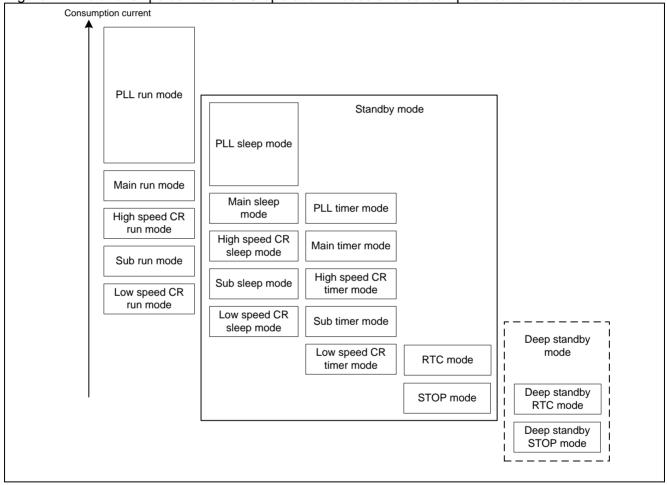

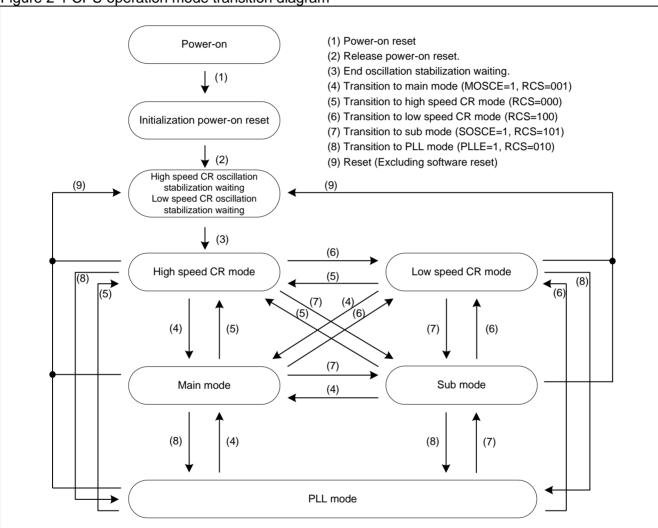

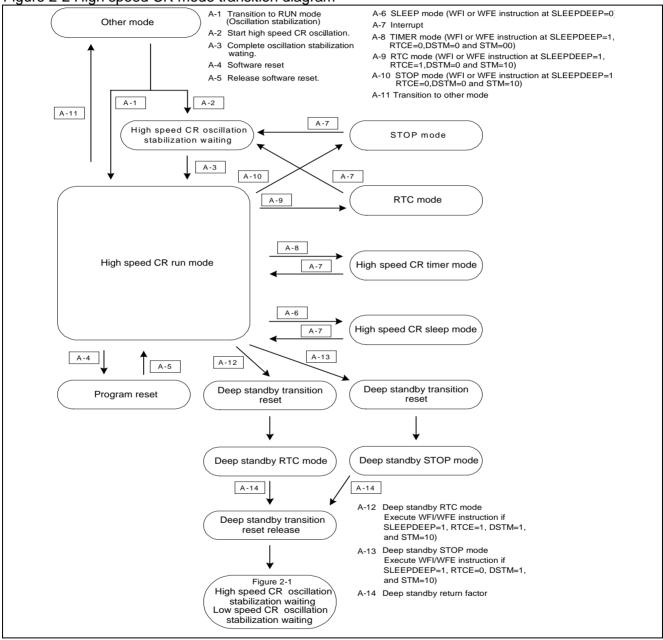

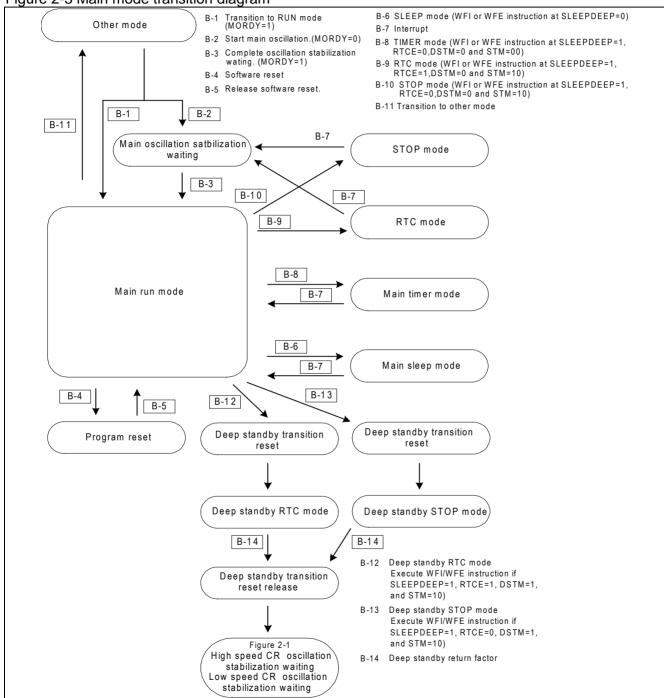

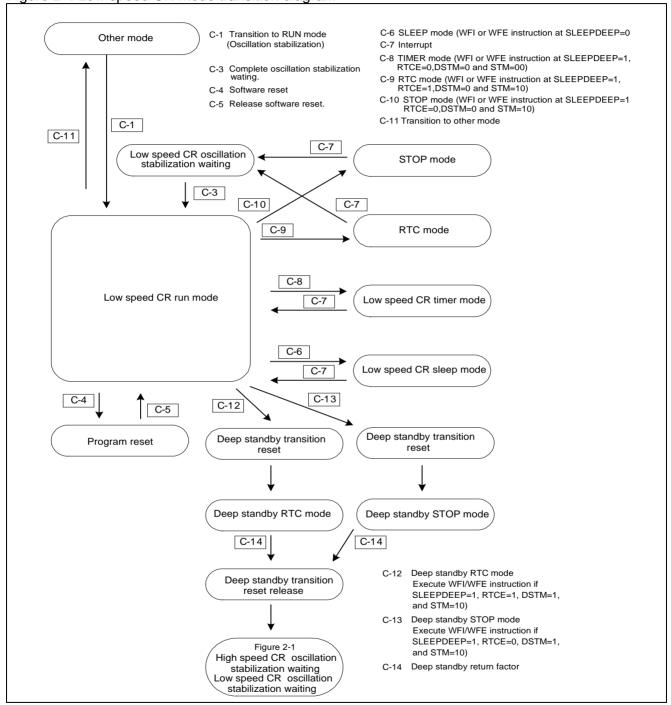

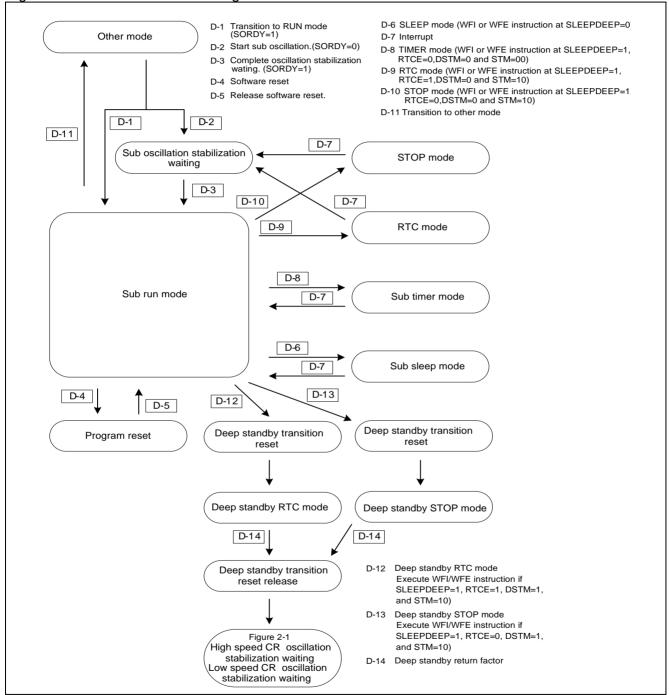

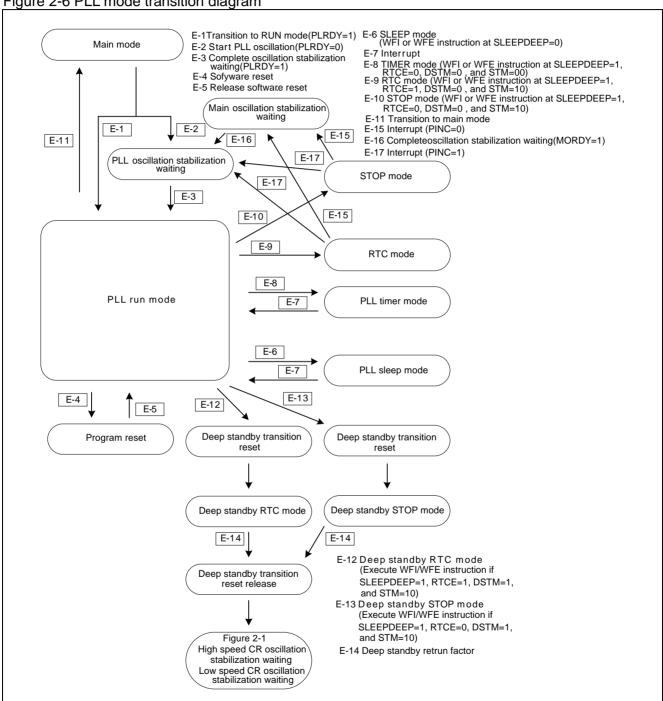

| CHAPTER 6: Low Power Consumption Mode                                                 | 215  |

| Overview of Low Power Consumption Mode                                                | 216  |

| Configuration of CPU Operation Modes                                                  | 222  |

| 3. Operations of Standby Modes                                                        |      |

| 3.1. Operations of SLEEP modes (high speed CR sleep, main sleep, PLL sleep, low spee  | d CR |

| sleep, and sub sleep modes)                                                           |      |

| 3.2. Operations of TIMER modes (high speed CR timer, main timer, PLL timer, low speed |      |

| timer, and sub timer modes)                                                           | 234  |

| 3.3. Operation of RTC Mode                                                            |      |

| 3.4. Operations of STOP mode                                                          |      |

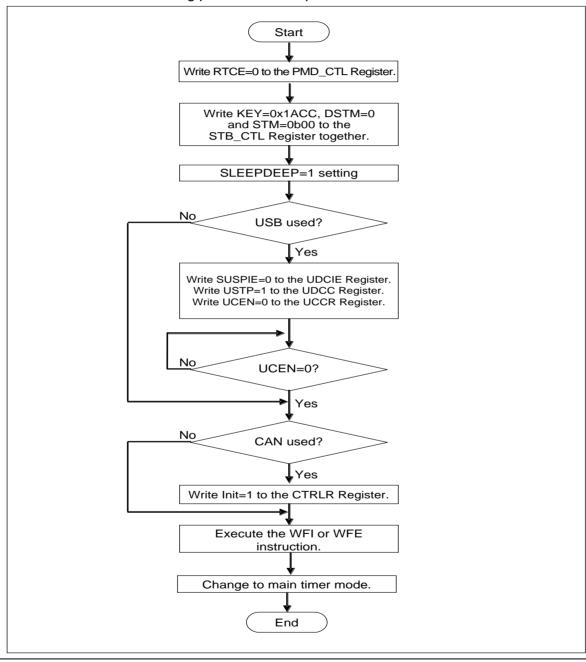

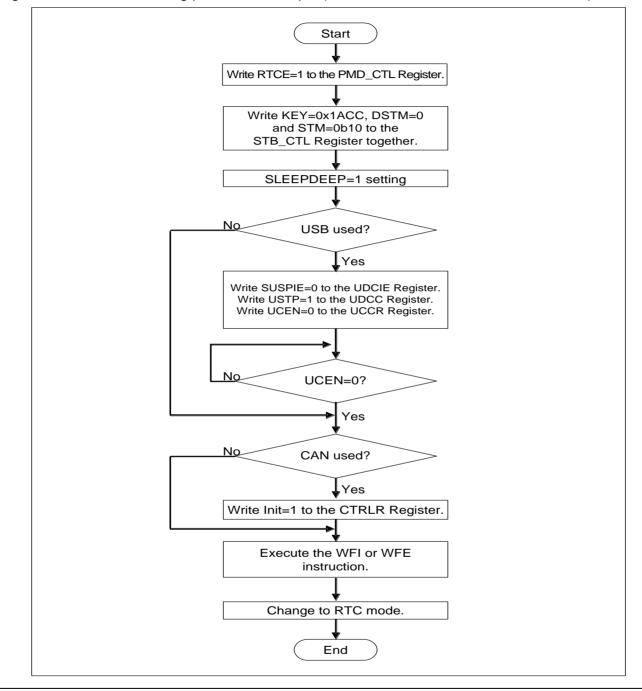

| 4. Standby Mode Setting Procedure Examples                                            |      |

| 5. Description of Deep Standby Mode Operation                                         |      |

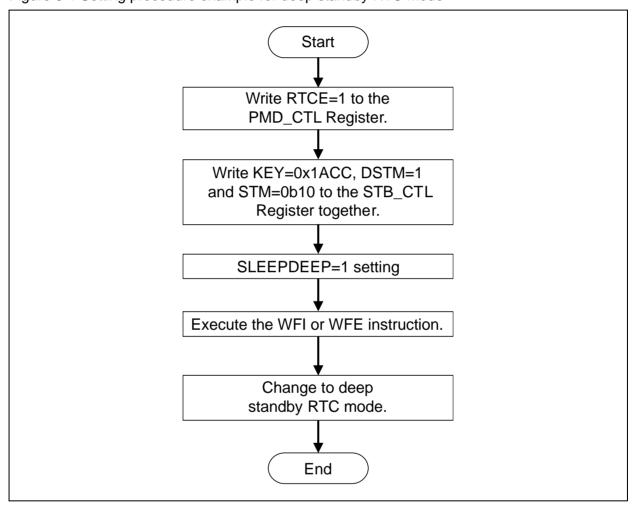

| 5.1. Operation of Deep Standby RTC Mode                                               |      |

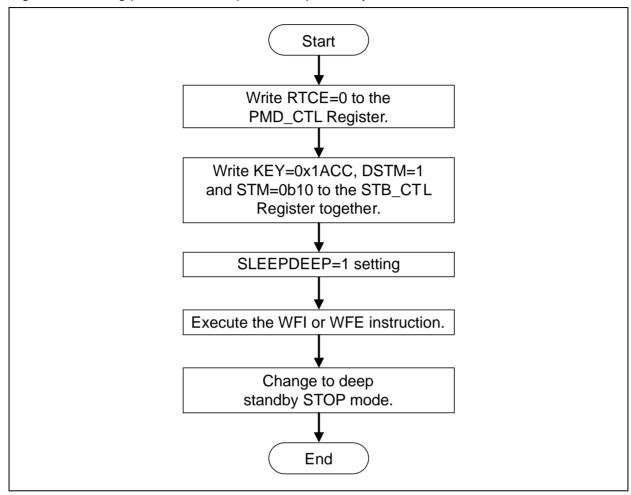

| 5.2. Operation of Deep Standby Stop Mode                                              |      |

| Deep Standby Mode Setting Procedure Examples                                          |      |

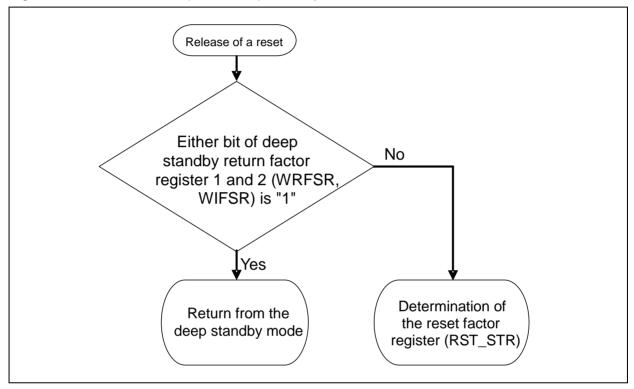

| 7. Deep Standby Return Factor Determination Procedure                                 | 253  |

| List of Low Power Consumption Mode Registers                         |     |

|----------------------------------------------------------------------|-----|

| 8.1. Standby Mode Control Register (STB_CTL)                         | 255 |

| 8.2. Sub Oscillation Circuit Power Supply Control Register (REG_CTL) | 257 |

| 8.3. Sub Clock Control Register (RCK_CTL)                            | 258 |

| 8.4. RTC Mode Control Register (PMD_CTL)                             |     |

| 8.5. Deep Standby Return Factor Register 1 (WRFSR)                   |     |

| 8.6. Deep Standby Return Factor Register 2 (WIFSR)                   |     |

| 8.7. Deep Standby Return Enable Register (WIER)                      | 263 |

| 8.8. WKUP Pin Input Level Register (WILVR)                           | 265 |

| 8.9. Deep Standby RAM Retention Register (DSRAMR)                    | 266 |

| 8.10. Backup Registers from 01 to 16 (BUR01 to 16)                   | 267 |

| 9. Usage Precautions                                                 | 268 |

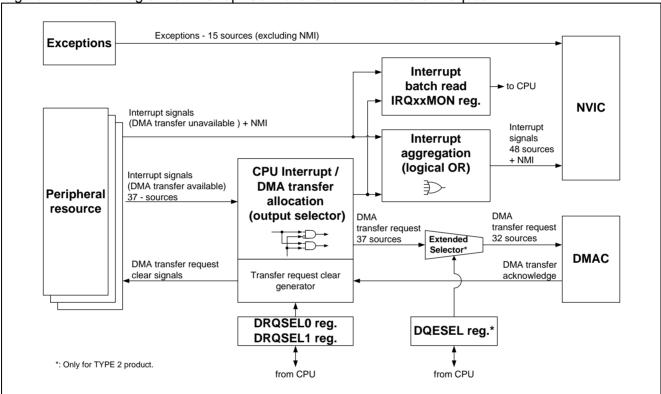

| CHAPTER7-1: Configuration of interrupts                              | 269 |

| 1. Configuration                                                     | 270 |

| CHAPTER 7-2: Interrupts (A)                                          |     |

| 1. Overview                                                          | 276 |

| 2. Configuration                                                     | 277 |

| 3. Exception and Interrupt Factor Vectors                            | 278 |

| 4. Registers                                                         | 281 |

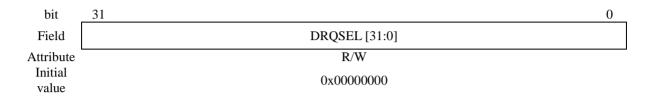

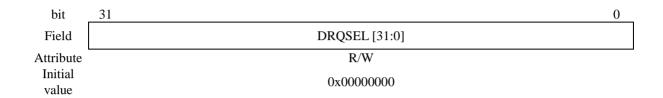

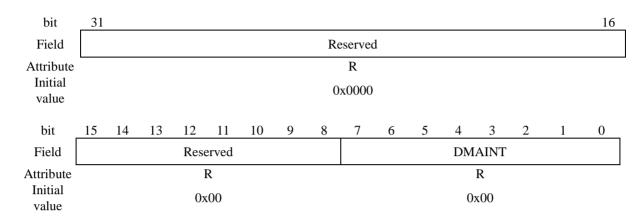

| 4.1. DMA Request Selection Register (DRQSEL0)                        | 283 |

| 4.2. DMA Request Select Register 1 (DRQSEL1)                         | 287 |

| 4.3. DMA Request Extended Selection Register (DQESEL)                | 288 |

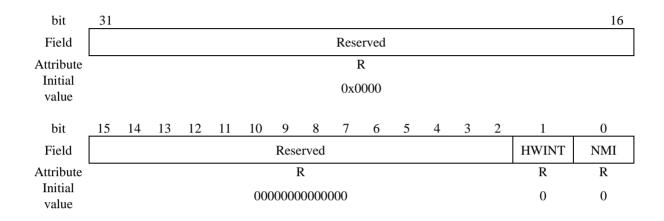

| 4.4. EXC02 Batch Read Register (EXC02MON)                            | 291 |

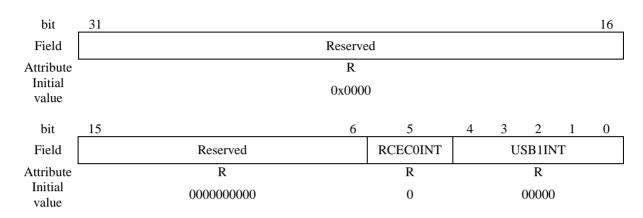

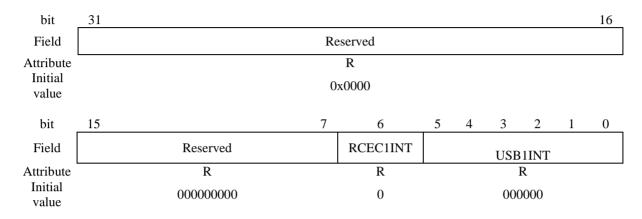

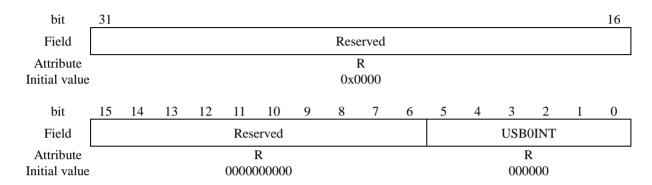

| 4.5. IRQ00 Batch Read Register (IRQ00MON)                            | 292 |

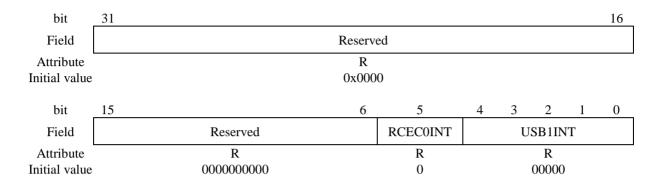

| 4.6. IRQ01 Batch Read Register (IRQ01MON)                            | 293 |

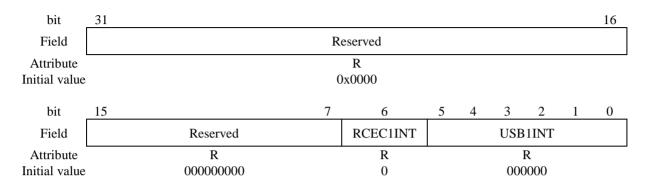

| 4.7. IRQ02 Batch Read Register (IRQ02MON)                            | 294 |

| 4.8. IRQ03 Batch Read Register (IRQ03MON)                            | 295 |

| 4.9. IRQ04 Batch Read Register (IRQ04MON)                            | 297 |

| 4.10. IRQ05 Batch Read Register (IRQ05MON)                           | 298 |

| 4.11. IRQ06 Batch Read Register (IRQ06MON)                           |     |

| 4.12. IRQ07/09/11/13/15/17/19/21 Batch Read Register (IRQxxMON)      | 302 |

| 4.13. IRQ08/10/12/14/16/18/20/22 Batch Read Register (IRQxxMON)      | 303 |

| 4.14. IRQ23 Batch Read Register (IRQ23MON)                           | 304 |

| 4.15. IRQ24 Batch Read Register (IRQ24MON)                           |     |

| 4.16. IRQ25/26 Batch Read Register (IRQxxMON)                        |     |

| 4.17. IRQ27 Batch Read Register (IRQ27MON)                           |     |

| 4.18. IRQ28 Batch Read Register (IRQ28MON)                           | 309 |

| 4.19. IRQ29 Batch Read Register (IRQ29MON)                           | 311 |

| 4.20. IRQ30 Batch Read Register (IRQ30MON)                           |     |

| 4.21. IRQ31 Batch Read Register (IRQ31MON)                           | 315 |

| 4.22. IRQ32 Batch Read Register (IRQ32MON)                           |     |

| 4.23. IRQ33 Batch Read Register (IRQ33MON)                           | 318 |

| 4.24. IRQ34 Batch Read Register (IRQ34MON)                           |     |

| 4.25. IRQ35 Batch Read Register (IRQ35MON)                           |     |

| 4.26. IRQ36 Batch Read Register (IRQ36MON)                           |     |

| 4.27. IRQ37 Batch Read Register (IRQ37MON)                           |     |

| 4.28. IRQ38/39/40/41/42/43/44/45 Batch Read Register (IRQxxMON)      |     |

| 4.29. IRQ46 Batch Read Register (IRQ46MON)                           |     |

| 4.30. IRQ47 Batch Read Register (IRQ47MON)                           |     |

| 4.31. USB ch.0 Odd Packet Size DMA Enable Register (ODDPKS)          |     |

| 4.32. USB ch.1 Odd Packet Size DMA Enable Register (ODDPKS1)         |     |

| 5. Usage Precautions                                                 | 331 |

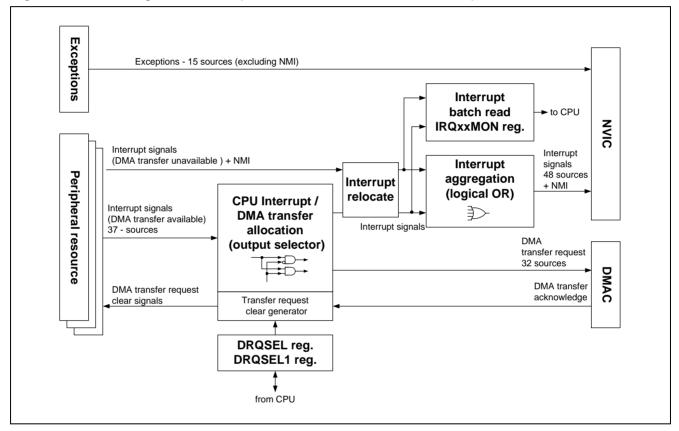

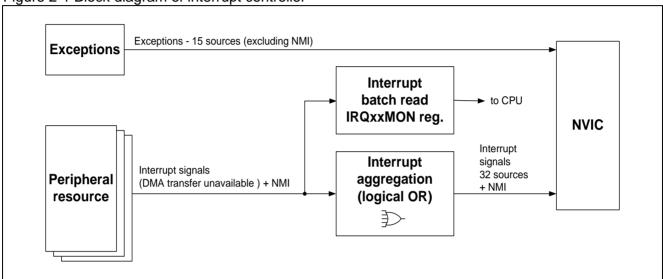

| CHAPTER 7-3: CHAPTER: Interrupts (B)                                | 333 |

|---------------------------------------------------------------------|-----|

| 1. Overview                                                         |     |

| 2. Configuration                                                    | 335 |

| 3. Exception and Interrupt Factor Vectors                           | 336 |

| 4. Registers                                                        |     |

| 4.1. DMA Request Selection Register (DRQSEL)                        | 341 |

| 4.2. EXC02 Batch Read Register (EXC02MON)                           | 344 |

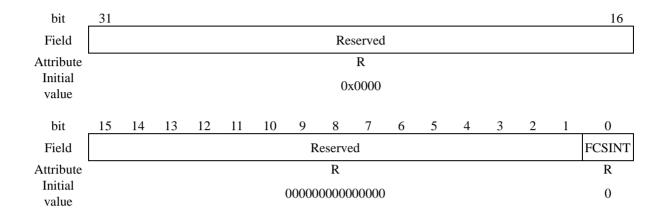

| 4.3. IRQ00 Batch Read Register (IRQ00MON)                           | 345 |

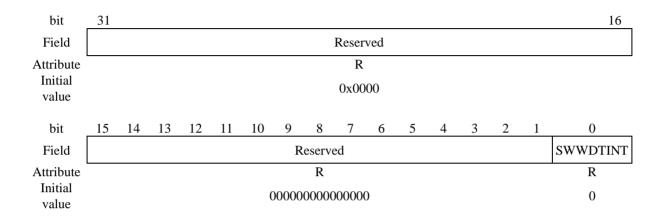

| 4.4. IRQ01 Batch Read Register (IRQ01MON)                           | 346 |

| 4.5. IRQ02 Batch Read Register (IRQ02MON)                           | 347 |

| 4.6. IRQ03 to IRQ10 Batch Read Register (IRQ03MON to IRQ10MON)      | 348 |

| 4.7. IRQ11/39/40 Batch Read Register (IRQxxMON)                     | 349 |

| 4.8. IRQ12 Batch Read Register (IRQ12MON)                           | 350 |

| 4.9. IRQ13 Batch Read Register (IRQ13MON)                           | 351 |

| 4.10. IRQ014 Batch Read Register (IRQ14MON)                         | 353 |

| 4.11. IRQ15/16/17/18 Batch Read Register (IRQxxMON)                 | 354 |

| 4.12. IRQ19/21/42/44 Batch Read Register (IRQxxMON)                 | 355 |

| 4.13. IRQ20/22/43/45 Batch Read Register (IRQxxMON)                 | 356 |

| 4.14. IRQ23 Batch Read Register (IRQ23MON)                          | 357 |

| 4.15. IRQ24 Batch Read Register (IRQ24MON)                          | 358 |

| 4.16. IRQ25/26 Batch Read Register (IRQxxMON)                       |     |

| 4.17. IRQ27 Batch Read Register (IRQ27MON)                          | 362 |

| 4.18. IRQ28/29/30 Batch Read Register (IRQxxMON)                    | 364 |

| 4.19. IRQ31 Batch Read Register (IRQ31MON)                          | 366 |

| 4.20. IRQ32 Batch Read Register (IRQ32MON)                          | 368 |

| 4.21. IRQ33 Batch Read Register (IRQ33MON)                          | 370 |

| 4.22. IRQ34 Batch Read Register (IRQ34MON)                          |     |

| 4.23. IRQ35 Batch Read Register (IRQ35MON)                          | 372 |

| 4.24. IRQ36 Batch Read Register (IRQ36MON)                          | 373 |

| 4.25. IRQ37 Batch Read Register (IRQ37MON)                          |     |

| 4.26. IRQ38 Batch Read Register (IRQ38MON)                          |     |

| 4.27. IRQ41 Batch Read Register (IRQ41MON)                          |     |

| 4.28. IRQ46 Batch Read Register (IRQ46MON)                          | 377 |

| 4.29. IRQ47 Batch Read Register (IRQ47MON)                          |     |

| 4.30. USB ch.0 Odd Packet Size DMA Enable Register (ODDPKS)         |     |

| 4.31. Interrupt Factor Vector Relocate Setting Register (IRQCMODER) |     |

| 4.32. Interrupt Factor Selection Register0 (RCINTSEL0)              |     |

| 4.33. Interrupt Factor Selection Register1 (RCINTSEL1)              |     |

| 5. Usage Precautions                                                |     |

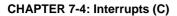

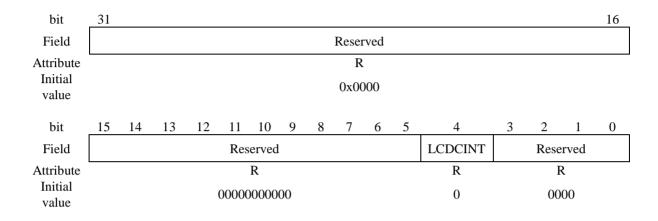

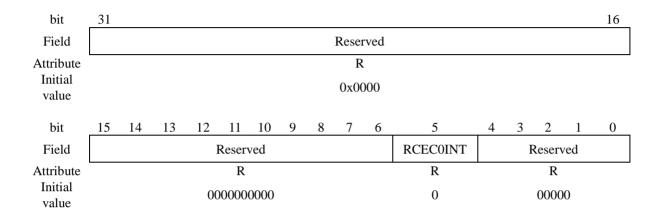

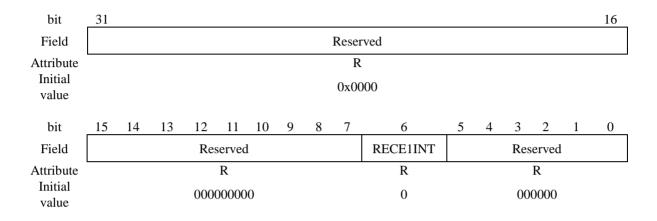

| CHAPTER 7-4: Interrupts (C)                                         |     |

| 1. Overview                                                         |     |

| 2. Configuration                                                    |     |

| 3. Exception and Interrupt Factor Vector                            | 392 |

| 4. Registers                                                           | 394 |

|------------------------------------------------------------------------|-----|

| 4.1. EXC02 Batch Read Register (EXC02MON)                              | 396 |

| 4.2. IRQ00 Batch Read Register (IRQ00MON)                              | 397 |

| 4.3. IRQ01 Batch Read Register (IRQ01MON)                              | 398 |

| 4.4. IRQ02 Batch Read Register (IRQ02MON)                              | 399 |

| 4.5. IRQ03 Batch Read Register (IRQ03MON)                              | 400 |

| 4.6. IRQ04 Batch Read Register (IRQ04MON)                              |     |

| 4.7. IRQ05 Batch Read Register (IRQ05MON)                              |     |

| 4.8. IRQ06/08/10/12/14/16/18/20 Batch Read Register (IRQxxMON)         |     |

| 4.9. IRQ07/09/11/13/15/17/19/21 Batch Read Register (IRQxxMON)         |     |

| 4.10. IRQ22 Batch Read Register (IRQ22MON)                             |     |

| 4.11. IRQ23 Batch Read Register (IRQ23MON)                             |     |

| 4.12. IRQ24 Batch Read Register (IRQ24MON)                             |     |

| 4.13. IRQ25 Batch Read Register (IRQ25MON)                             |     |

| 4.14. IRQ26 Batch Read Register (IRQ26MON)                             |     |

| 4.15. IRQ27 Batch Read Register (IRQ27MON)                             |     |

| 4.16. IRQ28 Batch Read Register (IRQ28MON)                             |     |

| 4.17. IRQ29 Batch Read Register (IRQ29MON)                             |     |

| 4.18. IRQ30 Batch Read Register (IRQ30MON)                             |     |

| 4.19. IRQ31 Batch Read Register (IRQ31MON)                             |     |

| 5. Usage Precautions                                                   |     |

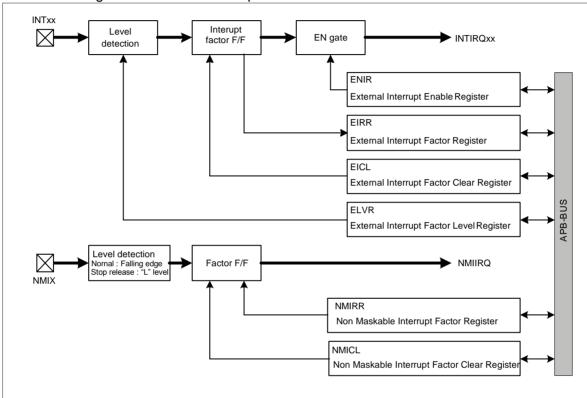

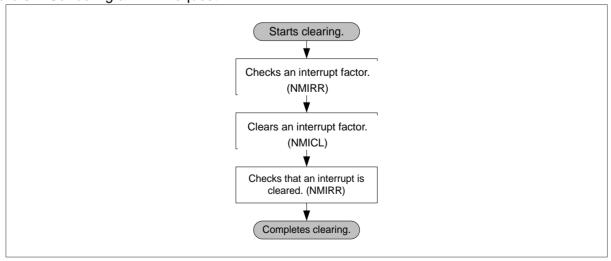

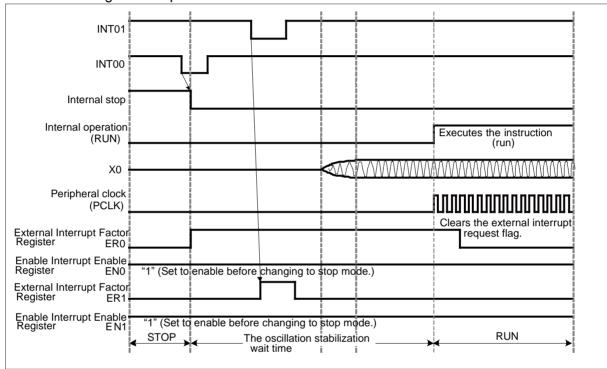

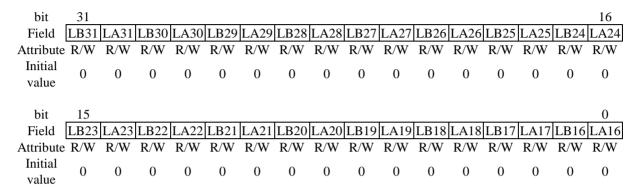

| CHAPTER 8: External Interrupt and NMI Control Sections                 |     |

| 1. Overview                                                            |     |

| 2. Block Diagram                                                       |     |

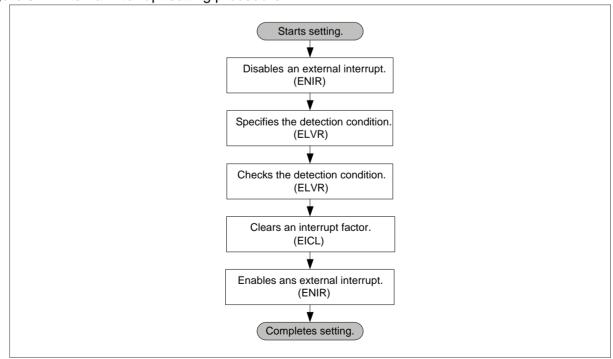

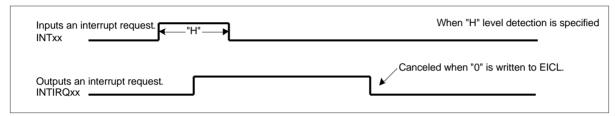

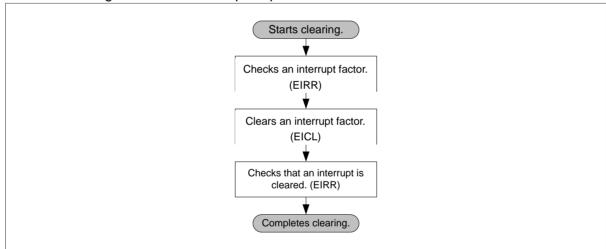

| Operations and Setting Procedure Examples                              |     |

| 3.1. Operations of External Interrupt Control Section                  |     |

| 3.2. Operations of NMI Control Section                                 |     |

| 3.3. Returning from Timer or Stop Mode                                 |     |

| 4. Registers                                                           |     |

| 4.1. External Interrupt Enable Register (ENIR)                         |     |

| 4.2. External Interrupt Factor Register (EIRR)                         |     |

| 4.3. External Interrupt Factor Clear Register (EICL)                   |     |

| 4.4. External Interrupt Factor Level Register (ELVR)                   |     |

| 4.5. External Interrupt Factor Level Register 1 (ELVR1)                | 431 |

| 4.6. Non Maskable Interrupt Factor Register (NMIRR)                    | 432 |

| 4.7. Non Maskable Interrupt Factor Clear Register (NMICL)              | 433 |

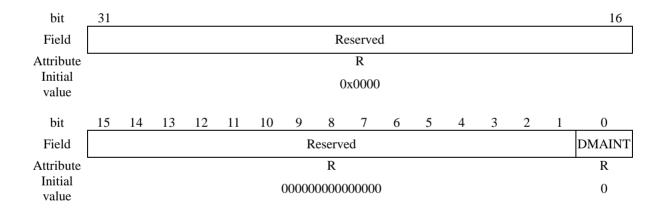

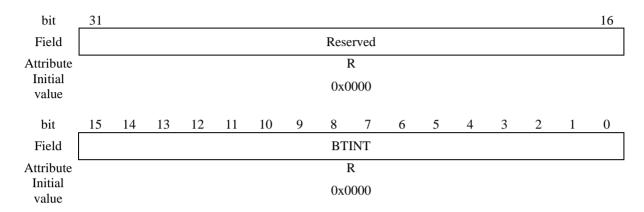

| CHAPTER 9: DMAC                                                        | 435 |

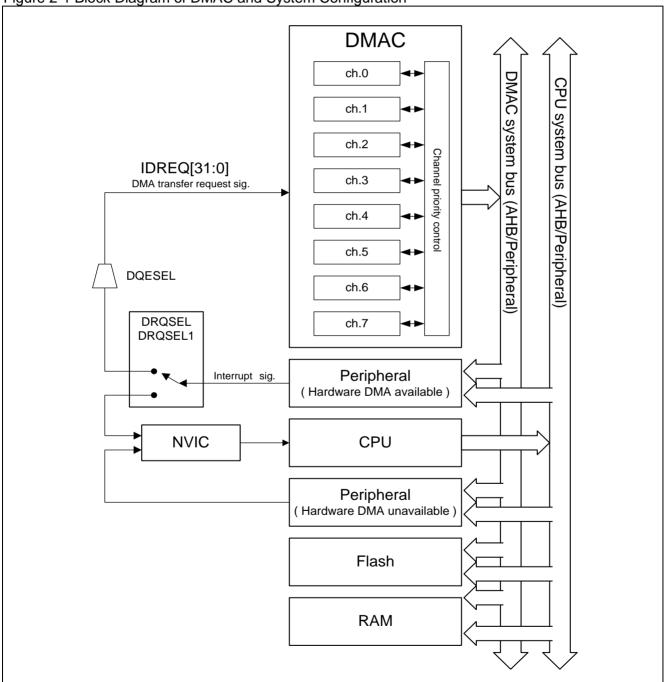

| 1. Overview of DMAC                                                    | 436 |

| 2. Configuration of DMAC                                               | 437 |

| 2.1. DMAC and System Configuration                                     | 438 |

| 2.2. I/O Signals of DMAC                                               | 440 |

| 3. Functions and Operations of DMAC                                    | 443 |

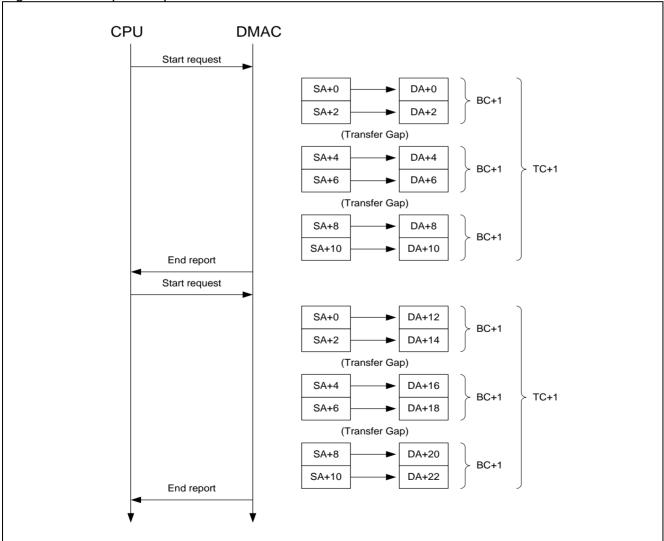

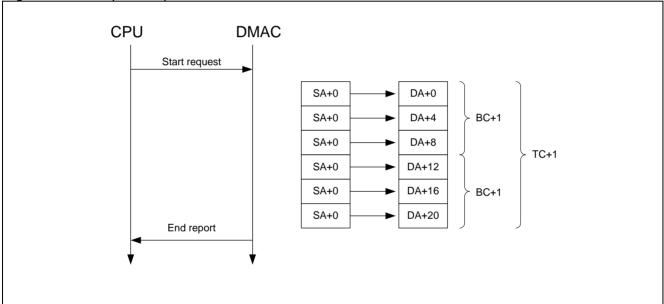

| 3.1. Software-Block Transfer                                           | 444 |

| 3.2. Software-Burst Transfer                                           |     |

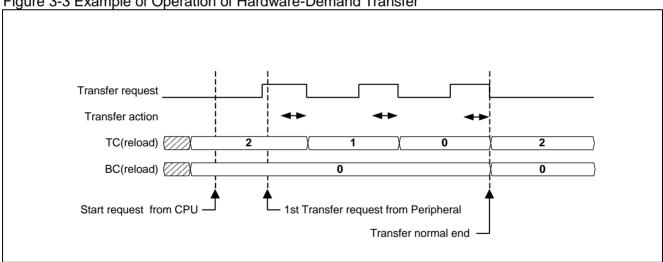

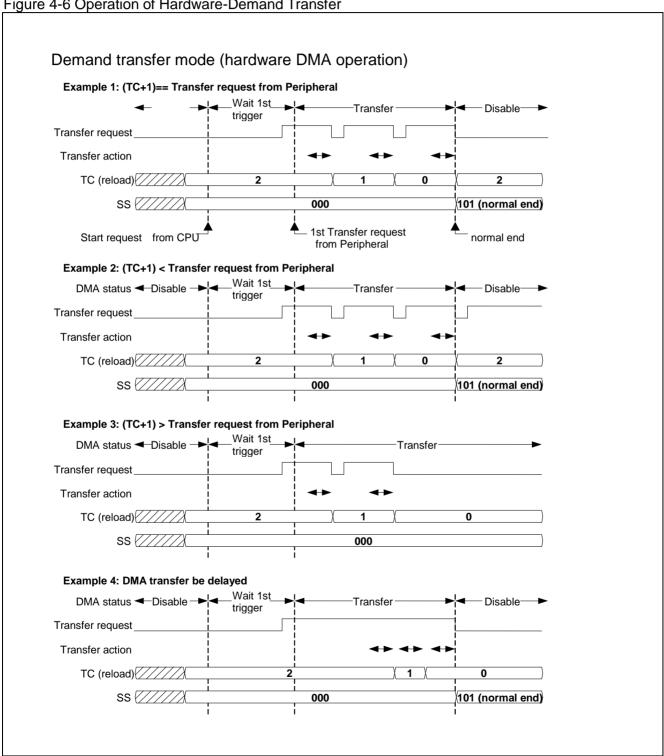

| 3.3. Hardware-Demand Transfer                                          |     |

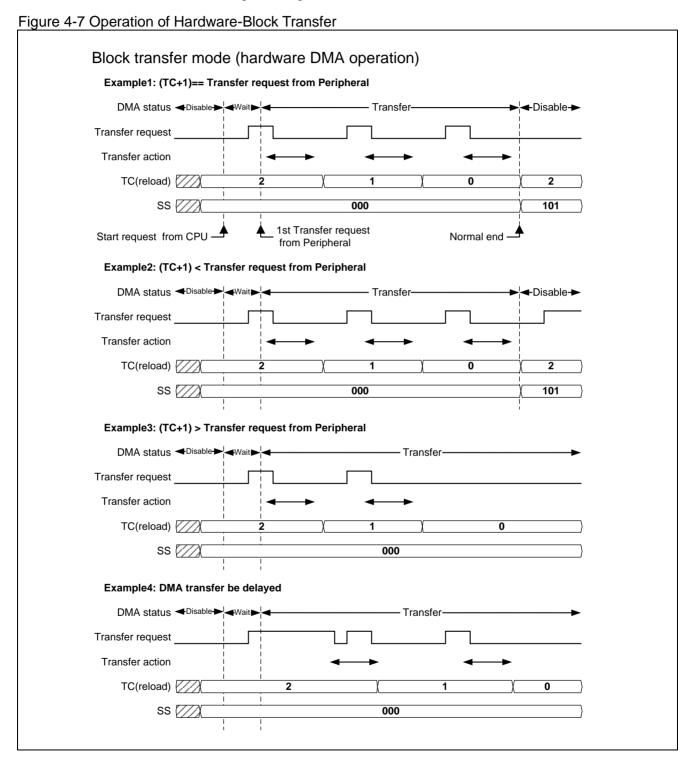

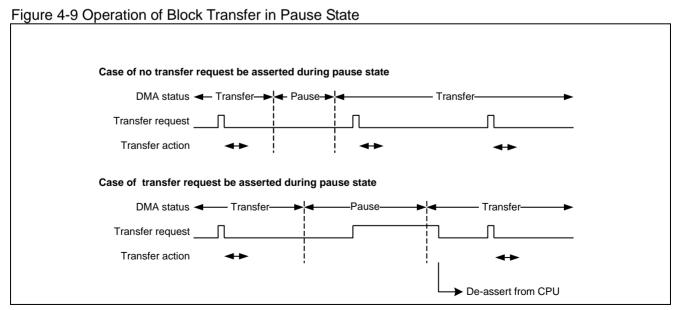

| 3.4. Hardware-Block Transfer & Burst Transfer                          | 448 |

| 3.5. Channel Priority Control                                          | 450 |

| 4. DMAC Control                                                        | 451 |

| 4.1. Overview of DMAC Control                                          |     |

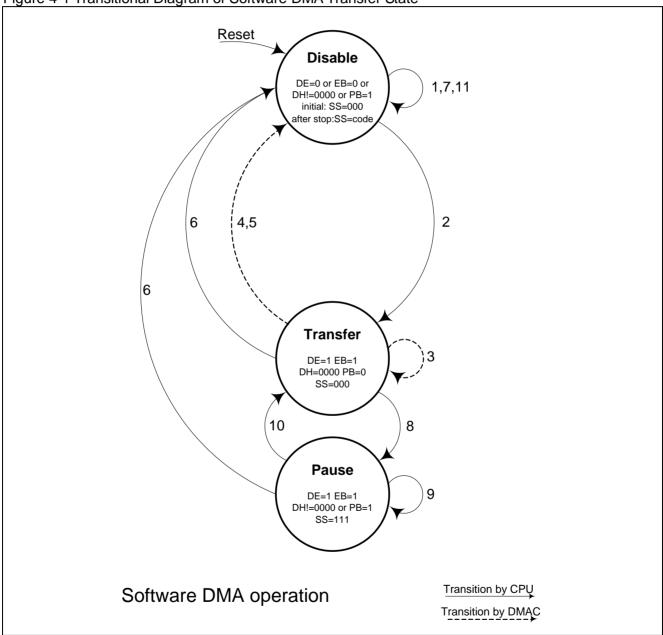

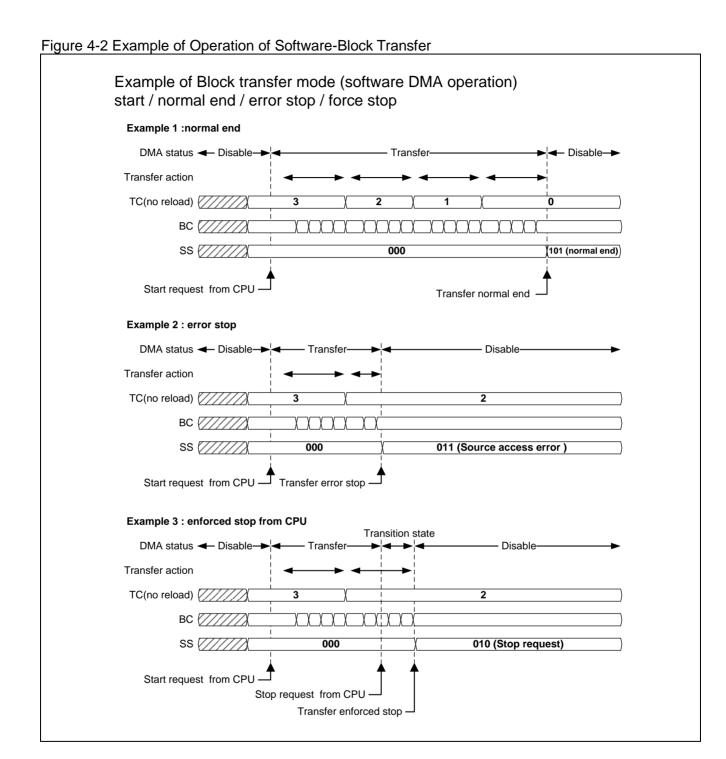

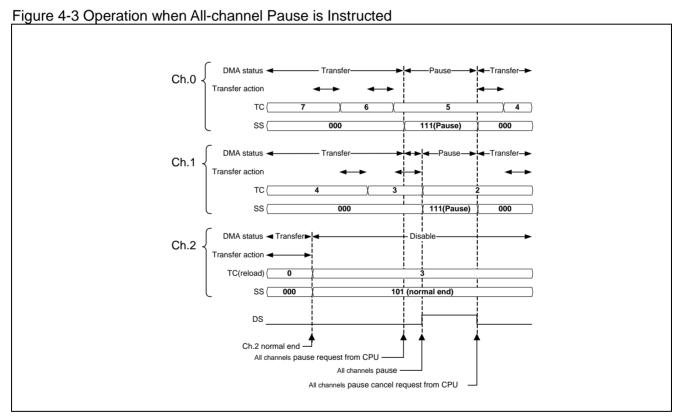

| 4.2. DMAC Operation and Control Procedure for Software Transfer        | 453 |

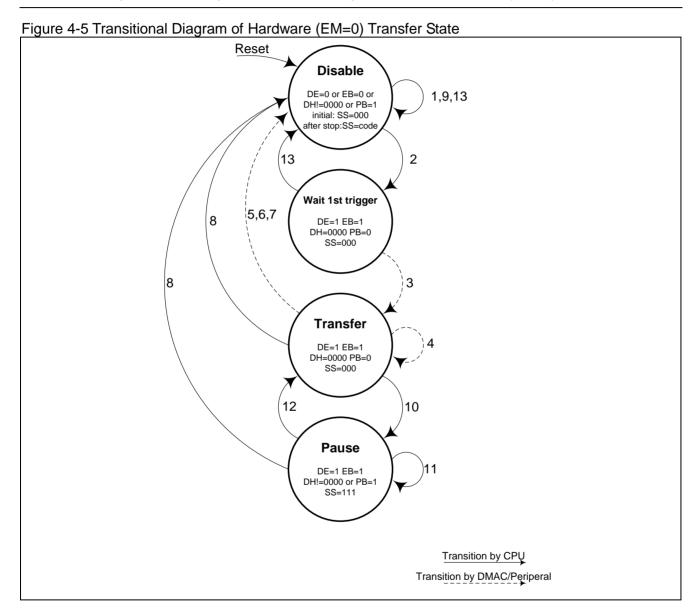

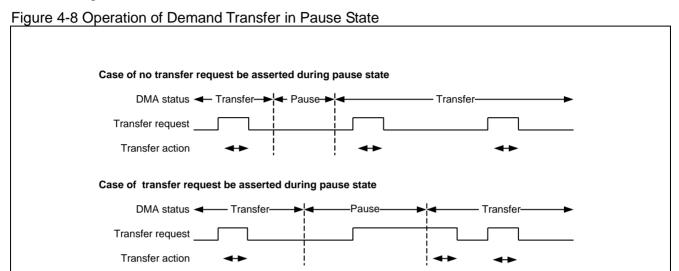

| 4.3. DMAC Operation and Control Procedure for Hardware (EM=0) Transfer | 460 |

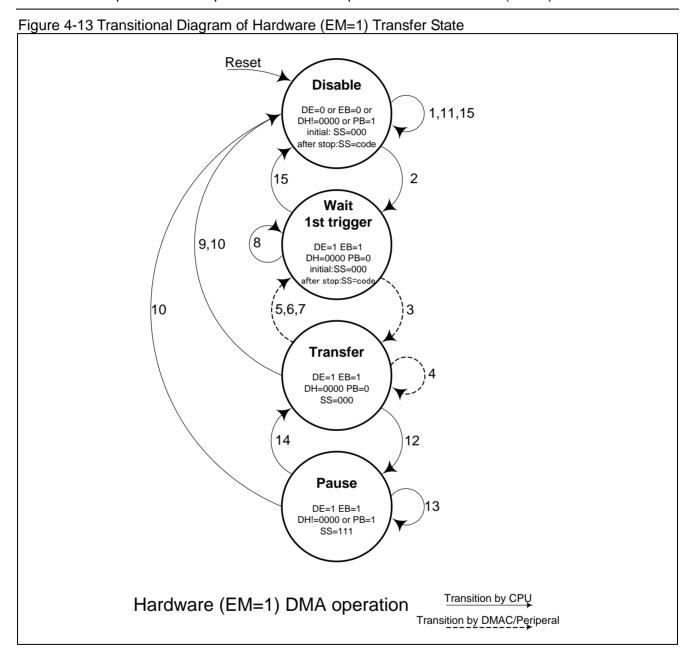

| 4.4. DMAC Operation and Control Procedure for Hardware (EM=1) Transfer | 469 |

|     | 5. Registers of DMAC                                      | 473 |

|-----|-----------------------------------------------------------|-----|

|     | 5.1. List of Registers                                    | 474 |

|     | 5.2. Entire DMAC Configuration Register (DMACR)           | 475 |

|     | 5.3. Configuration A Register (DMACA)                     |     |

|     | 5.4. Configuration B Register (DMACB)                     | 480 |

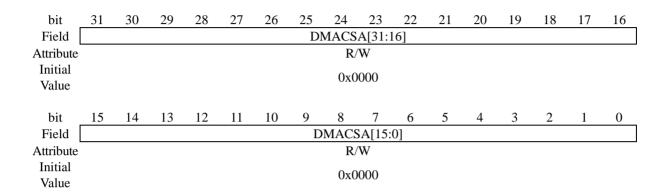

|     | 5.5. Transfer Source Address Register (DMACSA)            | 484 |

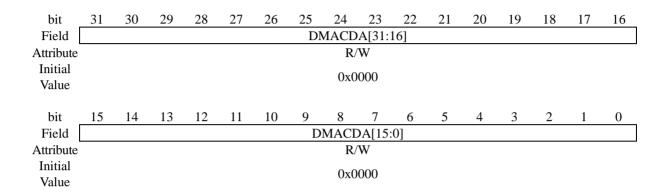

|     | 5.6. Transfer Destination Address Register (DMACDA)       |     |

|     | 6. Usage Precautions                                      | 486 |

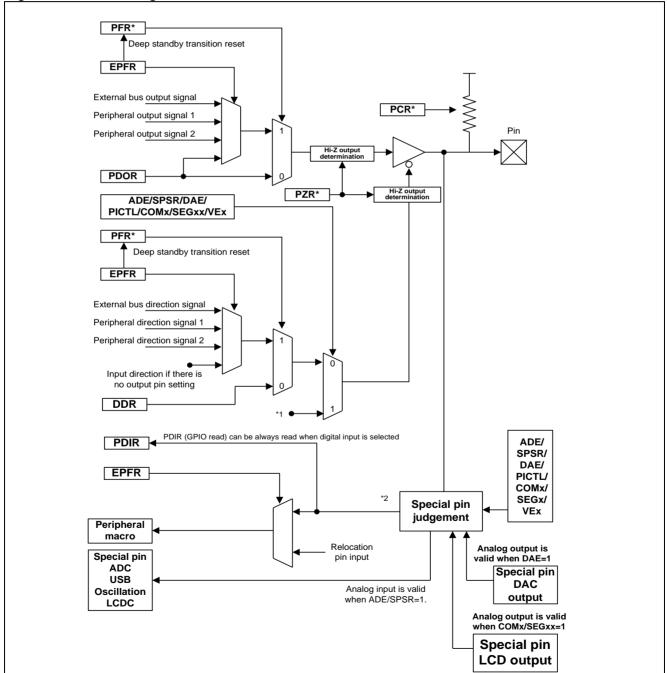

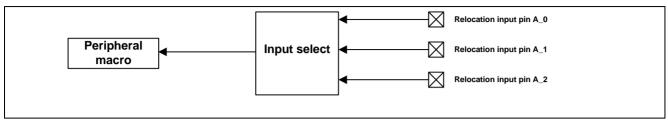

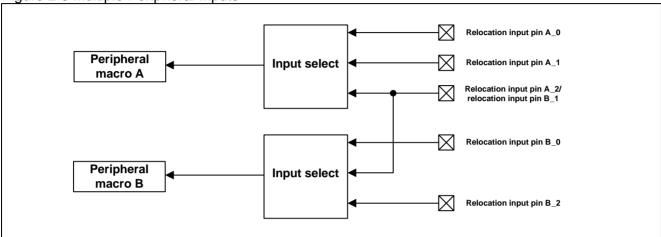

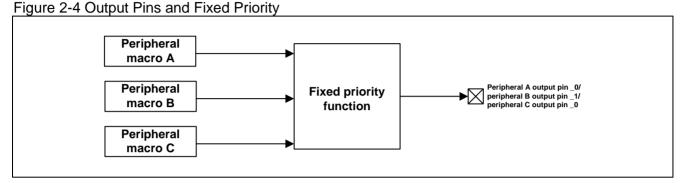

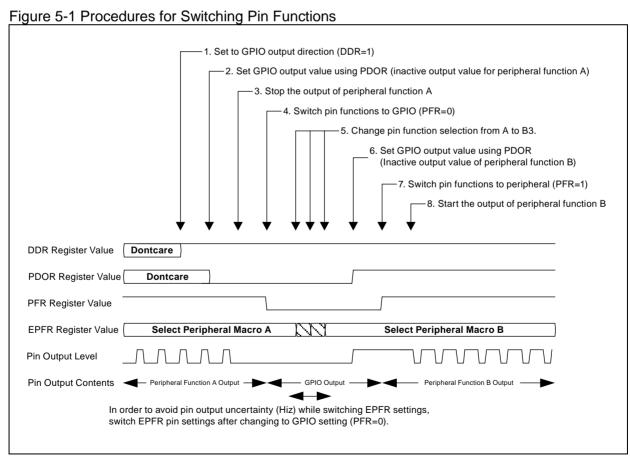

| СНА | PTER 10: I/O PORT                                         | 487 |

|     | 1. Overview                                               | 488 |

|     | 2. Configuration, Block Diagram, and Operation            | 489 |

|     | 3. Setup Procedure Example                                | 498 |

|     | 4. Register List                                          | 499 |

|     | 4.1. Port Function Setting Register (PFRx)                | 503 |

|     | 4.2. Pull-up Setting Register (PCRx)                      | 504 |

|     | 4.3. Port input/output Direction Setting Register (DDRx)  | 506 |

|     | 4.4. Port Input Data Register (PDIRx)                     | 508 |

|     | 4.5. Port Output Data Register x (PDORx)                  |     |

|     | 4.6. Analog Input Setting Register (ADE)                  | 512 |

|     | 4.7. Extended Pin Function Setting Register (EPFRx)       | 513 |

|     | 4.8. Extended Pin Function Setting Register 00 (EPFR00)   | 516 |

|     | 4.9. Extended Pin Function Setting Register 01 (EPFR01)   |     |

|     | 4.10. Extended Pin Function Setting Register 02 (EPFR02)  | 523 |

|     | 4.11. Extension Function Pin Setting Register 03 (EPFR03) |     |

|     | 4.12. Extended Pin Function Setting Register 04 (EPFR04)  | 531 |

|     | 4.13. Extended Pin Function Setting Register 05 (EPFR05)  | 535 |

|     | 4.14. Extended Pin Function Setting Register 06 (EPFR06)  | 539 |

|     | 4.15. Extended Pin Function Setting Register 07 (EPFR07)  | 543 |

|     | 4.16. Extended Pin Function Setting Register 08 (EPFR08)  | 547 |

|     | 4.17. Extended Pin Function Setting Register 09 (EPFR09)  | 552 |

|     | 4.18. Extended Pin Function Setting Register 10 (EPFR10)  | 556 |

|     | 4.19. Extended Pin Function Setting Register 11 (EPFR11)  | 563 |

|     | 4.20. Extended Pin Function Setting Register 12 (EPFR12)  |     |

|     | 4.21. Extended Pin Function Setting Register 13 (EPFR13)  |     |

|     | 4.22. Extended Pin Function Setting Register 14 (EPFR14)  | 577 |

|     | 4.23. Extended Pin Function Setting Register 15 (EPFR15)  | 581 |

|     | 4.24. Extended Pin Function Setting Register 13 (EPFR16)  | 585 |

|     | 4.25. Extended Pin Function Setting Register 14 (EPFR17)  |     |

|     | 4.26. Extended Pin Function Setting Register 15 (EPFR18)  |     |

|     | 4.27. Special Port Setting Register (SPSR)                |     |

|     | 4.28. Port Pseudo Open Drain Setting Register (PZRx)      | 599 |

|     | 5. Usage Precautions                                      | 601 |

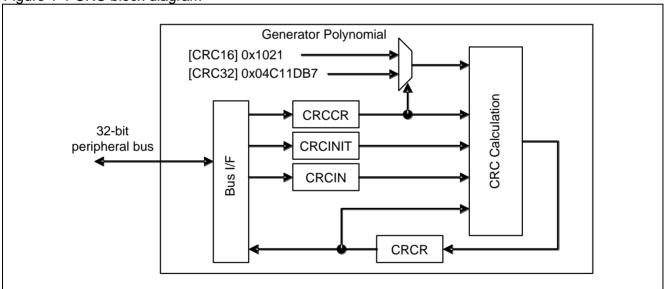

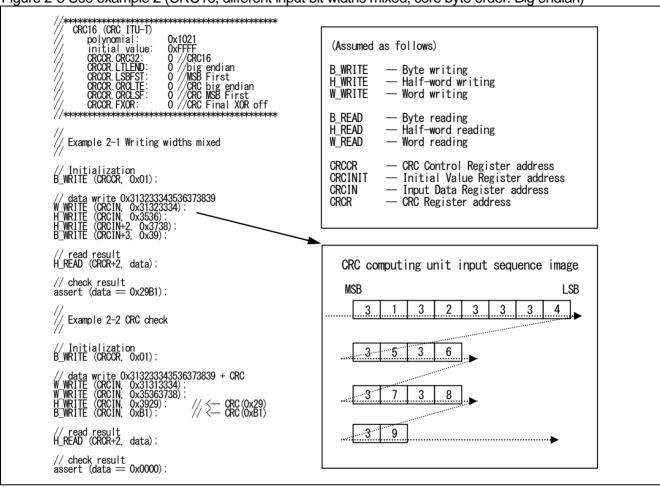

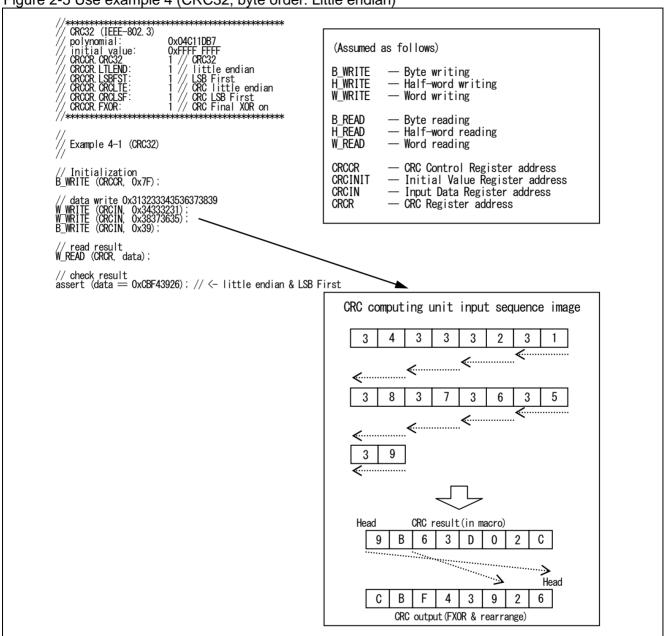

| CHAPTER 11: CRC (Cyclic Redundancy Check)                   | 603 |

|-------------------------------------------------------------|-----|

| 1. Overview of CRC                                          | 604 |

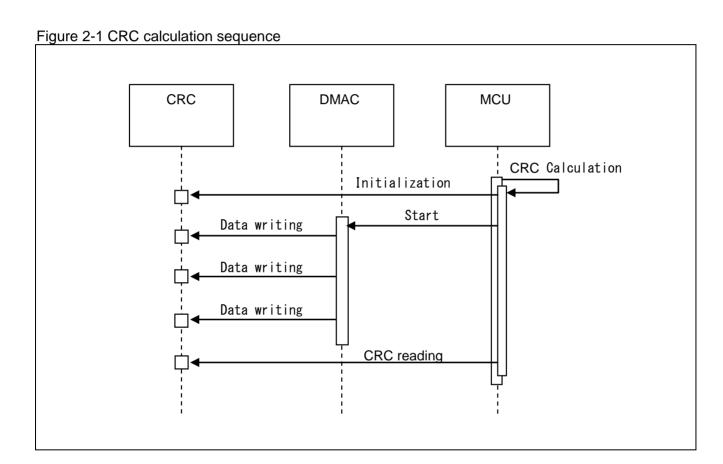

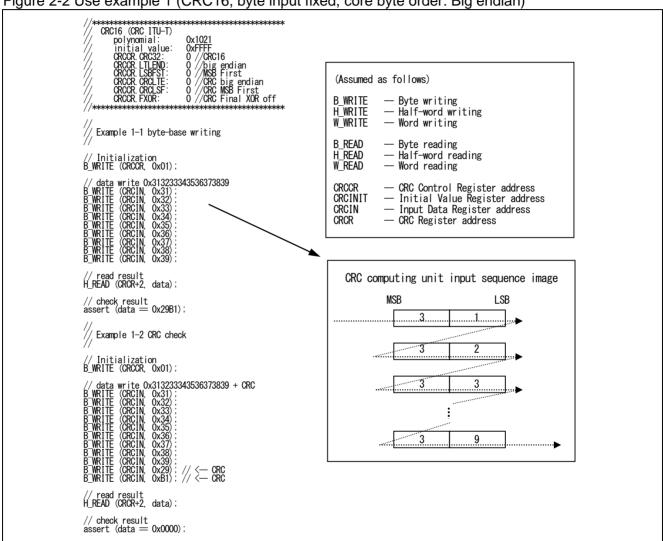

| 2. CRC Operations                                           | 605 |

| 2.1. CRC calculation sequence                               | 606 |

| 2.2. CRC use examples                                       | 607 |

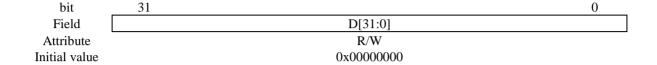

| 3. CRC Registers                                            | 611 |

| 3.1. CRC Control Register (CRCCR)                           | 612 |

| 3.2. Initial Value Register (CRCINIT)                       | 614 |

| 3.3. Input Data Register (CRCIN)                            | 615 |

| 3.4. CRC Register (CRCR)                                    | 616 |

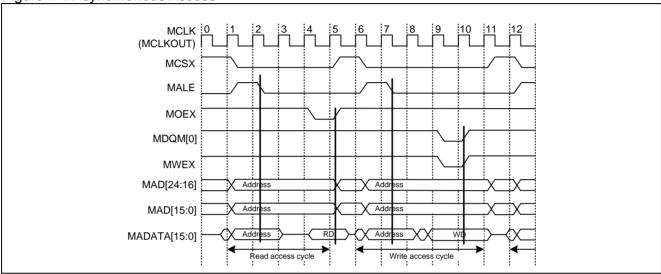

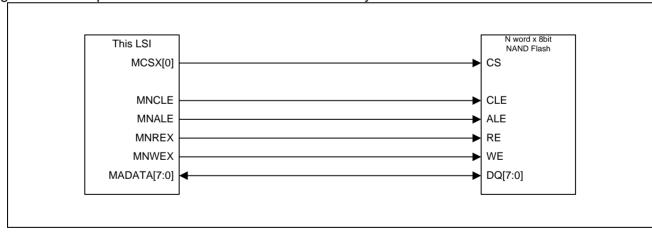

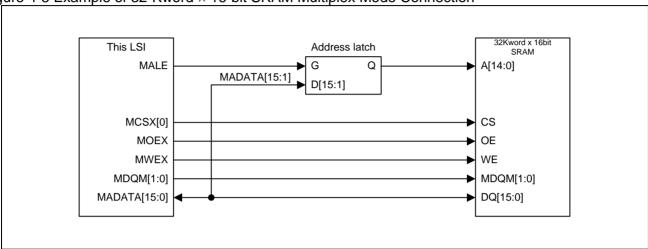

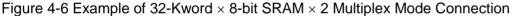

| CHAPTER12: External Bus Interface                           | 617 |

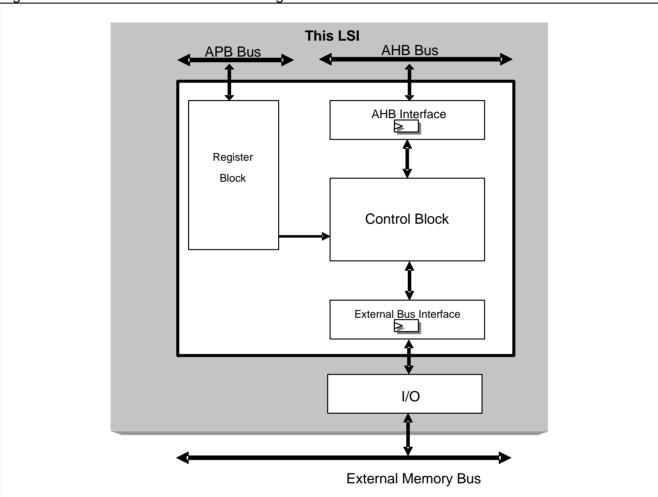

| Overview of External Bus Interface                          | 618 |

| 2. Block Diagram                                            | 620 |

| 3. Operations                                               | 623 |

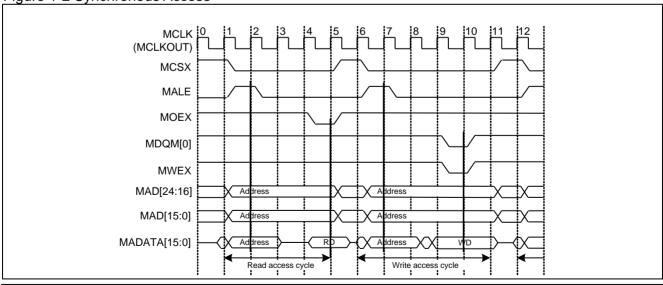

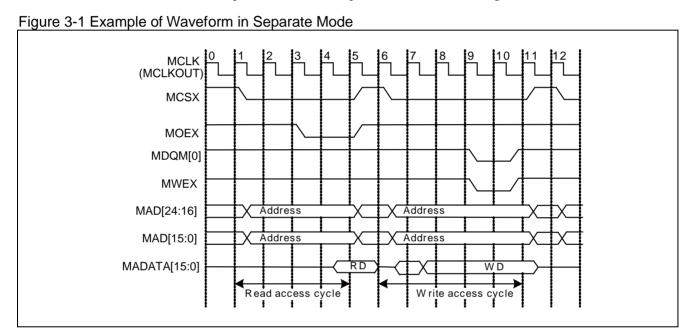

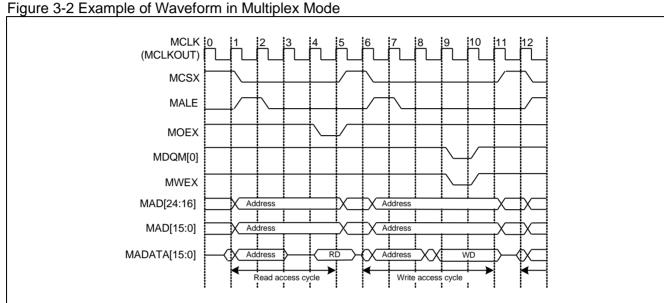

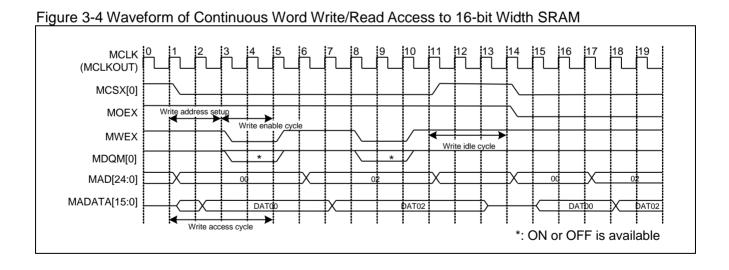

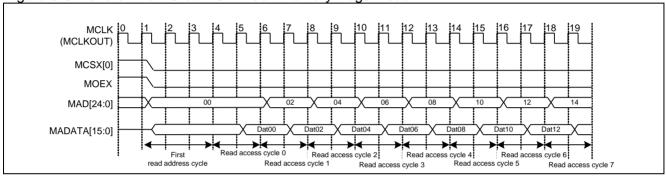

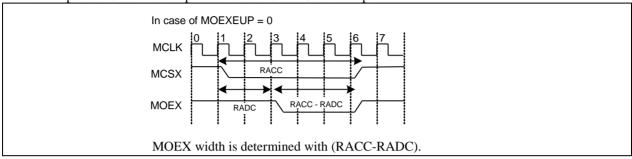

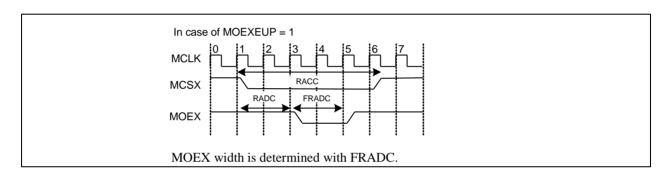

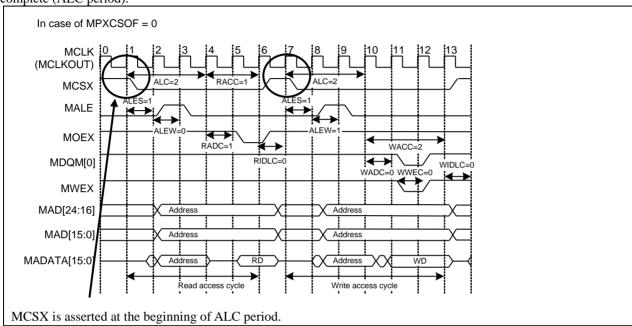

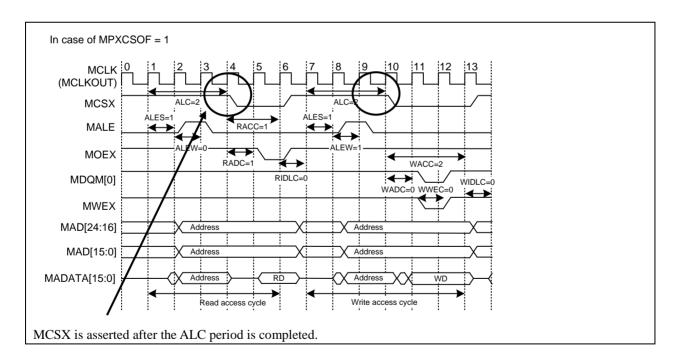

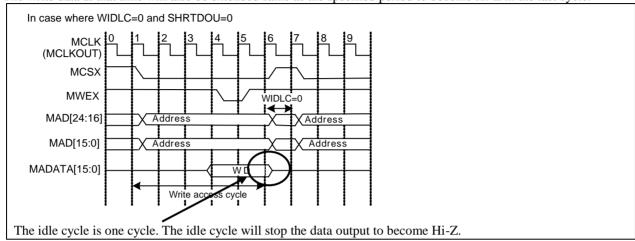

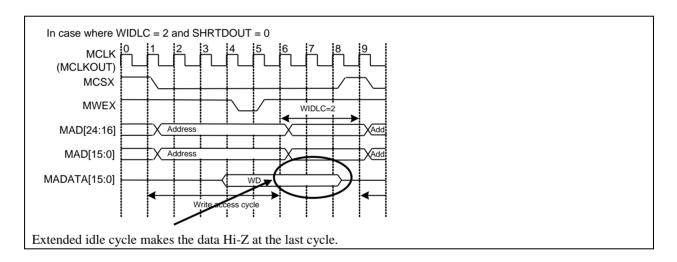

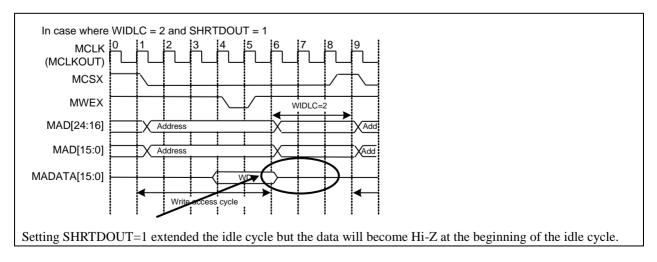

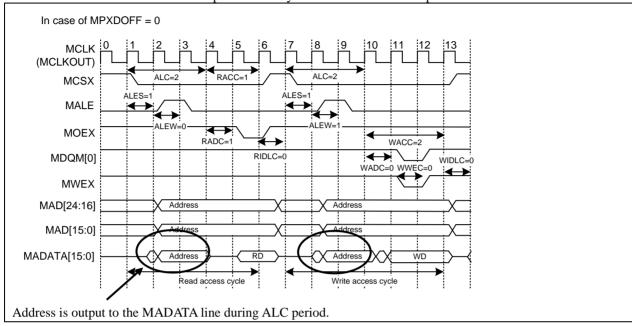

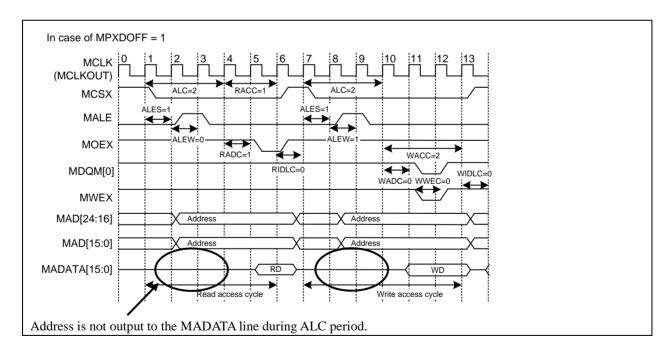

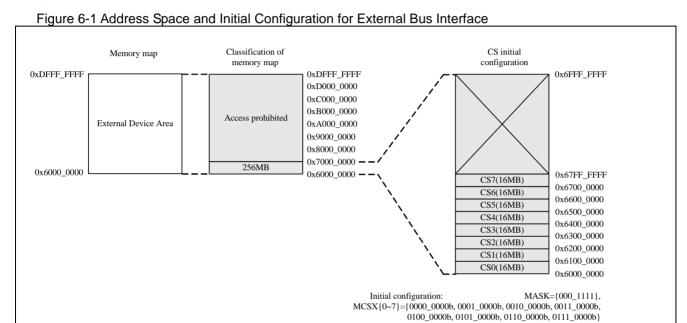

| 3.1. Bus Access Mode                                        | 624 |

| 3.2. SRAM and NOR Flash Memories Access                     | 629 |

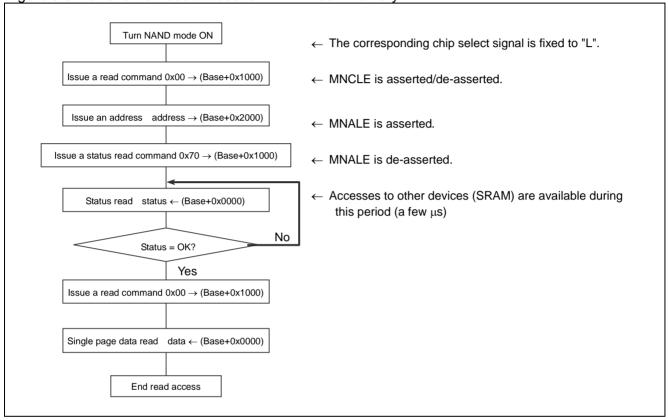

| 3.3. NAND Flash memory access                               | 631 |

| 3.3.1. Read access to NAND Flash memory                     |     |

| 3.3.2. Write (auto program) access                          |     |

| 3.3.3. Auto block erase access                              |     |

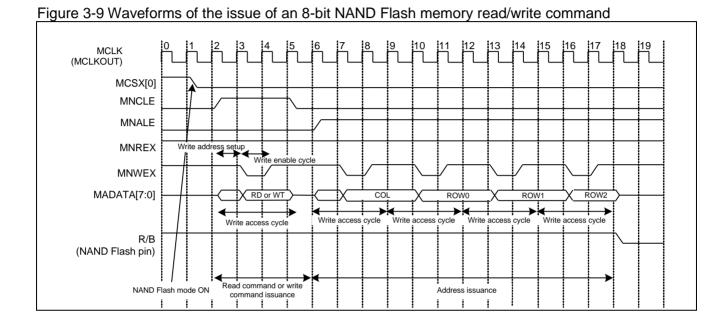

| 3.4. Issue of an 8-bit NAND Flash memory read/write command |     |

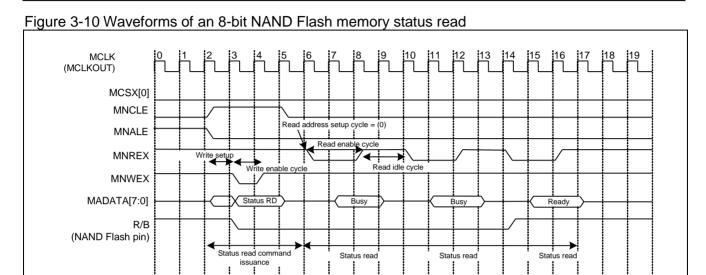

| 3.5. 8-bit NAND Flash memory status read                    |     |

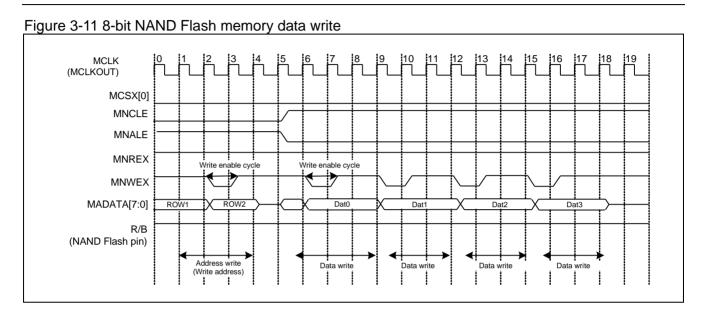

| 3.6. 8-bit NAND Flash memory data write                     |     |

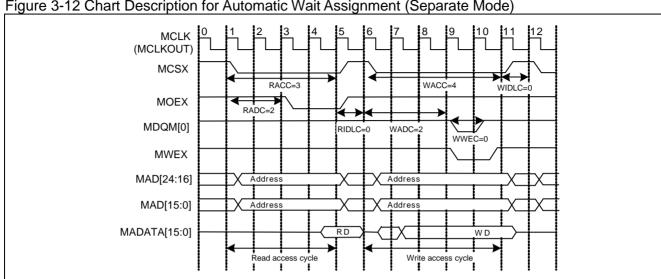

| 3.7. Automatic Wait Setup                                   |     |

| 3.8. External RDY                                           |     |

| 4. Connection Examples                                      |     |

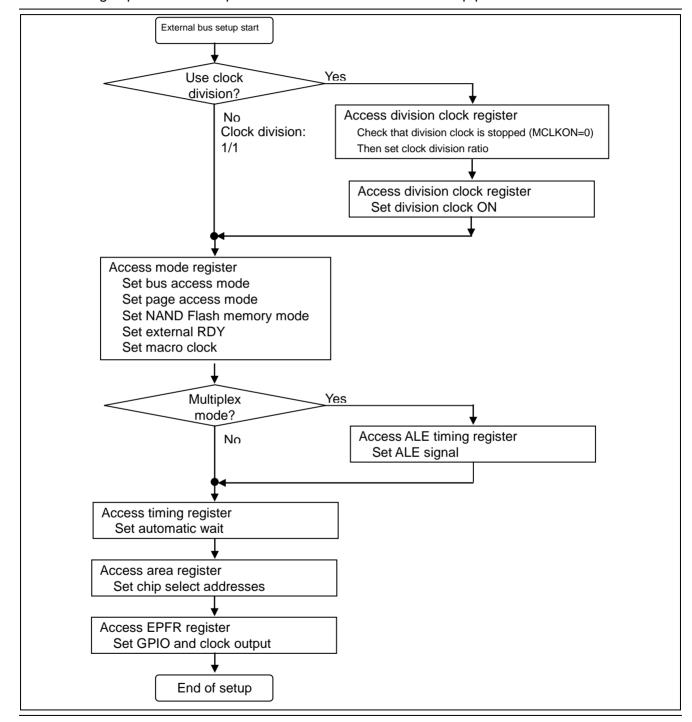

| 5. Setup Procedure Example                                  |     |

| 6. Registers                                                |     |

| 6.1. Mode Register 0 to Mode Register 7 (MODE0 to MODE7)    |     |

| 6.2. Timing Register 0 to Timing Register 7 (TIM0 to TIM7)  |     |

| 6.3. Area Register 0 to Area Register 7 (AREA0 to AREA7)    |     |

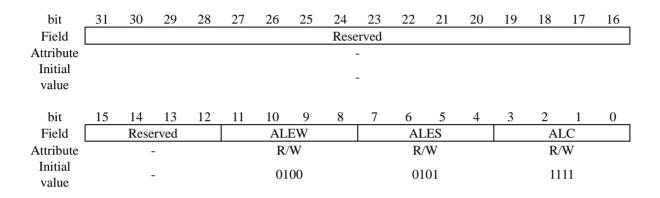

| 6.4. ALE Timing Register 0 to 7 (ATIM0 to ATIM7)            |     |

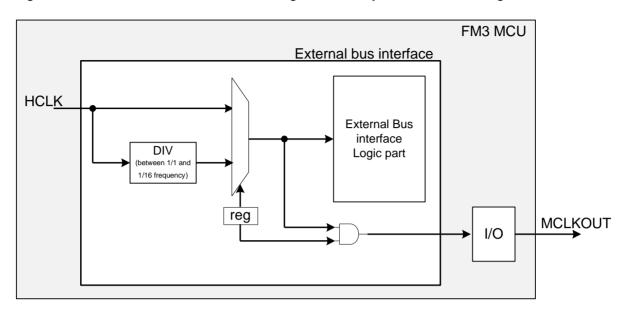

| 6.5. Division Clock Register (DCLKR)                        |     |

| 7. Usage Precautions                                        |     |

| CHAPTER 13: Debug Interface                                 |     |

| 1. Overview                                                 |     |

| 2. Pin Description                                          |     |

| 2.1. Pins for Debug Purposes                                |     |

| 2.2. ETM Pins                                               |     |

| 2.3. Functions Initially Assigned to Pins                   |     |

| 2.4. Internal Pull-Ups of JTAG Pins                         |     |

| CHAPTER14: Flash Memory                                     |     |

| CHAPTER15: Unique ID Register                               |     |

| 1. Overview                                                 |     |

| 2. Registers                                                |     |

| 2.1. Unique ID Register 0 (UIDR0: Unique ID Register 0)     |     |

| 2.2. Unique ID Register 1 (UIDR0: Unique ID Register 1)     | 681 |

| Appendi  | ixes                                                     | 683 |

|----------|----------------------------------------------------------|-----|

| Α        | Register Map                                             | 684 |

|          | 1. Register Map                                          | 685 |

| В        | List of Notes                                            | 747 |

|          | 1. Notes when high-speed CR is used for the master clock | 748 |

| С        | List of Limitations                                      | 749 |

|          | 1. List of Limitations for TYPE0 Products                | 750 |

|          | 2. List of Limitations for TYPE1 Products                | 753 |

| D        | Product TYPE List                                        | 755 |

|          | 1. Product TYPE List                                     | 756 |

| Major Cl | hanges                                                   | 761 |

| Revision | n History                                                | 783 |

## **CHAPTER 1: System Overview**

This chapter explains the system overview.

- 1. Bus Architecture

- 2. Cortex-M3 Architecture

- 3. Mode

CODE: 9BFSYSTEM-E06.0

## 1. Bus Architecture

This section explains the bus architecture.

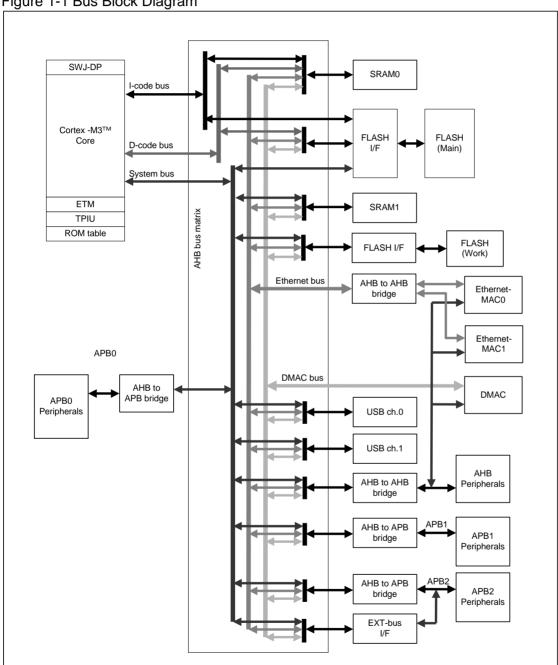

For this series bus, AHB Bus Matrix circuit actualizes a multi-layer bus. Master and slave architectures are shown below:

#### Master

- · Cortex-M3 CPU(I-code Bus, D-code Bus, System Bus)

- · DMAC

- · Ethernet

.

#### Slave

- · On-chip Flash Memory (MainFlash, WorkFlash)

- · On-chip SRAM (SRAM0, SRAM1)

- · External Bus

- · USB ch.0/ch.1

- · AHB-AHB Bus Bridge

- · AHB-APB Bus Bridge (APB0 to APB2)

See Figure 1-1 for the bus block diagram.

#### ■ Features

#### RAM Architecture

This family divides the on-chip SRAM area into two separate SRAM (SRAM0 and SRAM1). SRAM0 is connected to the I-Code bus and D-Code bus of the Cortex-M3 core. SRAM1 is connected to the System bus of the Cortex-M3 core. Also, SRAM0 and SRAM1 are connected to DMAC and other bus masters. This allows for preventing conflicts to RAM by multiple bus masters such as CPU and DMAC and allows for improving the performance. Also, because the divided RAM address areas are serial, RAM area can be utilized to the maximum extent.

#### APB Extension Bus

APB1 and APB2 Peripheral Buses are APB extension bus that the following functions are originally added based on AMBA3.0. (APB0 is not included.)

- Supporting Halfword (16-bits) and Byte(8-bits) Accesses

For supported registers, halfword access and byte access are enabled.

See "A. Register Map" in "Appendixes" for the supported registers.

- Supporting Read-Modify-Write (RMW) Accesses Bit-band operation is generated RMW access.

When performing bit-band operation to the register containing the flag that is set to 1 by hardware, the flag corresponding to the RMW access is not cleared to 0.

The corresponding flag reads 1 in read during the RMW access and ignore 1 write.

When the flag is set immediately after the read in the sequence from read to modify to write, the flag is not cleared in the write.

For the corresponding flags and registers, it is described that "In RMW access, read value is 1".

#### <Notes>

- · Bit-band operation must not be performed to a register which RMW access is prohibited.

- · When Read-Modify-Write process is performed over the software without bit-band operation, RMW access is not generated.

- Therefore, in this case, the flag value can be read in read operation although a register supports RMW access, and it is necessary not to be cleared an unrelated flag mistakenly in write operation.

- · For the details of bit-band operations, see the "Cortex-M3 Technical Reference Manual".

## Priority Level

TYPE0 products set the bus mastership as "DMAC>CPU".

According to DMAC access settings such as a case where DMAC is always accessed by a burst transfer, access to CPU may be controlled. Please pay extra attention to DMAC transfer settings.

For products other than TYPE0, a priority of the bus mastership is determined in round-robin scheduling.

#### Endian

This family uses little endian byte order.

## 1.1. Bus Block Diagram

Figure 1-1 illustrates the bus block diagram.

Figure 1-1 Bus Block Diagram

#### <Note>

There are some areas which no DMAC transfer can be performed. For details, see the DMAC Transfer column in Table 1-1.

## 1.2. Memory Architecture

This section shows the memory architecture.

For this family, 4G-byte address space is available.

Maximum 1M-byte FLASH memory, maximum 512K-byte SRAM0 area, and maximum 512K-byte SRAM1 area are defined.

Also, as an external bus area, 2G-byte area from 0x60000000 to 0xDFFFFFFF is defined. An external memory device can be connected to this area.

Section "1.3 Memory Map" illustrates the memory map, and Section "1.4 Peripheral Address Map" illustrates the peripheral address map.

For the details of Cortex-M3 private peripheral area and bit-band area shown in Figure 1-2, see "Cortex-M3 Technical Reference Manual".

## 1.3. Memory Map

Figure 1-2 illustrates the memory map.

| Figure 1-2 Memory Map |                            |            |             |                        |  |

|-----------------------|----------------------------|------------|-------------|------------------------|--|

|                       |                            |            |             | Peripherals Area       |  |

|                       |                            |            | 0x41FF_FFFF | ·                      |  |

|                       |                            |            |             | Reserved               |  |

|                       |                            | <i>-</i> - | 0x4006_9000 |                        |  |

|                       |                            | į          | _           | F.1 MAG4               |  |

|                       |                            | į          | 0x4006_7000 | Ethernet-MAC1          |  |

|                       |                            | /          | 0x4006 6000 | Ethernet-Control-Reg.  |  |

|                       |                            | - /        | 0x4000_0000 | Eth MACO               |  |

| 0xFFFF_FFFF           |                            | <i>j</i>   | 0x4006_4000 | Ethernet-MAC0          |  |

|                       | Reserved                   | į          | 0x4006_3000 | CAN ch.1               |  |

| 0xE010_0000           |                            | <i>i</i>   | 0x4006_2000 | CAN ch.0               |  |

|                       | Cortex-M3 Private          | }          | 0x4006_1000 | Reserved               |  |

| 0xE000_0000           | Peripherals                | į          | 0x4006_0000 | DMAC                   |  |

|                       |                            | <i>!</i>   |             | USB ch.1               |  |

|                       |                            | !          | 0x4005_0000 |                        |  |

|                       |                            | į į        |             | USB ch.0               |  |

|                       | Reserved                   | į          | 0x4004_0000 |                        |  |

|                       |                            | ;          | 0x4003_F000 | EXT-Bus I/F            |  |

|                       |                            | ļ į        | 0x4003_D000 | Reserved               |  |

| 0x7000_0000           |                            | <i> </i>   | 0x4003_C000 | Low-speed CR Prescaler |  |

|                       | External Device Area       | }          | 0x4003_B000 | RTC                    |  |

| 0x6000_0000           |                            | į          | 0x4003_A000 | Watch Counter          |  |

|                       |                            | !          | 0x4003_9000 | CRC                    |  |

|                       | Reserved                   | į          | 0x4003_8000 | MFS                    |  |

| 0x4400_0000           |                            |            | 0x4003_7000 | CAN Prescaler          |  |

|                       | 32Mbytes                   | į          | 0x4003_6000 | USB Clock              |  |

| 0x4200_0000           | Bit band alias             | <i>]</i>   | 0x4003_5000 | LVD/DS mode            |  |

|                       | Peripherals Area           |            | 0x4003_4000 | RCEC                   |  |

| 0x4000_0000           | . onpriorate 7 trea        |            | 0x4003_3000 | GPIO                   |  |

|                       | Reserved                   | Ì          | 0x4003_2000 | LCDC                   |  |

| 0x2400_0000           |                            | Ì          | 0x4003_1000 | Int-Req.Read           |  |

|                       | 32Mbytes                   | \          | 0x4003_0000 | EXTI                   |  |

| 0x2200_0000           | Bit band alias             | Ì          | 0x4002_F000 | Reserved               |  |

|                       | Reserved                   | Ì          | 0x4002_E000 | CR Trim                |  |

| 0x200E_1000           |                            | }          | 0x4002_9000 | Reserved               |  |

| 0x200E_0000           | Flash I/F(Work)            | į          | 0x4002_8000 | D/AC                   |  |

| 0x200C_0000           | Flash(Work)                | \          | 0x4002_7000 | A/DC                   |  |

|                       | Reserved                   | \          | 0x4002_6000 | QPRC                   |  |

| 0x2001_8000           |                            | i          | 0x4002_5000 | Base Timer             |  |

| 0x2000_0000           | SRAM1                      | \          | 0x4002_4000 | PPG                    |  |

| 0x1FFE_8000           | SRAM0                      | į          | 0x4002_3000 | Reserved               |  |

|                       | Reserved                   | Ì          | 0x4002_2000 | MFT unit2              |  |

|                       |                            | 1          | 0x4002_1000 | MFT unit1              |  |

|                       | Flash(Work area)*          | į          | 0x4002_0000 | MFT unit0              |  |

|                       | Reserved Security/CR Trim* | ļ          | 0x4001_6000 | Reserved               |  |

|                       | Coounty/Or mill            | į          | 0x4001_5000 | Dual Timer             |  |

|                       |                            | 1          | 0x4001_3000 | Reserved               |  |

|                       | Flash(Main)                | }          | 0x4001_3000 | SW WDT                 |  |

|                       |                            | Ì          | 0x4001_2000 | HW WDT                 |  |

| 0x0000_0000           |                            | 1          | 0x4001_1000 | Clock/Reset            |  |

| 0,0000_0000           |                            | 1          | 5A+001_0000 | 5.55.4.1.555.          |  |

|                       |                            | í<br>!     | 0x4000_1000 | Reserved               |  |

|                       |                            | \          | 0x4000_0000 | Flash I/F(Main)        |  |

<sup>\*:</sup> For addresses of Security/CR Trim areas and Flash (Work area), see the Data Sheet of the product used.

#### <Notes>

- · Do not access to reserved area.

- · For the details of flash memory, see "Flash Programming Manual" of the product used.

- · Do not perform DMAC transfer to bit-band area.

## 1.4. Peripheral Address Map

Table 1-1 shows the peripheral address map.

Table 1-1 Peripheral Address Map

| Table 1-1 Perip | heral Address | Мар    | T.               |                                                 | T                                  | 1                                                                         |

|-----------------|---------------|--------|------------------|-------------------------------------------------|------------------------------------|---------------------------------------------------------------------------|

| Start Address   | End Address   | Bus    | DMAC<br>Transfer | Peripheral                                      | Register Map                       | CHAPTER                                                                   |

| 0x4000_0000     | 0x4000_0FFF   | AHB    | Disabled         | FLASH IF Register (Main)/<br>Unique ID Register | FLASH_IF/Unique<br>ID              | *1<br>Chapter15                                                           |

| 0x4000_1000     | 0x4000_FFFF   |        |                  | Reserved                                        | -                                  | -                                                                         |

| 0x4001_0000     | 0x4001_0FFF   |        |                  | Clock and Reset Control                         | Clock /<br>Reset                   | Chapter 2-1<br>Chapter 3<br>Chapter 4<br>Chapter 6                        |

| 0x4001_1000     | 0x4001_1FFF   |        | Disabled         | Hardware Watchdog Timer                         | HWWDT                              | Chapter 1 in                                                              |

| 0x4001_2000     | 0x4001_2FFF   | APB0   |                  | Software Watchdog Timer                         | SWWDT                              | Timer Part                                                                |

| 0x4001_3000     | 0x4001_4FFF   |        |                  | Reserved                                        | -                                  | -                                                                         |

| 0x4001_5000     | 0x4001_5FFF   |        |                  | Dual Timer                                      | Dual_Timer                         | Chapter 2 in<br>Timer Part                                                |

| 0x4001_6000     | 0x4001_FFFF   |        |                  | Reserved                                        | -                                  | -                                                                         |

| 0x4002_0000     | 0x4002_0FFF   | APB1 E |                  | Multi-function Timer unit0                      | MFT                                |                                                                           |

| 0x4002_1000     | 0x4002_1FFF   |        | APB1 Enabled     | Multi-function Timer unit1                      | MFT                                | Chapter 6 in<br>Timer Part                                                |

| 0x4002_2000     | 0x4002_2FFF   |        |                  | Multi-function Timer unit2                      | MFT                                | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                   |

| 0x4002_3000     | 0x4002_3FFF   |        |                  | Reserved                                        | -                                  | -                                                                         |

| 0x4002_4000     | 0x4002_4FFF   |        |                  | PPG                                             | PPG                                | Chapter 7-2 in<br>Timer Part                                              |

| 0x4002_5000     | 0x4002_5FFF   |        |                  | Base Timer                                      | Base Timer/<br>Base Timer Selector | Chapter 5-1<br>Chapter 5-2<br>Chapter 5-3<br>Chapter 5-4<br>in Timer Part |

| 0x4002_6000     | 0x4002_6FFF   |        |                  | QPRC                                            | QPRC                               | Chapter 8-1<br>Chapter 8-2 in<br>Timer Part                               |

| 0x4002_7000     | 0x4002_7FFF   |        |                  | A/D Converter                                   | A/DC                               | Chapter 1-2<br>Chapter 1-3 in<br>Analog Macro Par                         |

| 0x4002_8000     | 0x4002_8FFF   |        |                  | D/A Converter                                   | D/AC                               | Chapter 2 in<br>Analog Macro Par                                          |

| 0x4002_9000     | 0x4002_DFFF   | APB1   | Enabled          | Reserved                                        | -                                  | -                                                                         |

| 0x4002_E000     | 0x4002_EFFF   | AFDI   |                  | High speed CR trimming                          | CR Trim                            | Chapter 2-2                                                               |

|                 |               |        |                  |                                                 |                                    |                                                                           |

|               |             | 1    | <u> </u>         |                                                                      |                           | <u> </u>                                                                                                  |                                             |

|---------------|-------------|------|------------------|----------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Start Address | End Address | Bus  | DMAC<br>Transfer | Peripheral                                                           | Register Map              | CHAPTER                                                                                                   |                                             |

| 0x4002_F000   | 0x4002_FFFF | -    |                  | Reserved                                                             | -                         | -                                                                                                         |                                             |

| 0x4003_0000   | 0x4003_0FFF |      |                  | External Interrupt                                                   | EXTI                      | Chapter 8                                                                                                 |                                             |

| 0x4003_1000   | 0x4003_1FFF |      |                  | Interrupt Factor Check<br>Register                                   | INT-Req READ              | Chapter 7-2<br>Chapter 7-3<br>Chapter 7-4                                                                 |                                             |

| 0x4003_2000   | 0x4003_2FFF |      |                  | LCDC                                                                 | LCDC                      | Chapter 3 in<br>Analog Macro<br>Part                                                                      |                                             |

| 0x4003_3000   | 0x4003_3FFF |      |                  | GPIO                                                                 | GPIO                      | Chapter 10                                                                                                |                                             |

| 0x4003_4000   | 0x4003_4FFF |      |                  | HDMI-CEC/Remote Control<br>Reception                                 | RCEC                      | Chapter 6-1 in<br>Communication<br>Macro Part                                                             |                                             |

| 0x4003_5000   | 0x4003_50FF | •    |                  | Low Voltage Detection                                                | LVD                       | Chapter 5-2<br>Chapter 5-3<br>Chapter 5-4                                                                 |                                             |

| 0x4003_5100   | 0x4003_5FFF |      |                  | Deep standby control block                                           | DS_Mode                   | Chapter 6                                                                                                 |                                             |

| 0x4003_6000   | 0x4003_6FFF | APB2 | PB2 Enabled      | USB clock generation block<br>USB/Ethernet clock<br>generation block | USB Clock                 | Chapter 2-2<br>Chapter 2-3 in<br>Communication<br>Macro Part                                              |                                             |

| 0x4003_7000   | 0x4003_7FFF |      |                  | CAN Prescaler                                                        | CAN_<br>Prescaler         | Chapter 5-1 in<br>Communication<br>Macro Part                                                             |                                             |

| 0x4003_8000   | 0x4003_8FFF |      |                  | Multi-function serial                                                | MFS                       | Chapter 1-2<br>Chapter 1-3<br>Chapter 1-4<br>Chapter 1-5<br>Chapter 1-6 in<br>Communication<br>Macro Part |                                             |

| 0x4003_9000   | 0x4003_9FFF |      |                  | CRC                                                                  | CRC                       | Chapter 11                                                                                                |                                             |

| 0x4003_A000   | 0x4003_AFFF |      |                  |                                                                      | Watch counter             | Watch Counter                                                                                             | Chapter 3-1<br>Chapter 3-2 in<br>Timer Part |

| 0x4003_B000   | 0x4003_BFFF |      |                  | Real time clock                                                      | RTC                       | Chapter 4-2<br>Chapter 4-3<br>Chapter 4-4 in<br>Timer Part                                                |                                             |

| 0x4003_C000   | 0x4003_CFFF |      |                  | Low-speed CR Prescaler                                               | Low-speed CR<br>Prescaler | Chapter 2-3                                                                                               |                                             |

| 0x4003_D000   | 0x4003_EFFF |      |                  | Reserved                                                             | -                         | -                                                                                                         |                                             |

| 0x4003_F000   | 0x4003_FFFF |      |                  | External Bus I/F                                                     | EXT-Bus I/F               | Chapter 12                                                                                                |                                             |

| Start Address | End Address | Bus         | DMAC<br>Transfer | Peripheral              | Register Map | CHAPTER                                 |

|---------------|-------------|-------------|------------------|-------------------------|--------------|-----------------------------------------|

| 0x4004_0000   | 0x4004_FFFF |             |                  | USB ch.0                | USB          | Chapter 3-1                             |

| 0x4005_0000   | 0x4005_FFFF |             |                  | USB ch.1                | USB          | Chapter 3-2 in Communication Macro Part |

| 0x4006_0000   | 0x4006_0FFF | AHB Enabled |                  | DMAC Register           | DMAC         | Chapter 9                               |

| 0x4006_1000   | 0x4006_1FFF |             | Reserved         | -                       | -            |                                         |

| 0x4006_2000   | 0x4006_2FFF |             | B Enabled        | CAN ch.0                | CAN          | Chapter 5-2 in                          |

| 0x4006_3000   | 0x4006_3FFF |             |                  | CAN ch.1                | CAN          | Communication Macro Part                |

| 0x4006_4000   | 0x4006_5FFF |             |                  | Ethernet MAC0           | *2           | *2                                      |

| 0x4006_6000   | 0x4006_6FFF |             |                  | Ethernet System Control | *2           | *2                                      |

| 0x4006_7000   | 0x4006_8FFF |             |                  | Ethernet MAC1           | *2           | *2                                      |

| 0x4006_9000   | 0x41FF_FFFF |             |                  | Reserved                | -            | -                                       |

<sup>\*1:</sup> For the details of "FLASH IF Register", see "Flash Programming Manual" of the product used.

<sup>\*2:</sup> For the details of "Ethernet MACO", "Ethernet system control", and "Ethernet MAC1", refer to "Ethernet Part".

| Start Address | End Address | Bus | DMAC<br>Transfer | Peripheral               | Register Map | Details |

|---------------|-------------|-----|------------------|--------------------------|--------------|---------|

| 0x200E_0000   | 0x200E_1000 | AHB | Enabled          | Flash IF register (Work) | "FLASH IF"   | *3      |

<sup>\*3:</sup> For the details of "FLASH IF register (Work)", refer to "Flash Programming Manual" of the product used.

## 2. Cortex-M3 Architecture

This section explains the core architecture used in this family.

Cortex-M3 core block architecture\* used in this family is as follows:

- · Cortex-M3 Core

- · NVIC

- · MPU

- · DWT

- · ITM

- · FPB

- · ETM

- · SWJ-DP

- · TPIU

- ROM Table

---

· \*: The architecture varies depending on the products. For details, see 2.1 Option Configuration.

#### **■** Cortex-M3 Core

High-performance 32-bit processor core (ARM Cortex-M3 core) is equipped with this family. This peripheral manual does not describe the details of Cortex-M3 core. For the details, see "Cortex-M3 Technical Reference Manual".

· Cortex-M3 Core Version For the version of Cortex-M3 core, See "Data Sheet" of the product used.

## ■ NVIC (Nested Vectored Interrupt Controller)

For this family, one NMI (non-maskable interrupt) and maximum 48 peripheral interrupts (IRQ0 to IRQ47)\*1 can be used

Also, interrupt priority register (from 0xE000E400) is comprised of 4 bits, and 16 interrupt priority levels can be configured.

For the details of peripheral interrupts, see the chapter of the target "Interrupts" after check the product currently used with "Configuration of interrupts", and for NMI operations, see also another chapter "External Interrupt and NMI Control Block".

NMI pin is assigned for a combined use with a general-purpose port. Its initial value after a reset release is set to the general-purpose port, and NMI input is masked.

When NMI is used, enable NMI in the port setting.

For the details, see another chapter "I/O Port".

\*1: "Cortex-M3 Technical Reference Manual" defines an exception type: IRQ as an external interrupt. In this peripheral manual, to distinguish from an interrupt by an external pin "External Interrupt and NMI Control Block", the exception type: IRQ is indicated as a peripheral interrupt.

#### SysTick Timer

SysTick Timer is a system timer for OS task management integrated into NVIC.

This family generates STCLK through dividing HCLK by eight and sets the values of SysTick Calibration Value Register (Address: 0xE000E01C) as shown below:

bit31: NOREF = 0bit30: SKEW = 1

bit23:0: TENMS =  $0x0186A0 (100000)^{*1}$

\*1: TENMS value is set to a value which becomes 10 ms when 1/8 clock of HCLK is input to STCLK and that HCLK is in 80 MHz (10 MHz in 1/8 case).

The value of TENMS is not always 10ms because HCLK can be changed to another frequency in the clock control block. Therefore, it is required to calculate an appropriate interrupt timing according to HCLK frequency.

## ■ DWT (Data Watchpoint & Trace Unit)

This family is equipped with DWT to use as the debug function.

DWT contains four comparators, and each comparator can be set as a hardware watchpoint.

## ■ ITM (Instrumentation Trace Macrocell)

This family is equipped with ITM as a debug function.

ITM is an optional application driven trace source that supports printf style debugging. The operation system (OS) and application event are traced, and the system diagnostic information is sent.

## ■ FPB (Flash Patch & Breakpoint)

FPB has the following functions:

- · Hardware Breakpoint function

- · The function of remapping from Code memory space (FLASH) to SRAM space.

FPB is equipped with six instruction comparators and two literal comparators.

### ■ MPU (Memory Protection Unit)

This family is equipped with a Cortex-M3 optional component MPU, and maximum eight areas can be defined.

#### **■ ETM(Embedded Trace Macrocell)**

This family is equipped with a Cortex-M3 optional component ETM to support instruction trace.

#### ■ SWJ-DP

This family is equipped with SWJ-DP to support both serial wire protocol and JTAG protocol.

## **■ TPIU (Trace Port Interface Unit)**

ETM/ITM trace information is output via TPIU.

### ■ ROM Table

ROM table provides the address information of a debug component to an external debug tool.

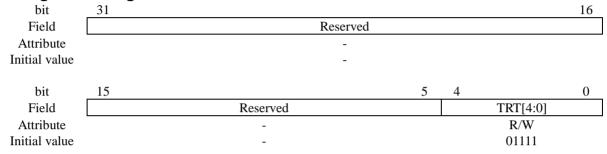

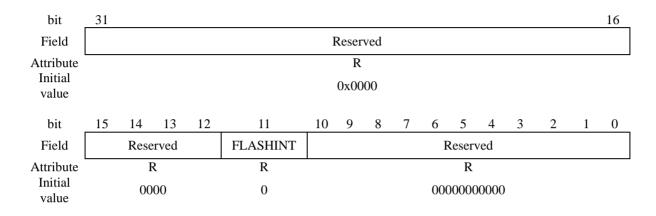

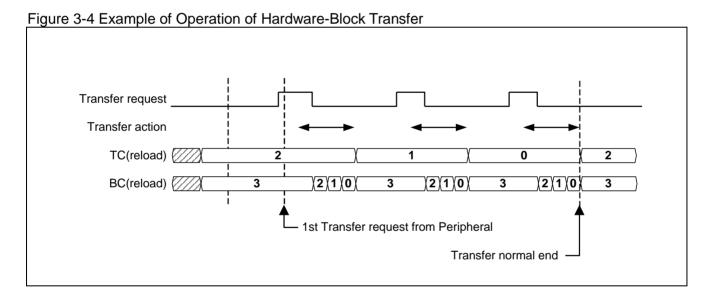

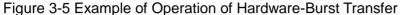

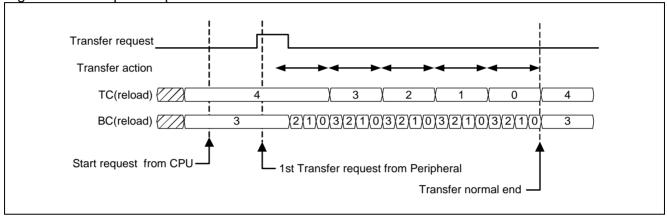

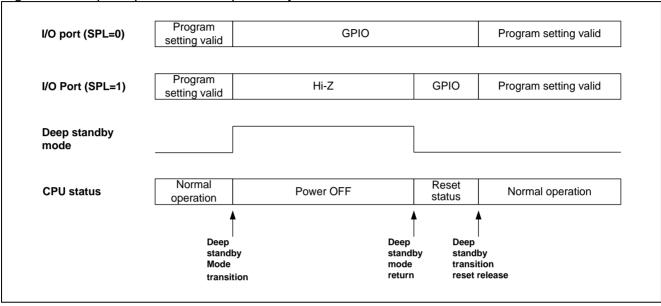

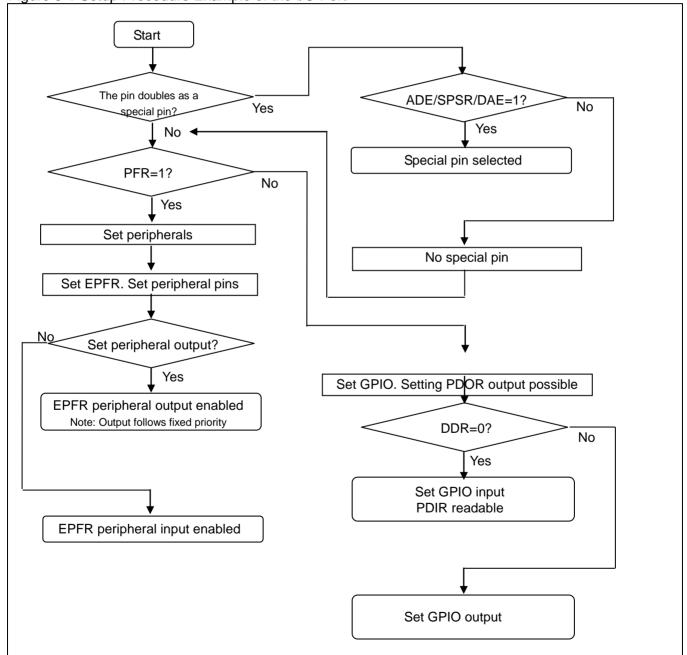

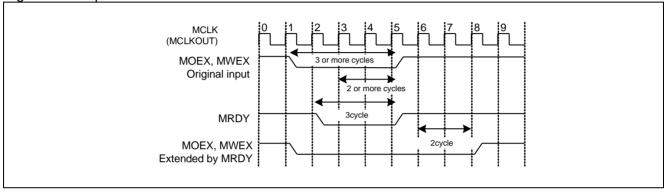

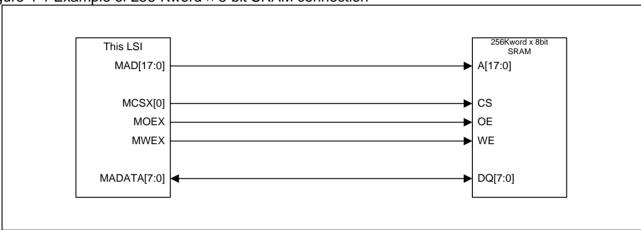

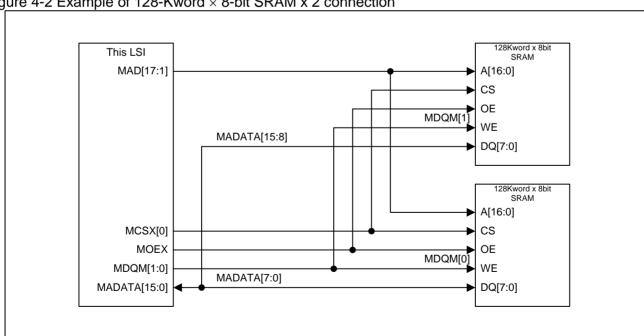

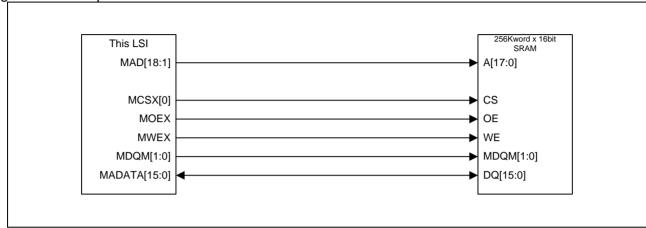

## 2.1. Option configuration