**FUJITSU SEMICONDUCTOR LIMITED**

## **How to Use This Manual**

### ■ Finding a function

The following methods can be used to search for the explanation of a desired function in this manual:

· Search from the table of the contents

The table of the contents lists the manual contents in the order of description.

### ■ About the chapters

Basically, this manual explains Ethernet.

### **■** Terminology

This manual uses the following terminology.

| Term Explanation |                                       |  |  |

|------------------|---------------------------------------|--|--|

| Word             | Indicates access in units of 32 bits. |  |  |

| Half word        | Indicates access in units of 16 bits. |  |  |

| Byte             | Indicates access in units of 8 bits.  |  |  |

#### ■ Notations

· The notations in bit configuration of the register explanation of this manual are written as follows.

bit : bit numberField : bit field name

· Attribute: Attributes for read and write of each bit

R : Read only

W : Write only

R/W : Readable/Writable

- : Undefined

· Initial value : Initial value of the register after reset

0 : Initial value is "0"

1 : Initial value is "1"

X : Initial value is undefined

· The multiple bits are written as follows in this manual.

Example: bit7:0 indicates the bits from bit7 to bit0

· The values such as for addresses are written as follows in this manual.

Hexadecimal number: "0x" is attached in the beginning of a value as a prefix (example: 0xFFFF)

Binary number: "0b" is attached in the beginning of a value as a prefix (example: 0b1111)

· Decimal number : Written using numbers only (example : 1000)

## ■ The target products in this manual

Table 1 Target Products List

| <u> </u>        |                       |  |

|-----------------|-----------------------|--|

| Series Name     | Product Name          |  |

|                 | MB9BFD18S, MB9BFD18T, |  |

| MB9BD10T Series | MB9BFD17S, MB9BFD17T, |  |

|                 | MB9BFD16S, MB9BFD16T  |  |

|                 | MB9BF618S, MB9BF618T, |  |

| MB9B610T Series | MB9BF617S, MB9BF617T, |  |

|                 | MB9BF616S, MB9BF616T  |  |

|                 | MB9BF218S, MB9BF218T, |  |

| MB9B210T Series | MB9BF217S, MB9BF217T, |  |

|                 | MB9BF216S, MB9BF216T  |  |

## **CONTENTS**

| CHAPTER 1: Ethernet                                              | 1  |

|------------------------------------------------------------------|----|

| 1. Overview                                                      | 2  |

| 2. I/O Signal of Ethernet                                        | 4  |

| 3. Ethernet-MAC Setup Control Procedure                          | 8  |

| 4. Ethernet System Control Block Register                        | 9  |

| 4.1. Mode Select Register (ETH_MODE)                             |    |

| 4.2. Clock Gating Register (ETH_CLKG)                            | 12 |

| CHAPTER 2: Ethernet-MAC                                          | 13 |

| 1. General Description                                           | 14 |

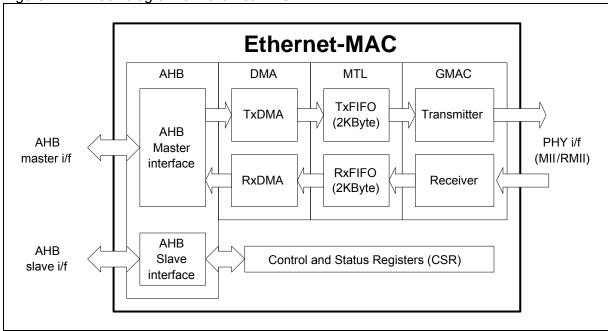

| 2. Block Configuration                                           | 15 |

| 3. Architecture                                                  | 16 |

| 3.1. Pin Functions                                               | 17 |

| 3.2. AHB Application Host Interface                              | 19 |

| 3.3. DMA Controller                                              |    |

| 3.4. Checksum Engine                                             |    |

| 3.5. Energy Efficient Ethernet                                   |    |

| 3.6. MAC Management Counters                                     |    |

| 3.7. Station Management Agent                                    |    |

| 3.8. IEEE1588                                                    |    |

| 4. Registers                                                     |    |

| 4.1. MCR (GMAC Register 0)                                       |    |

| 4.3. GMAC Register 2, 3 (MHTRH, MHTRL)                           |    |

| 4.4. GAR (GMAC Register 4)                                       |    |

| 4.5. GDR (GMAC Register 5)                                       |    |

| 4.6. FCR (GMAC Register 6)                                       |    |

| 4.7. VTR (GMAC Register 7)                                       | 72 |

| 4.8. RWFFR (GMAC Register 10)                                    | 74 |

| 4.9. PMTR (GMAC Register 11)                                     |    |

| 4.10. LPICSR (GMAC Register 12)                                  |    |

| 4.11. LPITCR (GMAC Register 13)                                  |    |

| 4.12. ISR (GMAC Register 14)                                     |    |

| 4.13. IMR (GMAC Register 15)4.14. MAR0H (GMAC Register 16)       |    |

| 4.15. MAROL (GMAC Register 17)                                   |    |

| 4.16. MAR1H,MAR2H,MAR3H,,MAR31H(GMAC Register 18,20,22,, 542)    |    |

| 4.17. MAR1L,MAR2L,MAR3L,,MAR31L(GMAC Register 19,21,23,25,, 543) |    |

| 4.18. RGSR (GMAC Register 54)                                    |    |

| 4.19. TSCR (GMAC Register 448)                                   | 91 |

| 4.20. SSIR (GMAC Register 449)                                   | 94 |

| 4.21. STSR (GMAC Register 450)                                   |    |

| 4.22. STNR (GMAC Register 451)                                   |    |

| 4.23. STSUR (GMAC Register 452)                                  |    |

| 4.24. STNUR (GMAC Register 453)                                  |    |

| 4.25. TSAR (GMAC Register 454)                                   | 99 |

| 4.26. TTSR (GMAC Register 455)                             | 100 |

|------------------------------------------------------------|-----|

| 4.27. TTNR (GMAC Register 456)                             | 101 |

| 4.28. STHWSR (GMAC Register 457)                           | 102 |

| 4.29. TSR (GMAC Register 458)                              | 103 |

| 4.30. PPSCR (GMAC Register 459)                            | 105 |

| 4.31. ATNR (GMAC Register 460)                             | 107 |

| 4.32. ATSR (GMAC Register 461)                             | 108 |

| 4.33. BMR (DMA Register 0)                                 | 109 |

| 4.34. TPDR (DMA Register 1)                                | 112 |

| 4.35. RPDR (DMA Register 2)                                | 113 |

| 4.36. RDLAR (DMA Register 3)                               | 114 |

| 4.37. TDLAR (DMA Register 4)                               | 115 |

| 4.38. SR (DMA Register 5)                                  | 116 |

| 4.39. OMR (DMA Register 6)                                 | 120 |

| 4.40. IER (DMA Register 7)                                 | 123 |

| 4.41. MFBOCR (DMA Register 8)                              | 126 |

| 4.42. RIWTR (DMA Register 9)                               | 127 |

| 4.43. AHBSR (DMA Register 11)                              | 128 |

| 4.44. CHTDR (DMA Register 18)                              | 129 |

| 4.45. CHRDR (DMA Register 19)                              | 130 |

| 4.46. CHTBAR (DMA Register 20)                             | 131 |

| 4.47. CHRBAR (DMA Register 21)                             | 132 |

| 4.48. MMC Register list                                    | 133 |

| 4.49. MMC Control Register                                 | 139 |

| 4.50. MMC Receive Interrupt Register                       | 140 |

| 4.51. MMC Transmit Interrupt Register                      | 142 |

| 4.52. MMC Receive Interrupt Mask Register                  | 144 |

| 4.53. MMC Transmit Interrupt Mask Register                 | 146 |

| 4.54. MMC Receive Checksum Offload Interrupt Mask Register | 148 |

| 4.55. MMC Receive Checksum Offload Interrupt Register      | 151 |

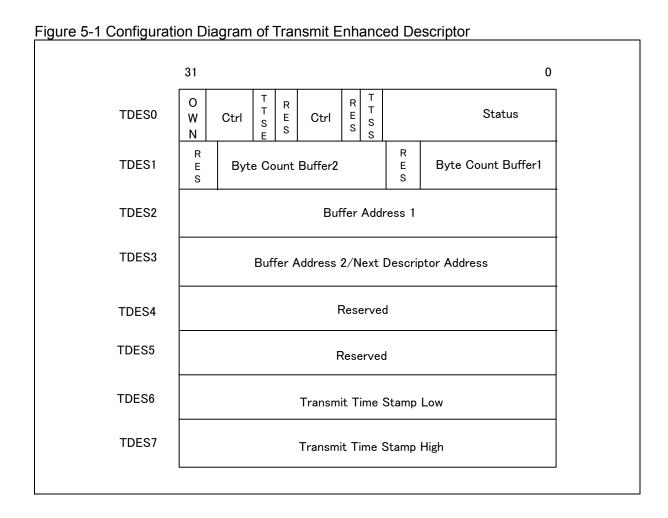

| 5. Descriptors                                             | 153 |

| 5.1. Transmit Enhanced Descriptor                          |     |

| 5.1.1. Transmit Enhanced Descriptor 0 (TDES0)              |     |

| 5.1.2. Transmit Enhanced Descriptor 1 (TDES1)              |     |

| 5.1.3. Transmit Enhanced Descriptor 2 (TDES2)              |     |

| 5.1.4. Transmit Enhanced Descriptor 3 (TDES3)              | 160 |

| 5.1.5. Transmit Enhanced Descriptor 6 (TDES6)              |     |

| 5.1.6. Transmit Enhanced Descriptor 7 (TDES7)              |     |

| 5.2. Receive Enhanced Descriptor                           |     |

| 5.2.1. Receive Enhanced Descriptor 0 (RDES0)               | 164 |

| 5.2.2. Receive Enhanced Descriptor 1 (RDES1)               | 166 |

| 5.2.3. Receive Enhanced Descriptor 2 (RDES2)               |     |

| 5.2.4. Receive Enhanced Descriptor 3 (RDES3)               |     |

| 5.2.5. Receive Enhanced Descriptor 4 (RDES4)               |     |

| 5.2.6. Receive Enhanced Descriptor 6 (RDES6)               |     |

| 5.2.7. Receive Enhanced Descriptor 7 (RDES7)               |     |

| 6. Programming Guide                                       | 173 |

| _                                                          |     |

# Major changes in this edition

A change on a page is indicated by a vertical line drawn on the left of that page.

| Page     | Section                                                                                        | Changes                                                                                                                                           |

|----------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| -        | Cover page                                                                                     | Revised the title                                                                                                                                 |

| (5)      | ■The target products in this manual                                                            | Added new section                                                                                                                                 |

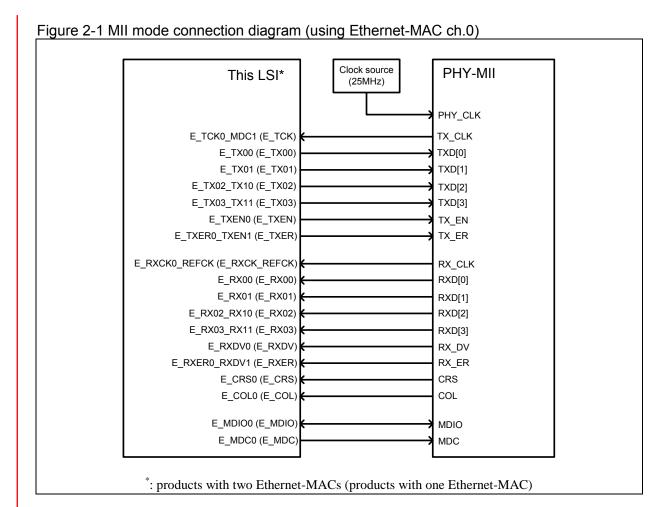

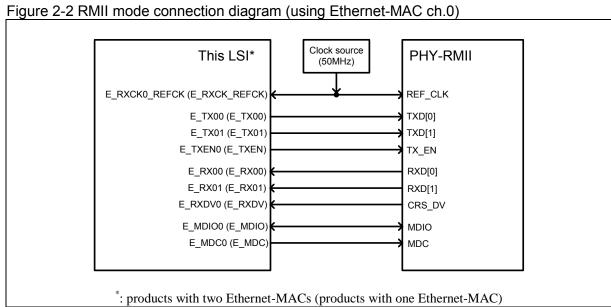

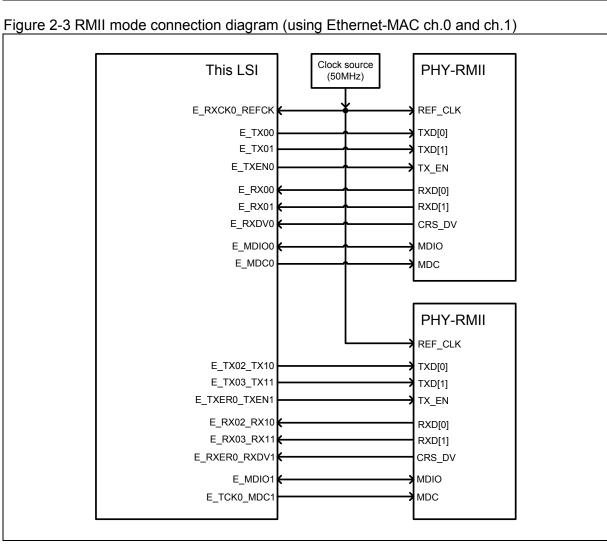

| 5, 6     | CHAPTER1 2. I/O Signal of Ethernet • Example of connection to external PHY                     | Revised Figure 2-1, Figure 2-2 and Figure 2-3                                                                                                     |

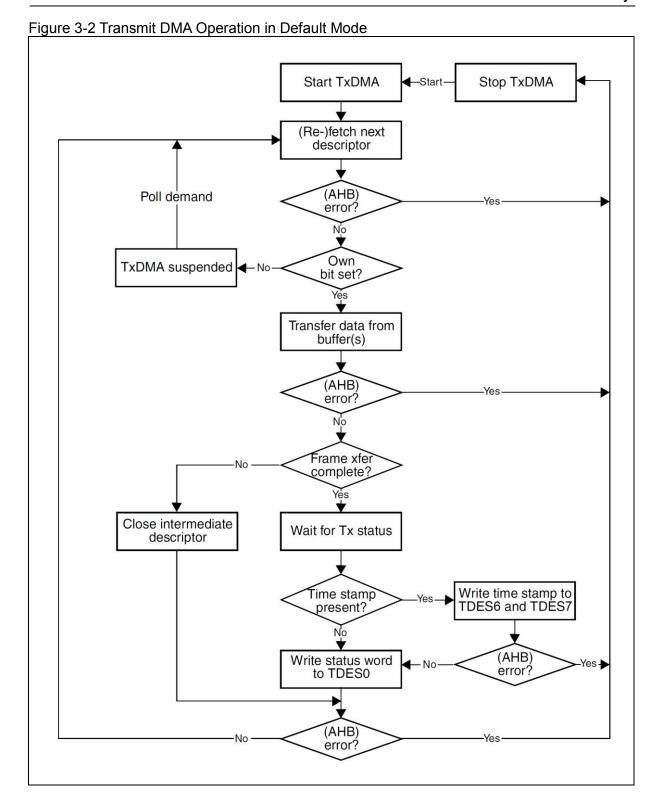

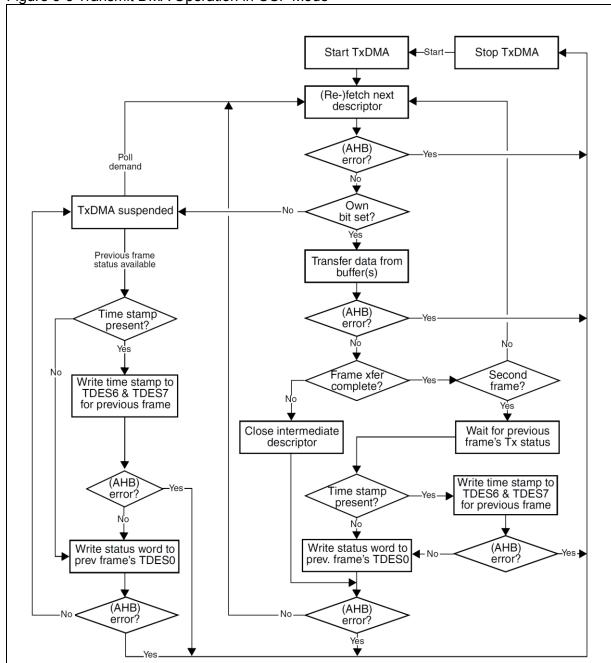

| 23       | CHAPTER 2 3.3 DMA Controller  Transmission  Transmission DMA Operation: Default (Non-OSF) Mode | Revised the following description of the procedure 8:<br>Interrupt on Completion (TDES1[30])  → Interrupt on Completion (TDES0[30])               |

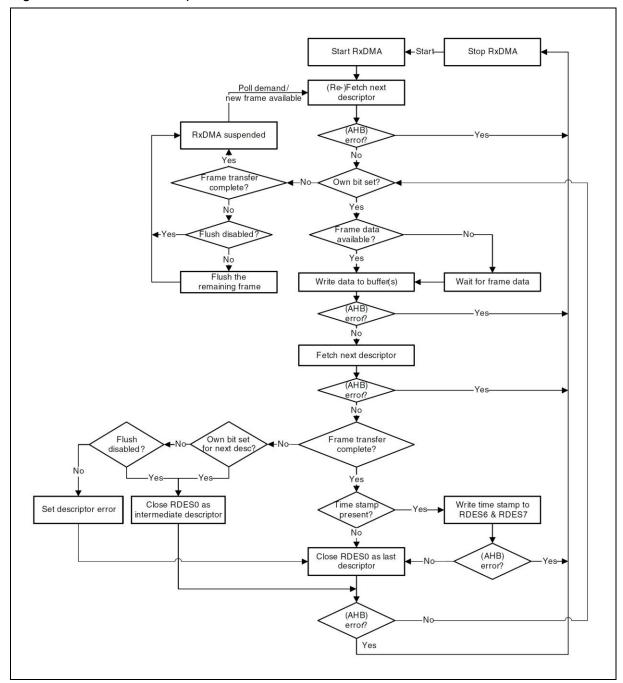

| 28       | CHAPTER 2 3.3 DMA Controller  Reception  Receive Descriptor Acquisition                        | Revised the following description:  The Receive Register → The Receive Engine                                                                     |

| 31       | CHAPTER 2 3.4 Checksum Engine  TCP/UDP/ICMP Checksum Engine                                    | Added the description to the Note                                                                                                                 |

| 33       | CHAPTER 2 3.4 Checksum Engine  Receive Checksum  Offload Engine                                | Added the description to the Note                                                                                                                 |

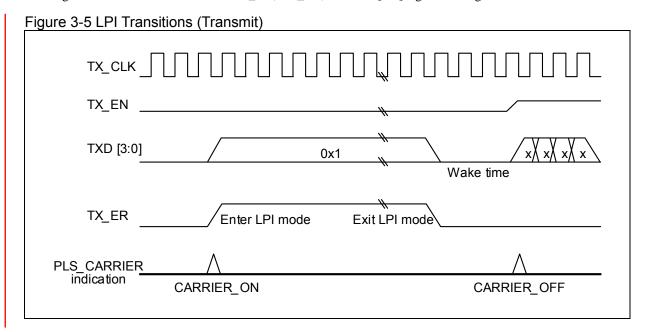

| 35       | CHAPTER 2 3.5 Energy Efficient Ethernet  Transmit Path Functions                               | Revised Figure 3-5                                                                                                                                |

| 37       | CHAPTER 2 3.6 MAC Management Counters  MMC Operation                                           | Added the descriptions to "MMC Operations"                                                                                                        |

| 49 to 52 | CHAPTER 2 4. Registers  Register Map                                                           | Revised Table 4-1                                                                                                                                 |

| 56       | CHAPTER 2<br>4.1 GMAC Register 0                                                               | Added the Note to "IPC (Checksum Offload)"                                                                                                        |

| 57       | (MCR)                                                                                          | Added the Note to "ACS (Automatic Pad/CRC Stripping)"                                                                                             |

| 78       | CHAPTER 2<br>4.12 GMAC Register 14<br>(ISR)                                                    | Revised the following descriptions of "RIS":  GMAC register65(MMC Transmit Interrupt Register)  → GMAC register65(MMC Receive Interrupt Register) |

| Page   | Section                                                      | Changes                                                                                              |

|--------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 87, 89 | CHAPTER 2<br>4.19 GMAC Register 448<br>(TSCR)                | Revised the following bit name:<br>TSCT → TSPS                                                       |

| 99     | CHAPTER 2<br>4.29 GMAC Register 458<br>(TSR)                 | Revised the descriptions of "TRGTER"                                                                 |

| 101    | CHAPTER 2<br>4.30 GMAC Register 459<br>(PPSCR)               | Revised the Initial value of bit3                                                                    |

| 105    | CHAPTER 2<br>4.33 BMR (DMA Register<br>0)                    | Revised the description of BMR (Bus Mode Register)                                                   |

| 116    | CHAPTER 2<br>4.39 DMA Register 6<br>(OMR)                    | Revised the following description of "RSF": MLT-receive FIFO → MTL Receive FIFO                      |

| 152    | CHAPTER 2<br>5.1.1 Transmit Enhanced<br>Descriptor 0 (TDES0) | Added the Note to "CIC (Checksum Insertion Control)"                                                 |

| 161    | CHAPTER 2<br>5.2.1 Receive Enhanced<br>Descriptor 0 (RDES0)  | Deleted the following description of "DE(Dribble Bit Error)":<br>This bit is valid only in MII Mode. |

| 169    | CHAPTER 2 6. Registers  Register Map                         | Revised the description of the procedure 5 and 9                                                     |

In the previous revision, the number at the upper-right of the page is MN706-00015-1v0-E.

## **CHAPTER: Ethernet**

This chapter describes the configuration of Ethernet related blocks.

- 1. Overview

- 2. I/O Signal of Ethernet

- 3. Ethernet-MAC Setup Control Procedure

- 4. Ethernet System Control Block Register

CODE: 9xETHER-E02.0

## 1. Overview

This section describes the overview of Ethernet function and Ethernet-MAC setup control procedure.

#### Overview

The Ethernet function of this family is composed of Ethernet-MAC block and its peripheral circuit. This chapter describes Ethernet-MAC the peripheral circuit and Ethernet-MAC setup control procedure.

#### ■ Block diagram

Figure 1-1 shows the configuration diagram of the Ethernet-MAC and peripheral circuit.

Figure 1-1 Configuration diagram of Ethernet-MAC and peripheral circuit **Ethernet Clock** generator (PLL) CPU sud Ethernet system control block **DMAC** Ethernet MAC block (ch.0) 5 **FIFO** Transmit port control block **FLASH** DMAC (2KB) control **FIFO** Receive (2KB) control II/RMII mode selecto **SRAM** Control and Status Registers External Memory Ethernet-MAC block (ch.1) **FIFO** Transmit DMAC (2KB) control Peripheral **FIFO** Receive (2KB) control Control and Status Registers

1. Overview

## ■ Description of each block

#### Ethernet-MAC block

Ethernet-MAC is the block that controls Ethernet communication protocol control. Although there are two EthernetMACs (ch.0 and ch.1) in the block diagram, some products have only ch.0 and other products have both ch.0 and ch.1. The products that have only one Ethernet-MAC cannot use the ch.1 side. Those that have two EthernetMACs can use both of them separately.

Each Ethernet-MAC is composed of send control block, receive control block, FIFO memory, and dedicated DMAC. It controls the operation by instructing the control register block (Control and Status Registers) from the CPU. The dedicated DMAC uses a descriptor on the memory that is created by the CPU and executes send and receive data transfers. For details on Ethernet-MAC, see the chapter "Ethernet-MAC".

To operate each Ethernet-MAC, execute the following Ethernet-MAC setup by register writing to the Ethernet system control block beforehand.

- 1. Start supplying clocks for each Ethernet-MAC

- 2. Select MII/RMII mode

- 3. Issue a hardware reset to each Ethernet-MAC and restart Ethernet-MAC

For the information above, see "3. Ethernet-MAC Setup Control Procedure".

Each Ethernet-MAC executes an initial setting to instruct the start of the operation after releasing the hardware reset of the above setup. Internal registers of each Ethernet-MAC have spots that select MII/RMII. These are set separately from the above setup procedure.

#### Ethernet system control block

Ethernet system control block controls the peripheral circuit of Ethernet-MAC and the setup of each Ethernet-MAC. The setup control procedure is described in "3. Ethernet-MAC Setup Control Procedure". Also, the register functions of the Ethernet system control block are described in "4. Ethernet System Control Block Register".

If each Ethernet-MAC is not operated, you can execute low power consumption of the microcontroller by stopping the supply of clock signals. If it is switched to stop, the supply of clock signals setup control becomes necessary.

#### MII/RMII mode selector

MII/RMII mode selector is the selector block that connects the external PHY interface signal of Ethernet-MAC with the I/O port control block. Based on the register setting of the Ethernet system control block, the interface mode (MII or RMII) to use is selected.

#### • I/O port control block

Pin functions of the external pins of the microcontroller are used with the peripheral function block pins other than Ethernet (e.g. GPIO). The setting of control registers in the I/O port block is required to use the external pins of the microcontroller as external PHY interface pins of Ethernet.

When the microcontroller is in low power consumption mode (STOP mode and TIMER mode), I/O signals of PHY interface pin must be enabled (called the last retention state) to receive WakeUP packet from external PHY.

For details on the I/O port control block, see the chapter "I/O PORT" in "PERIPHERAL MANUAL".

#### Ethernet clock generator

The clock signals generated by the Ethernet clock generator can be output to microcontroller pin. If the above clock output signals are generated by PLL, input clock oscillation accuracy of general external PHY devices cannot be guaranteed. So, please be careful. For details on the Ethernet clock generator, see the chapter "USB/Ethernet Clock Generation Block" in "Communication Macro Part".

## 2. I/O Signal of Ethernet

This section describes the connection of I/O signals related to the Ethernet function.

## ■ Microcontroller external pin

#### External PHY interface signal

The functions of the Microcontroller external pin are also used by Ethernet-MAC ch.0 and ch.1 and the PHY interface signal pin of MII/RMII. Which interface signal is used is decided at the setup control of the Ethernet system control block.

Table 2-1 shows the correspondence of each microcontroller external pin name of both the product with one Ethernet-MAC and the products with two Ethernet-MACs and PHY interface signals of each Ethernet-MAC.

Table 2-1 Correspondence of microcontroller external pin name and PHY interface signals

| Microcontroller external pin name |                                 | N 411               | DMU                  | RMII                         |         |

|-----------------------------------|---------------------------------|---------------------|----------------------|------------------------------|---------|

| Product with only ch.0            | Product with both ch.0 and ch.1 | MII<br>(using ch.0) | RMII<br>(using ch.0) | (using ch.0<br>and ch.1)     | Remarks |

| E_RXCK_REFCK                      | E_RXCK0_REFCK                   | ch.0 RX_CLK         | ch.0 REF_CLK         | ch.0 REF_CLK<br>ch.1 REF_CLK | *1      |

| E_RX00                            | E_RX00                          | ch.0 RXD [0]        | ch.0 RXD [0]         | ch.0 RXD [0]                 |         |

| E_RX01                            | E_RX01                          | ch.0 RXD [1]        | ch.0 RXD [1]         | ch.0 RXD [1]                 |         |

| E_RX02                            | E_RX02_RX10                     | ch.0 RXD [2]        | Do not use           | ch.1 RXD [0]                 |         |

| E_RX03                            | E_RX03_RX11                     | ch.0 RXD [3]        | Do not use           | ch.1 RXD [1]                 |         |

| E_RXDV                            | E_RXDV0                         | ch.0 RX_DV          | ch.0 CRS_DV          | ch.0 CRS_DV                  |         |

| E_RXER                            | E_RXER0_RXDV1                   | ch.0 RX_ER          | Do not use           | ch.1 CRS_DV                  | *2      |

| E_TCK                             | E_TCK0_MDC1                     | ch.0 TX_CLK         | Do not use           | ch.1 MDC                     |         |

| E_TX00                            | E_TX00                          | ch.0 TXD [0]        | ch.0 TXD [0]         | ch.0 TXD [0]                 |         |

| E_TX01                            | E_TX01                          | ch.0 TXD [1]        | ch.0 TXD [1]         | ch.0 TXD [1]                 |         |

| E_TX02                            | E_TX02_TX10                     | ch.0 TXD [2]        | Do not use           | ch.1 TXD [0]                 |         |

| E_TX03                            | E_TX03_TX11                     | ch.0 TXD [3]        | Do not use           | ch.1 TXD [1]                 |         |

| E_TXEN                            | E_TXEN0                         | ch.0 TX_EN          | ch.0 TX_EN           | ch.0 TX_EN                   |         |

| E_TXER                            | E_TXER0_TXEN1                   | ch.0 TX_ER          | Do not use           | ch.1 TX_EN                   | *3      |

| E_CRS                             | E_CRS0                          | ch.0 CRS            | Do not use           | Do not use                   |         |

| E_COL                             | E_COL0                          | ch.0 COL            | Do not use           | Do not use                   |         |

| E_MDC                             | E_MDC0                          | ch.0 MDC            | ch.0 MDC             | ch.0 MDC                     |         |

| E_MDIO                            | E_MDIO0                         | ch.0 MDIO           | ch.0 MDIO            | ch.0 MDIO                    |         |

| -                                 | E_MDIO1                         | Do not use          | Do not use           | ch.1 MDIO                    |         |

<sup>\*1:</sup> This pin is used as RX\_CLK input in the case of MII. In the case of RMII, it is used as REF\_CLK input. If both ch.0 and ch.1 of Ethernet-MAC are used, it is common to both channels.

If both ch.0 and ch.1 of Ethernet-MAC are used, MII cannot be selected.

<sup>\*2:</sup> In the case of RMII, it is not necessary to connect it since the RX\_ER input from external PHY is not used.

<sup>\*3:</sup> In the case of MII, TX\_ER output executes, High level output is only in the LPI mode of EEE (Energy Efficient Ethernet). If EEE is not used, connection to PHY is not necessary.

## • Example of connection to external PHY

The following shows the example of connection to external PHY devices.

Although not indicated to the Figure 2-1 to Figure 2-3, it recommends connecting pull-up resistance to the MDIO signal.

Using Ethernet-MAC (ch.0) and connecting to PHY in MII mode (Figure 2-1)

Using Ethernet-MAC (ch.0) and connecting to PHY in RMII mode (Figure 2-2)

Using Ethernet-MAC (ch.0 and ch.1) and connecting to two PHYs in RMII mode (Figure 2-3)

#### • Other microcontroller external pin

Table 2-2 shows the microcontroller external pins that are other than those shown in Table 2-1 and related to Ethernet function.

Table 2-2 Other microcontroller external pin

| Microcontroller external pin name | Function                                                                                                                                                                                                   |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E_PPS0_PPS1 *                     | A pulse in each one-second of system time counter of the PTP function is output from the Ethernet-MAC block. Selection of either ch.0 output or ch.1 output can be determined by ETH_MODE.PTPSEL register. |

| E_COUT                            | A pin to output clock signals is generated by the Ethernet clock generator.                                                                                                                                |

<sup>\*:</sup> Products with only one Ethernet-MAC uses E\_PPS pin. Ch.1 output cannot be selected.

## ■ Microcontroller internal connection pin

#### System clock signal and AHB bus interface

Each Ethernet-MAC is connected to the CPU and memory via AHB bus. When using each Ethernet-MAC, the AHB clock (HCLK) must be set to more than 25 MHz.

The AHB clock (HCLK) is connected to the source clock (PTP\_CLK) of the system time counter of each Ethernet-MAC.

#### • Interrupt signal interface

Interrupt signals output from each Ethernet-MAC block are shown in Table 2-3. These interrupts are connected to NVIC. For these interrupts, see the chapter "Interrupts" in "PERIPHERAL MANUAL".

Table 2-3 Interrupt signal from Ethernet-MAC

| Interrupt signal name | Function                                                                                    |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------|--|--|--|

| MAC0_INT_SBD          | The interrupt asserted along with the end of DMAC processing of Ethernet-MAC ch.0.          |  |  |  |

| MAC0_INT_PMT          | The interrupt asserted when valid WAKE-UP frame reception of Ethernet-MAC ch.0 is detected. |  |  |  |

| MAC0_INT_LPI          | The interrupt asserted when Ethernet-MAC ch.0 ends LPI state.                               |  |  |  |

| MAC1_INT_SBD          | The interrupt asserted along with the end of DMAC processing of Ethernet-MAC ch.1.          |  |  |  |

| MAC1_INT_PMT          | The interrupt asserted when valid WAKE-UP frame reception of Ethernet-MAC ch.1 is detected. |  |  |  |

Ethernet-MAC ch.1 generates no LPI interrupts since it does not have MII mode.

## 3. Ethernet-MAC Setup Control Procedure

This section describes the Ethernet-MAC setup control procedure.

### ■ About the setup

After selecting the I/O port block, execute the following procedure to set up each Ethernet-MAC. It includes clock supply to each Ethernet-MAC, selection of MII/RMII mode, and issue/release of hardware reset to each Ethernet-MAC. After the setup is completed, execute the initial setting for each Ethernet-MAC to start operation.

#### ■ Procedure when MII mode is selected

- 1. Write ETH\_CLKG.MACEN0 = 1 and ETH\_CLKG.MACEN1 = 0. Start clock supply to Ethernet-MAC (ch.0).

- 2. Write ETH\_MODE.IFMODE = 0, ETH\_MODE.RST0 = 1, and ETH\_MODE.RST1 = 0. Select MII and issue a hardware reset to Ehernet-MAC (ch.0).

- 3. At this point, clock signals (RX\_CLK and TX\_CLK) must be input from external PHY. If the clock signals have not been input, wait until they are input.

- 4. Write ETH\_MODE.IFMODE = 0, ETH\_MODE.RST0 = 0, and ETH\_MODE.RST1 = 0. Select MII and release a hardware reset of Ethernet-MAC (ch.0).

#### ■ Procedure when RMII mode (using only ch.0) is selected

- 1. Write ETH\_CLKG.MACEN0 = 1, ETH\_CLKG.MACEN1 = 0. Start clock supply to Ethernet-MAC (ch.0).

- 2. Write ETH\_MODE.IFMODE = 1, ETH\_MODE.RST0 = 1, and ETH\_MODE.RST1 = 0. Select RMII and issue a hardware reset to Ethernet-MAC (ch.0).

- 3. At this point, clock signal (REF\_CLK) must be input from external PHY. If the clock signal has not been input, wait until it is input.

- 4. Write ETH\_MODE.IFMODE = 1, ETH\_MODE.RST0 = 0, and ETH\_MODE.RST1 = 0. Select RMII and release a hardware reset of Ethernet-MAC (ch.0).

### ■ Procedure when RMII mode (using both ch.0 and ch.1) is selected

- 1. Write ETH\_CLKG.MACEN0 = 1 and ETH\_CLKG.MACEN1 = 1. Start clock supply to Ethernet-MAC (ch.0 and ch.1).

- 2. Write ETH\_MODE.IFMODE = 1, ETH\_MODE.RST0 = 1, and ETH\_MODE.RST1 = 1. Select RMII and issue a hardware reset to Ethernet-MAC (ch.0 and ch.1).

- 3. At this point, clock signal (REF\_CLK) must be input from external PHY. If the clock signal has not been input, wait until it is input.

- 4. Write ETH\_MODE.IFMODE = 1, ETH\_MODE.RST0 = 0, and ETH\_MODE.RST1 = 0. Select RMII and release a hardware reset of Ethernet-MAC (ch.0 and ch.1).

- \* : ETH\_MODE.PTPSEL can be selected arbitrarily according to the channel of the PTP signal being output.

## 4. Ethernet System Control Block Register

This section describes Ethernet system control block registers.

Table 4-1 shows the list of Ethernet system control block registers.

Table 4-1 Ethernet system control block register list

| Offset address | Register abbreviation | Register name         | Reference |

|----------------|-----------------------|-----------------------|-----------|

| 0x00           | ETH_MODE              | Mode select register  | 4.1       |

| 0x08           | ETH_CLKG              | Clock gating register | 4.2       |

Ethernet system control block base address: 0x40066000

## 4.1. Mode Select Register (ETH\_MODE)

ETH\_MODE controls the external interface mode of Ethernet.

| Register  | confid | uration |

|-----------|--------|---------|

| i/cuistei | COLLIN | ulalion |

| i coming | diation               |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31       | 30                    | 29                                                                                                                                                                                                                                                             | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          | Reserved              |                                                                                                                                                                                                                                                                | PPSSEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | erved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| R        | R                     | R                                                                                                                                                                                                                                                              | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0        | 0                     | 0                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |                       |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 23       | 22                    | 21                                                                                                                                                                                                                                                             | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |                       |                                                                                                                                                                                                                                                                | Resei                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| R        | R                     | R                                                                                                                                                                                                                                                              | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |