## STM32F042xx Errata sheet

## STM32F042xx device limitations

## Silicon identification

This errata sheet applies to revision 'A' of the STMicroelectronics STM32F042xx products. The STM32F042xx family features an ARM® 32-bit Cortex®-M0 core.

Section 1 gives a detailed description of the product silicon limitations.

The full list of part numbers is shown in *Table 2*. The products are identifiable by the revision code marked below the order code on the device package, as shown in *Table 1*.

Table 1. Device identification<sup>(1)</sup>

| Sales type  | Revision code marked on the device <sup>(2)</sup> |

|-------------|---------------------------------------------------|

| STM32F042xx | 'A'                                               |

- The REV\_ID bits in the DBGMCU\_IDCODE register show the revision code of the device (see the reference manual RM0091 for details on how to find the revision code).

- 2. Refer to *Appendix A: Revision code on device marking* for details on how to identify the revision code according to the packages.

**Table 2. Device summary**

| Reference   | Part numbers                                                                                                                   |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| STM32F042xx | STM32F042F4, STM32F042G4,STM32F042K4, STM32F042T4,STM32F042C4<br>STM32F042F6, STM32F042G6,STM32F042K6, STM32F042T6,STM32F042C6 |  |

March 2014 DocID025951 Rev 1 1/11

Contents STM32F042xx

## **Contents**

| 1                                   | STM3                                        | 2F042x     | x silicon limitations                                                                        | 3 |

|-------------------------------------|---------------------------------------------|------------|----------------------------------------------------------------------------------------------|---|

|                                     | 1.1                                         | System     | limitations                                                                                  | 4 |

|                                     |                                             | 1.1.1      | Wakeup sequence from Standby mode when using more than one wakeup source                     | 4 |

| 1.2                                 |                                             | USART      | peripheral limitation                                                                        | 4 |

|                                     |                                             | 1.2.1      | Last byte written in TDR might not be transmitted if TE is cleared just after writing in TDR | 4 |

|                                     | 1.3 GPIO peripheral limitation              |            | eripheral limitation                                                                         | 5 |

|                                     |                                             | 1.3.1      | GPIOx locking mechanism not working properly for GPIOx_OTYPER register                       | 5 |

| 1.4 SPI/I <sup>2</sup> S limitation |                                             | limitation | 5                                                                                            |   |

|                                     |                                             | 1.4.1      | In $I^2S$ slave mode: WS level must be set by the external master when enabling the $I^2S$   | 5 |

|                                     | 1.5 I <sup>2</sup> C peripheral limitations |            | pheral limitations                                                                           | 5 |

|                                     |                                             | 1.5.1      | Wrong behaviors in Stop mode when wakeup from Stop mode is disabled in I <sup>2</sup> C      | 5 |

| 1.6 USB peripheral limitation       |                                             | USB pe     | ripheral limitation                                                                          | 6 |

|                                     |                                             | 1.6.1      | The USB BCD functionality limited below -20°C                                                | 6 |

| Appendix                            | A Re                                        | evision    | code on device marking                                                                       | 7 |

| Revision                            | history                                     | /          |                                                                                              | 0 |

## 1 STM32F042xx silicon limitations

*Table 3* gives quick references to all documented limitations.

Legend for *Table 3*: A = workaround available; N = no workaround available; P = partial workaround available, '-' and grayed = fixed.

Table 3. Summary of silicon limitations

| Section                                              | Limitation                                                                                                  | Rev A |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------|

| Section 1.1: System limitations                      | Section 1.1.1: Wakeup sequence from Standby mode when using more than one wakeup source                     | Α     |

| Section 1.2: USART peripheral limitation             | Section 1.2.1: Last byte written in TDR might not be transmitted if TE is cleared just after writing in TDR | Α     |

| Section 1.3: GPIO peripheral limitation              | Chapter 1.3.1: GPIOx locking mechanism not working properly for GPIOx_OTYPER register                       | Р     |

| Section 1.4: SPI/I <sup>2</sup> S<br>limitation      | Section 1.4.1: In $I^2S$ slave mode: WS level must be set by the external master when enabling the $I^2S$   | Α     |

| Section 1.5: I <sup>2</sup> C peripheral limitations | Section 1.5.1: Wrong behaviors in Stop mode when wakeup from Stop mode is disabled in I <sup>2</sup> C      | Α     |

| Section 1.6: USB peripheral limitation               | Section 1.6.1: The USB BCD functionality limited below - 20°C                                               | N     |

## 1.1 System limitations

# 1.1.1 Wakeup sequence from Standby mode when using more than one wakeup source

### **Description**

The various wakeup sources are logically OR-ed in front of the rising-edge detector which generates the wakeup flag (WUF). The WUF needs to be cleared prior to Standby mode entry, otherwise the MCU wakes up immediately.

If one of the configured wakeup sources is kept high during the clearing of the WUF (by setting the CWUF bit), it may mask further wakeup events on the input of the edge detector. As a consequence, the MCU might not be able to wake up from Standby mode.

#### Workaround

To avoid this problem, the following sequence should be applied before entering Standby mode:

- Disable all used wakeup sources,

- Clear all related wakeup flags,

- Re-enable all used wakeup sources,

- Enter Standby mode

Note:

Be aware that, when applying this workaround, if one of the wakeup sources is still kept high, the MCU will enter Standby mode but then it wakes up immediately generating a power reset.

## 1.2 USART peripheral limitation

# 1.2.1 Last byte written in TDR might not be transmitted if TE is cleared just after writing in TDR

## **Description**

If the USART clock source is slow (for example LSE) and TE bit is cleared immediately after the last write to TDR, the last byte will probably not be transmitted.

### Workarounds

- 1. Wait until TXE flag is set before clearing TE bit.

- 2. Wait until TC flag is set before clearing TE bit.

57/

## 1.3 **GPIO** peripheral limitation

# 1.3.1 GPIOx locking mechanism not working properly for GPIOx\_OTYPER register

## **Description**

Locking of GPIOx\_OTYPER[i] with i = 15...8 depends from setting of GPIOx\_LCKR[i-8] and not from GPIOx\_LCKR[i]. GPIOx\_LCKR[i-8] is locking GPIOx\_OTYPER[i] together with GPIOx\_OTYPER[i-8]. It is not possible to lock GPIOx\_OTYPER[i] with i = 15...8, without also locking GPIOx\_OTYPER[i-8].

#### Workaround

The only way to lock GPIOxOTYPER[i] with i=15...8 is to also lock GPIOxOTYPER[i-8].

## 1.4 SPI/I<sup>2</sup>S limitation

# 1.4.1 In I<sup>2</sup>S slave mode: WS level must be set by the external master when enabling the I<sup>2</sup>S

### **Description**

In slave mode, the WS signal level is used only to start the communication. If the  $I^2S$  (in slave mode) is enabled while the master is already sending the clock and the WS signal level is low (for  $I^2S$  protocol) or is high (for the LSB or MSB-justified mode), the slave starts communicating data immediately. In this case, the master and slave will be desynchronized throughout the whole communication.

#### Workaround

The I<sup>2</sup>S peripheral must be enabled when the external master sets the WS line at:

- High level when the I<sup>2</sup>S protocol is selected.

- Low level when the LSB or MSB-justified mode is selected.

## 1.5 I<sup>2</sup>C peripheral limitations

# 1.5.1 Wrong behaviors in Stop mode when wakeup from Stop mode is disabled in I<sup>2</sup>C

### **Description**

When wakeup from Stop mode is disabled in  $I^2C$  (WUPEN = 0) and the MCU enters Stop mode while a transfer is on going on the bus, some wrong behavior may happen:

- BUSY flag can be wrongly set when the MCU exits Stop mode. This prevents from initiating a transfer in master mode, as the START condition cannot be sent when BUSY is set.

- 2. If clock stretching is enabled (NOSTRETCH = 0), the I<sup>2</sup>C clock SCL may be stretched low by the I<sup>2</sup>C as long as the MCU is in Stop mode. This limitation may occur when the Stop mode is entered during the address phase of a transfer on the I<sup>2</sup>C bus while SCL = 0. Therefore the transfer may be stalled as long as the MCU is in Stop mode. The probability of the occurrence depends also on the timings configuration, the peripheral clock frequency and the I<sup>2</sup>C bus frequency.

These behaviors can occur in Slave mode and in Master mode in a multi-master topology.

#### Workaround

Disable the I<sup>2</sup>C (PE=0) before entering Stop mode and re-enable it in Run mode.

## 1.6 USB peripheral limitation

## 1.6.1 The USB BCD functionality limited below -20°C

### **Description**

Primary and secondary detection can return an incorrectly detected port type.

This limitation may be observed on a small number of devices when the temperature is below -20°C.

#### Workaround

None.

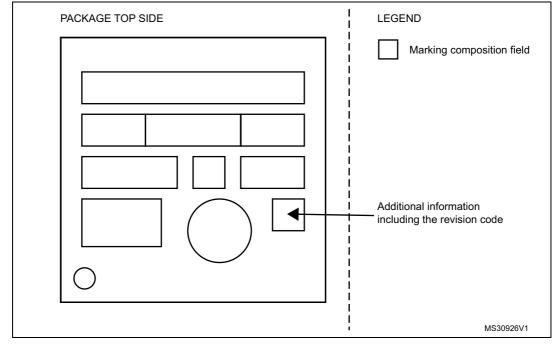

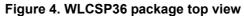

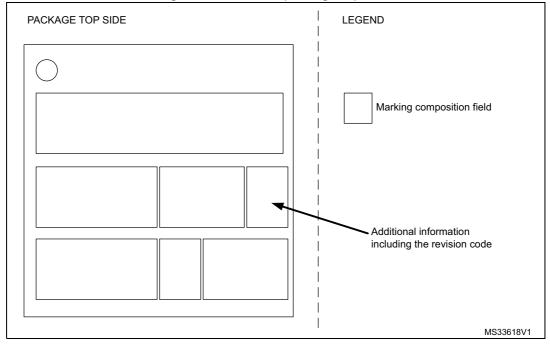

## Appendix A Revision code on device marking

The following figures show the standard marking compositions for the LQFP48, LQFP32, UFQFPN48, UFQFPN32, UFQFPN28, WLCSP36 and TSSOP20 packages, respectively. Only the Additional information field containing the revision code is shown.

PACKAGE TOP SIDE

LEGEND

Marking composition field

Additional information including the revision code

Figure 1. LQFP48 and UFQFPN48 packages top view

PACKAGE TOP SIDE LEGEND Marking composition field Additional information including the revision code MS32139V1

Figure 3. UFQFPN28 package top view

PACKAGE TOP SIDE

LEGEND

Marking composition field

Additional information including the revision code

Figure 5. TSSOP20 package top view

Revision history STM32F042xx

# **Revision history**

**Table 4. Document revision history**

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 11-Mar-2014 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2014 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com