# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### Cautions

Keep safety first in your circuit designs!

- Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but

there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire

or property damage.

- Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation

product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any

other rights, belonging to Renesas Technology Corporation or a third party.

- Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors.

- Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these

materials

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

# Hitachi Microcomputer H8/300H Series Application Notes for CPU

# RENESAS

# **Notice**

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- Hitachi will not be held responsible for any damage to the user that may result from

accidents or any other reasons during operation of the user's unit according to this

document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

# Contents

| Sect | ion 1    | CPU Architecture                                                | 1  |

|------|----------|-----------------------------------------------------------------|----|

| 1.1  | Introdu  | action                                                          | 1  |

|      | 1.1.1    | Features                                                        | 1  |

|      | 1.1.2    | Register Configuration                                          | 2  |

|      | 1.1.3    | Data Configuration                                              | 4  |

|      | 1.1.4    | Address Space                                                   | 6  |

|      | 1.1.5    | Addressing Mode                                                 | 7  |

|      | 1.1.6    | Instructions                                                    | 16 |

| Sect | ion 2    | Instructions                                                    | 17 |

| 2.1  |          | ransfer Instructions                                            | 17 |

| 2.1  | 2.1.1    | MOV                                                             | 17 |

|      | 2.1.2    | PUSH, POP                                                       | 19 |

| 2.2  |          | etic Operation Instructions                                     | 21 |

|      | 2.2.1    | ADD, SUB                                                        | 21 |

|      | 2.2.2    | ADDX, SUBX                                                      | 22 |

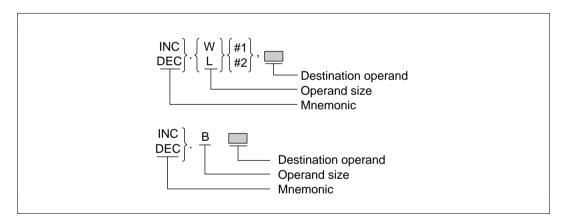

|      | 2.2.3    | INC, DEC                                                        | 23 |

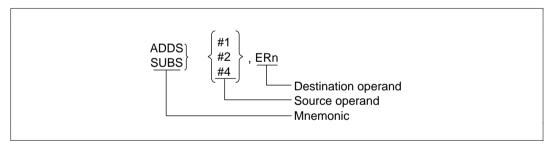

|      | 2.2.4    | ADDS, SUBS                                                      | 24 |

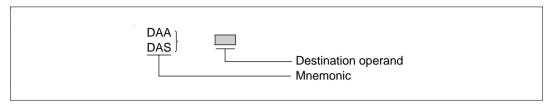

|      | 2.2.5    | DAA, DAS                                                        | 25 |

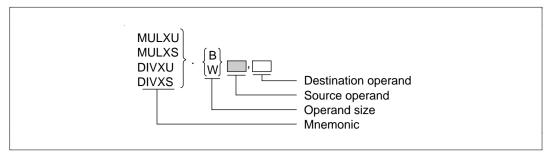

|      | 2.2.6    | MULXU, DIVXU, MULXS, DIVXS                                      | 25 |

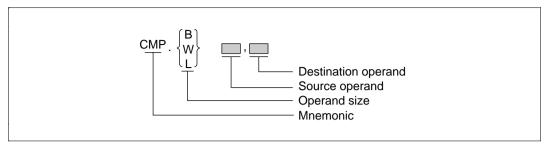

|      | 2.2.7    | CMP                                                             | 27 |

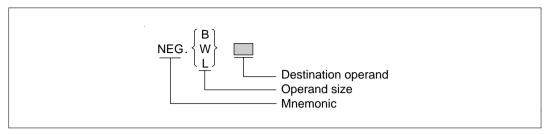

|      | 2.2.8    | NEG                                                             | 28 |

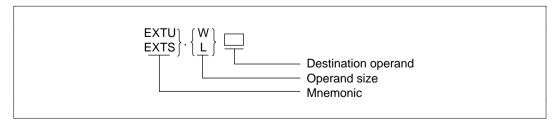

|      | 2.2.9    | EXTS, EXTU                                                      | 28 |

| 2.3  | Logic (  | Operation Instructions                                          | 30 |

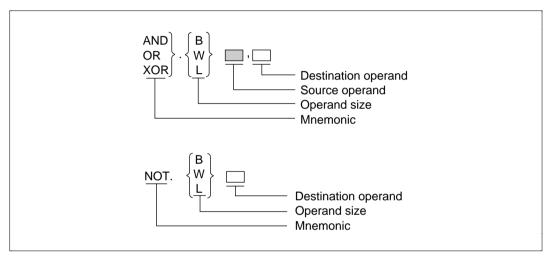

|      | 2.3.1    | AND, OR, XOR, NOT                                               | 30 |

| 2.4  | Shift In | nstructions                                                     | 32 |

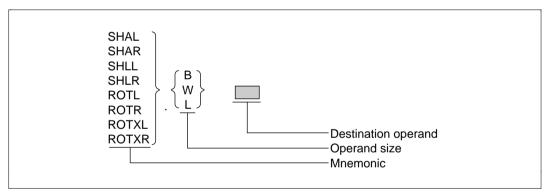

|      | 2.4.1    | SHAL, SHAR, SHLL, SHLR, ROTL, ROTR, ROTXL, ROTXR                | 32 |

| 2.5  | Bit Ma   | nipulation Instructions                                         | 34 |

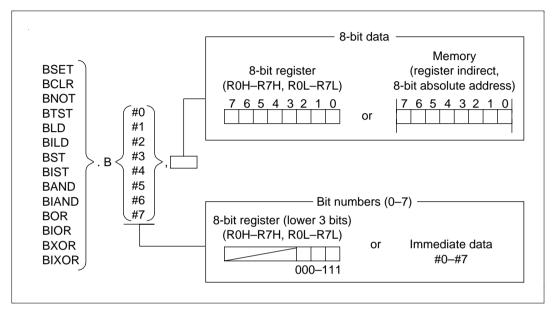

|      | 2.5.1    | BSET, BCLR, BNOT, BTST, BLD, BILD, BST, BIST, BAND, BIAND, BOR, |    |

|      | BIOR,    | BXOR, BIXOR                                                     | 34 |

| 2.6  | Branch   | Instructions                                                    | 36 |

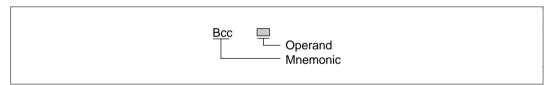

|      | 2.6.1    | Bcc                                                             | 36 |

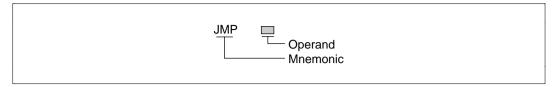

|      | 2.6.2    | JMP                                                             | 38 |

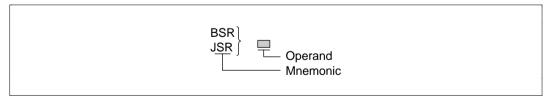

|      | 2.6.3    | BSR, JSR                                                        | 38 |

|      | 2.6.4    | RTS                                                             | 40 |

| 2.7  | System   | Control Instructions                                            | 41 |

|      | 2.7.1    | RTE                                                             | 41 |

|      | 2.7.2    | SLEEP                                                           | 41 |

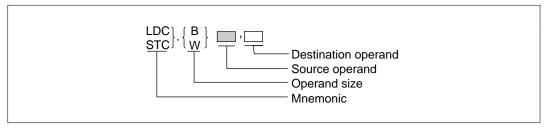

|      | 2.7.3    | LDC, STC                                                        | 42 |

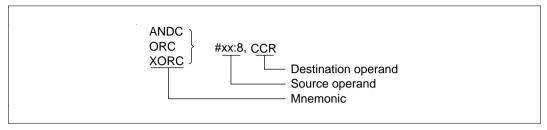

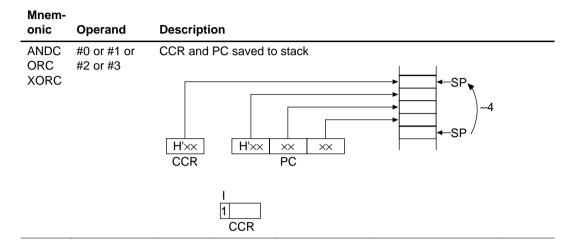

|      | 2.7.4    | ANDC, ORC, XORC                                                 | 43 |

|      |          |                                                                 |    |

|       | 2.7.5 | NOP                                        | 44  |

|-------|-------|--------------------------------------------|-----|

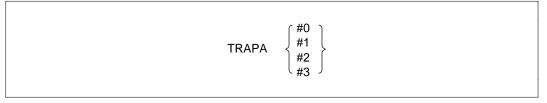

|       | 2.7.6 | TRAPA                                      | 44  |

| 2.8   | Block | Transfer Instructions                      | 45  |

|       | 2.8.1 | EEPMOV                                     | 45  |

|       |       |                                            |     |

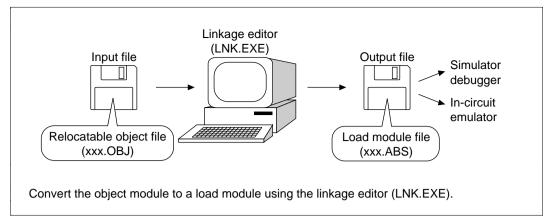

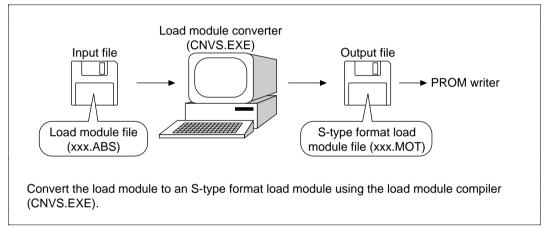

| Secti | ion 3 | Load Module Conversion Procedures          | 47  |

|       |       |                                            |     |

|       |       | Examples of Software Applications          | 49  |

| 4.1   |       | are Applications Examples                  | 49  |

| 4.2   |       | Software Examples                          | 50  |

|       | 4.2.1 | Program Listing Page Format (Format 4)     | 51  |

| 4.3   | Block | Transfer                                   | 52  |

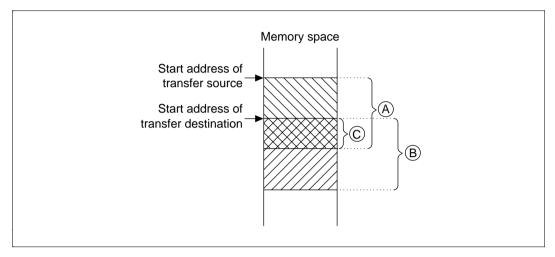

|       | 4.3.1 | Description of Functions                   | 54  |

|       | 4.3.2 | Cautions for Use                           | 56  |

|       | 4.3.3 | Description of Data Memory                 | 56  |

|       | 4.3.4 | Examples of Use                            | 57  |

|       | 4.3.5 | Principles of Operation                    | 57  |

|       | 4.3.6 | Program Listing                            | 59  |

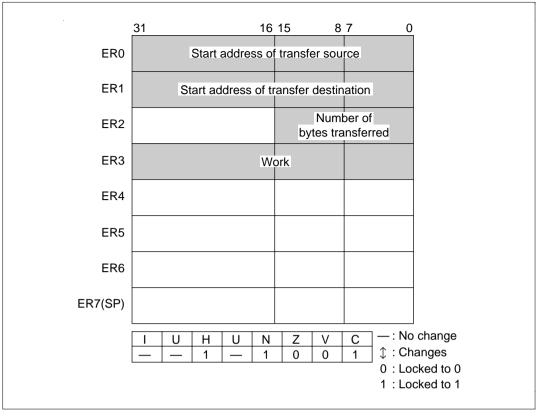

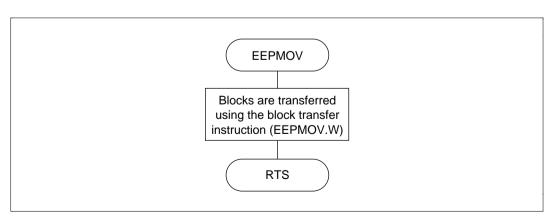

| 4.4   | Block | Transfer Using Block Transfer Instruction  | 60  |

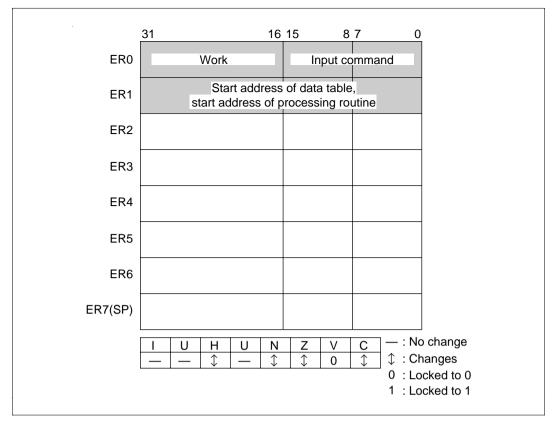

|       | 4.4.1 | Description of Functions                   | 63  |

|       | 4.4.2 | Cautions for Use                           | 64  |

|       | 4.4.3 | Description of Data Memory                 | 64  |

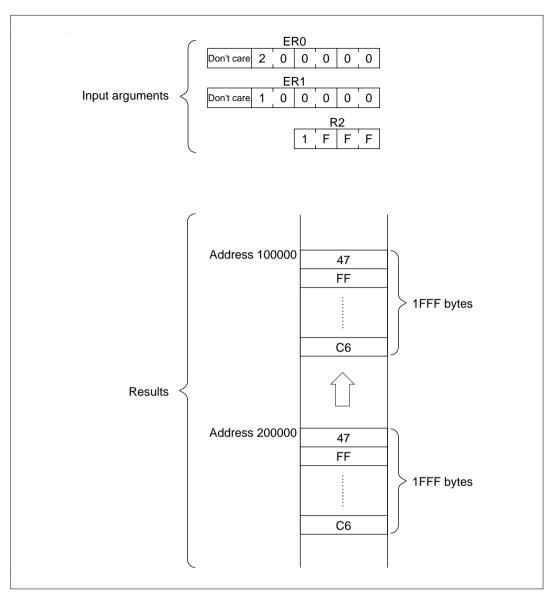

|       | 4.4.4 | Examples of Use                            | 65  |

|       | 4.4.5 | Principles of Operation                    | 65  |

|       | 4.4.6 | Program Listing                            | 66  |

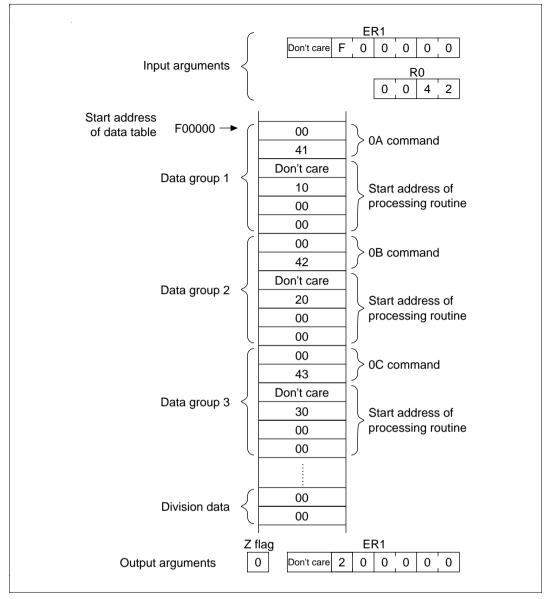

| 4.5   | Branc | hing Using a Table                         | 67  |

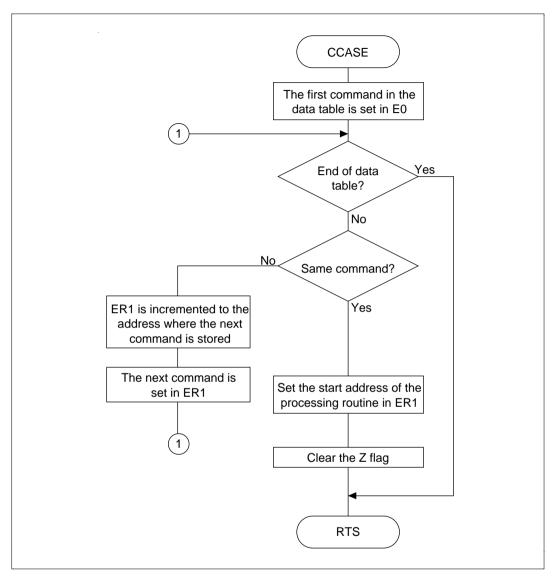

|       | 4.5.1 | Description of Functions                   | 69  |

|       | 4.5.2 | Cautions for Use                           | 70  |

|       | 4.5.3 | Description of Data Memory                 | 70  |

|       | 4.5.4 | Examples of Use                            | 71  |

|       | 4.5.5 | Principles of Operation                    | 72  |

|       | 4.5.6 | Program Listing                            | 74  |

| 4.6   | Count | ing the Number of Logical 1s in 8-Bit Data | 75  |

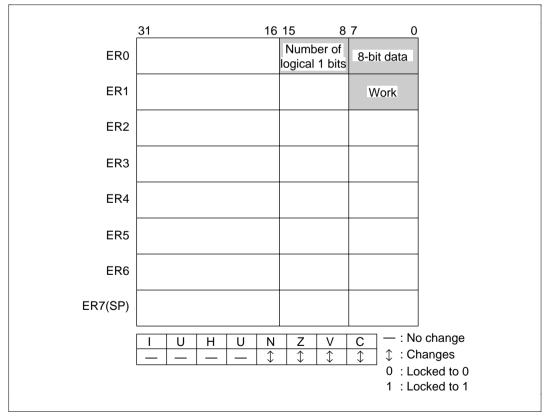

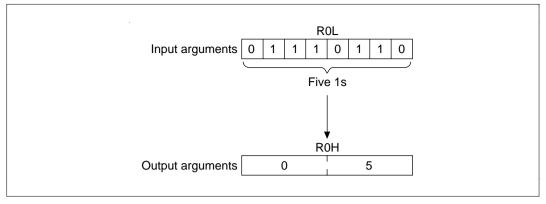

|       | 4.6.1 | Description of Functions                   | 76  |

|       | 4.6.2 | Cautions for Use                           | 77  |

|       | 4.6.3 | Description of Data Memory                 | 77  |

|       | 4.6.4 | Examples of Use                            | 77  |

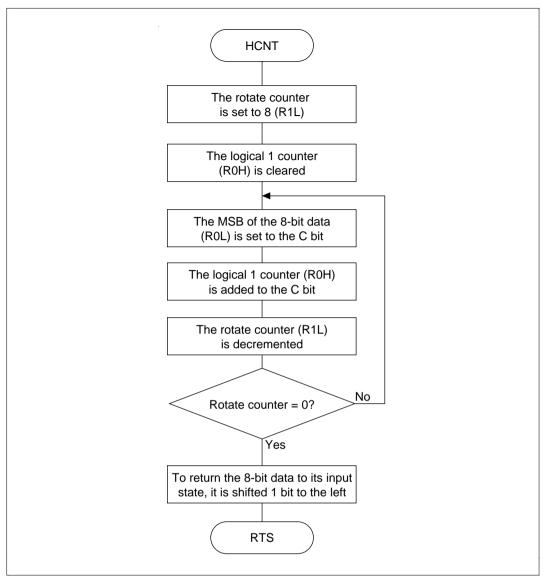

|       | 4.6.5 | Principles of Operation                    | 78  |

|       | 4.6.6 | Program Listing                            | 80  |

| 4.7   |       | he First 1 in 32-Bit Data.                 | 81  |

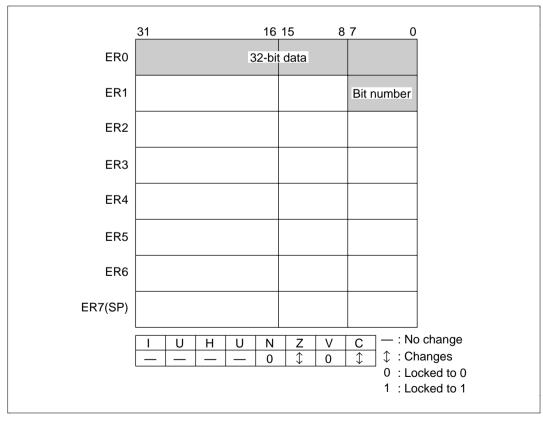

|       | 4.7.1 | Description of Functions                   | 83  |

|       | 4.7.2 | Cautions for Use                           | 83  |

|       | 4.7.3 | Description of Data Memory                 | 83  |

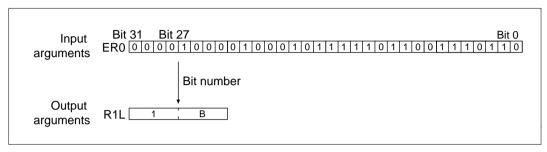

|       | 1.7.5 | Description of Data Memory                 | 0.5 |

|      | 4.7.4  | Examples of Use                 | 84  |

|------|--------|---------------------------------|-----|

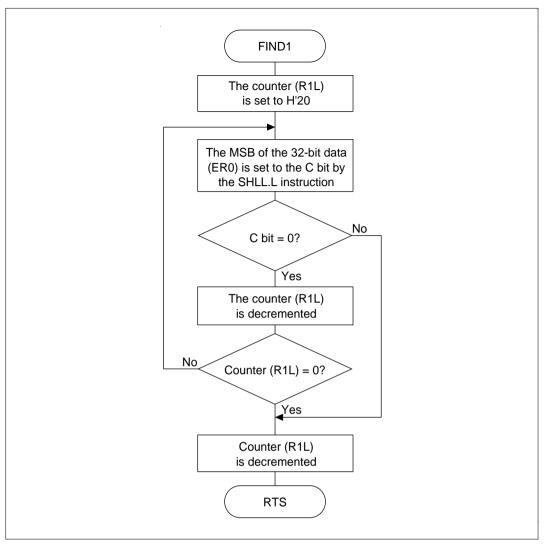

|      | 4.7.5  | Principles of Operation         | 84  |

|      | 4.7.6  | Program Listing                 | 86  |

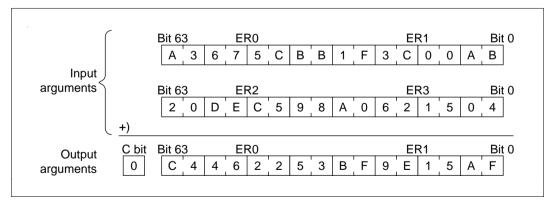

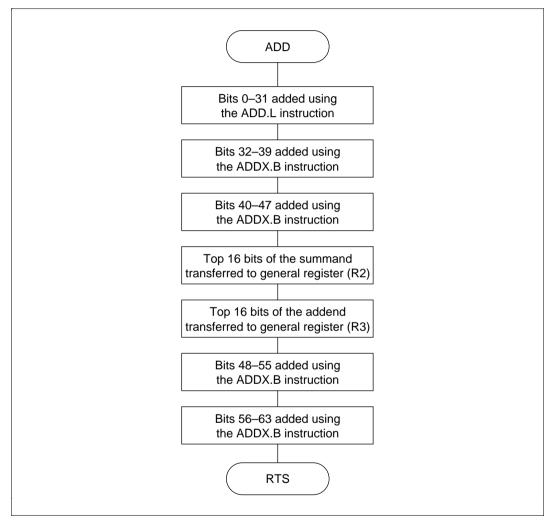

| 4.8  | 64-Bit | Binary Addition                 | 87  |

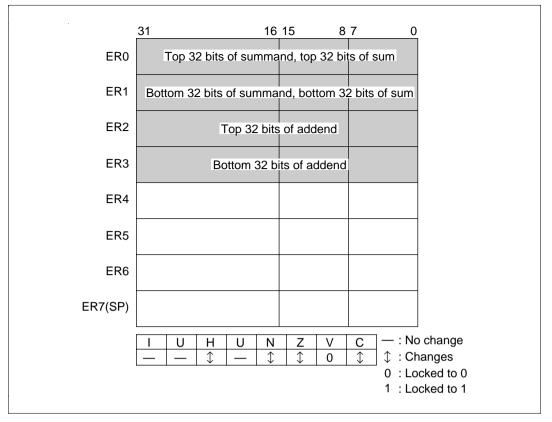

|      | 4.8.1  | Description of Functions        | 90  |

|      | 4.8.2  | Cautions for Use                |     |

|      | 4.8.3  | Description of Data Memory      |     |

|      | 4.8.4  | Examples of Use                 | 91  |

|      | 4.8.5  | Principles of Operation         | 92  |

|      | 4.8.6  | Program Listing                 | 93  |

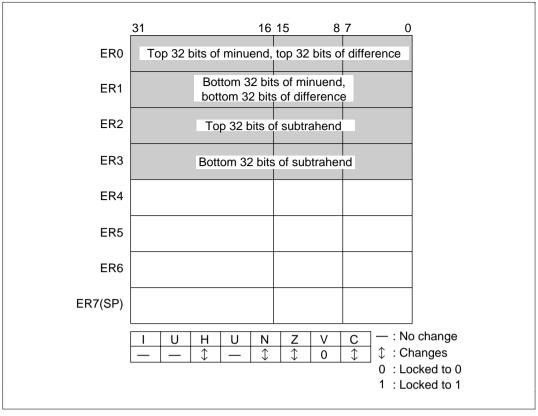

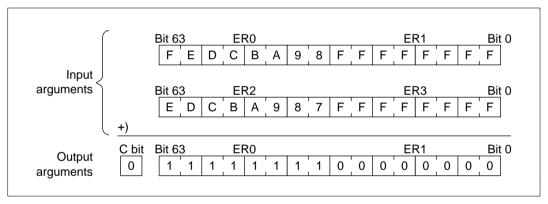

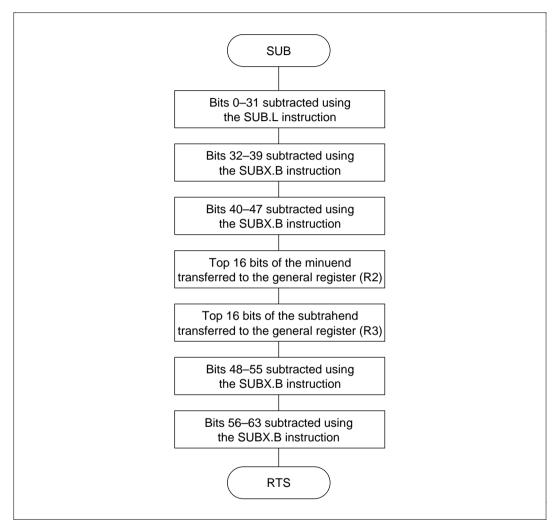

| 4.9  | 64-Bit | Binary Subtraction              | 94  |

|      | 4.9.1  | Description of Functions        | 97  |

|      | 4.9.2  | Cautions for Use                | 97  |

|      | 4.9.3  | Description of Data Memory      | 97  |

|      | 4.9.4  | Examples of Use                 | 98  |

|      | 4.9.5  | Principles of operation         | 99  |

|      | 4.9.6  | Program Listing                 | 100 |

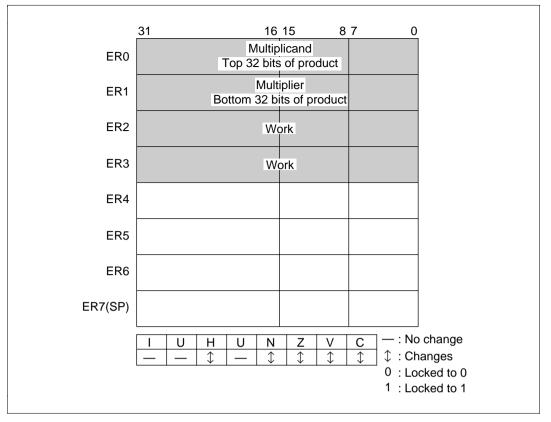

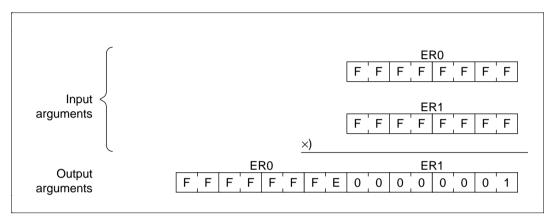

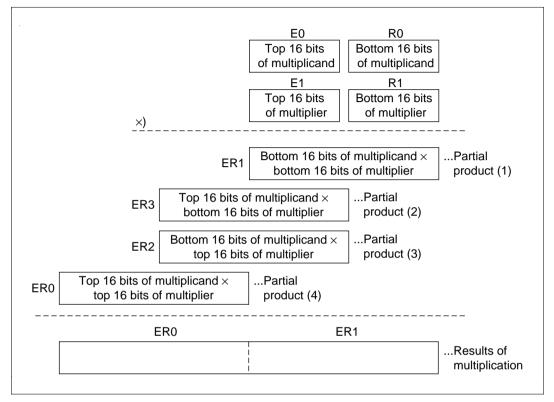

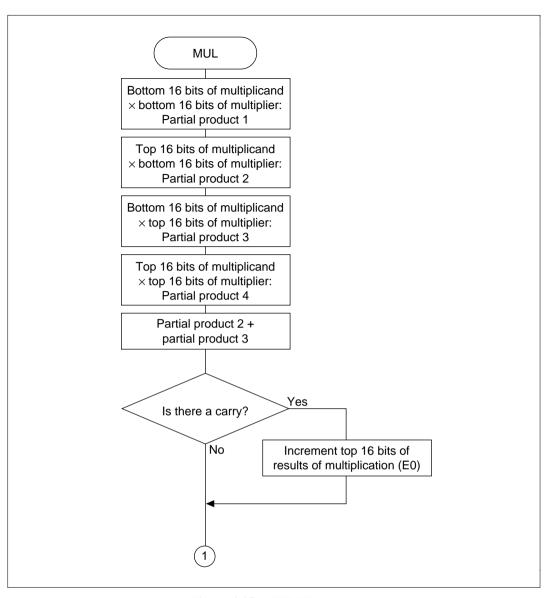

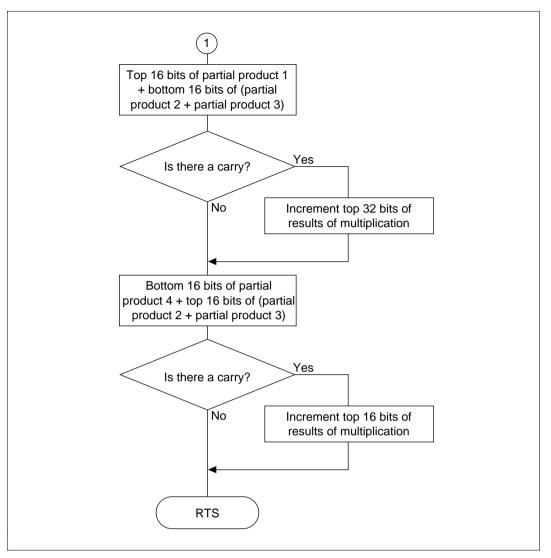

| 4.10 | Unsign | ed 32-Bit Binary Multiplication | 101 |

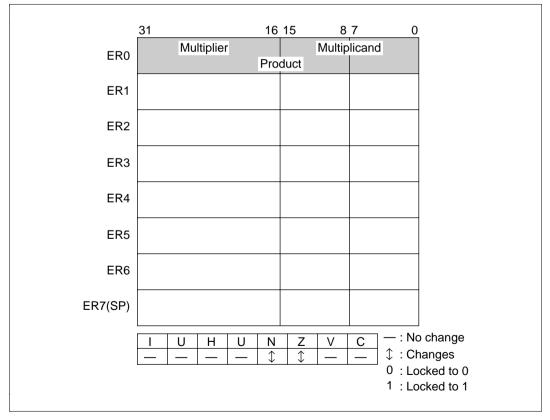

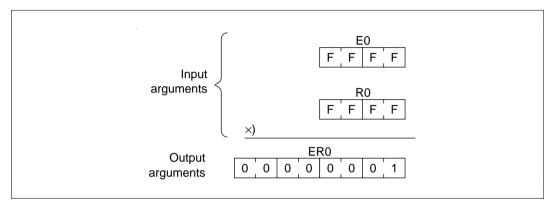

|      | 4.10.1 | Description of functions        | 104 |

|      | 4.10.2 | Cautions for Use                | 104 |

|      | 4.10.3 | Description of Data Memory      | 104 |

|      | 4.10.4 | Examples of Use                 | 105 |

|      | 4.10.5 | Principles of Operation         | 106 |

|      | 4.10.6 | Program Listing                 | 109 |

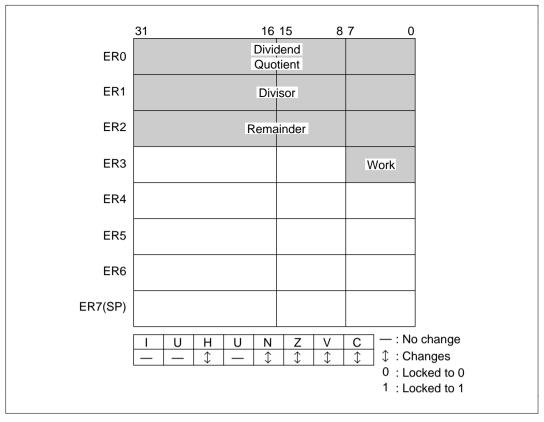

| 4.11 | Unsign | ed 32-Bit Binary Division       | 110 |

|      | 4.11.1 | Description of Functions        | 113 |

|      | 4.11.2 | Cautions for Use                | 113 |

|      | 4.11.3 | Description of Data Memory      | 113 |

|      | 4.11.4 | Examples of Use                 | 114 |

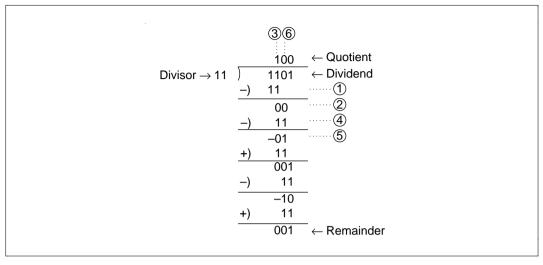

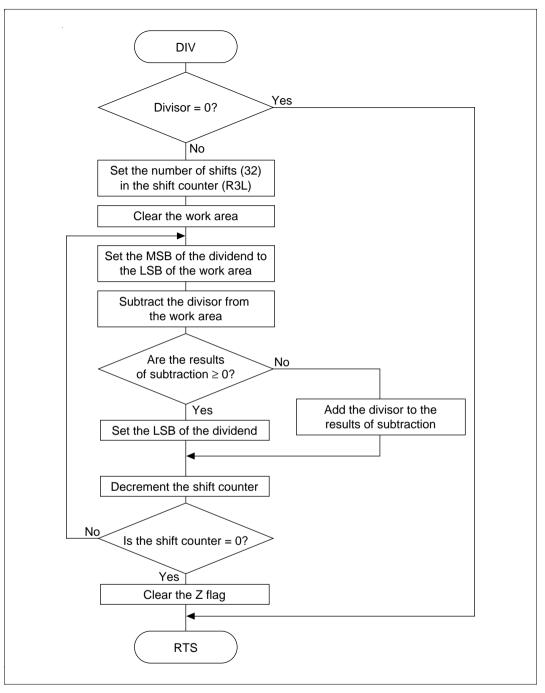

|      | 4.11.5 | Principles of Operation.        | 115 |

|      | 4.11.6 | Program Listing                 | 117 |

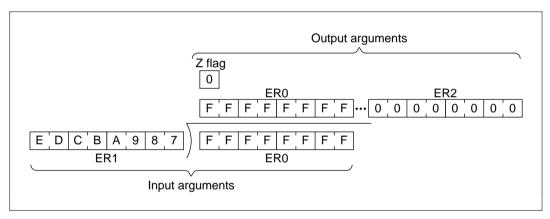

| 4.12 |        | 16-Bit Binary Multiplication    |     |

|      |        | Description of Functions        |     |

|      |        | Cautions for Use                |     |

|      | 4.12.3 | Description of Data Memory      | 120 |

|      | 4.12.4 | Examples of Use                 | 121 |

|      | 4.12.5 | Principles of Operation.        | 121 |

|      | 4.12.6 | Program Listing                 | 122 |

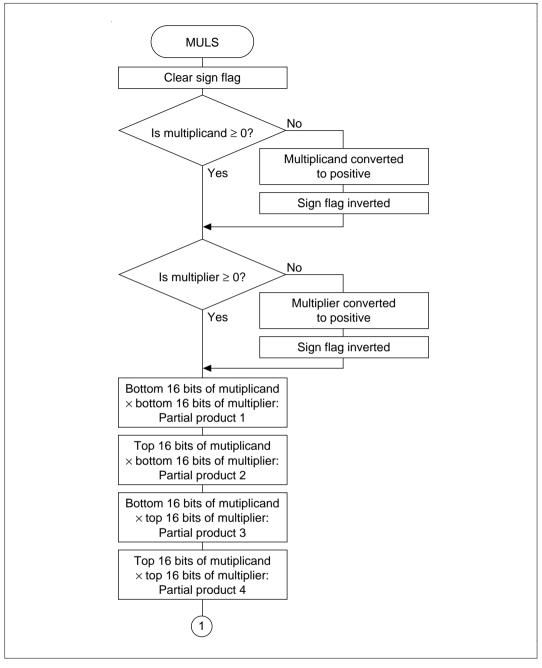

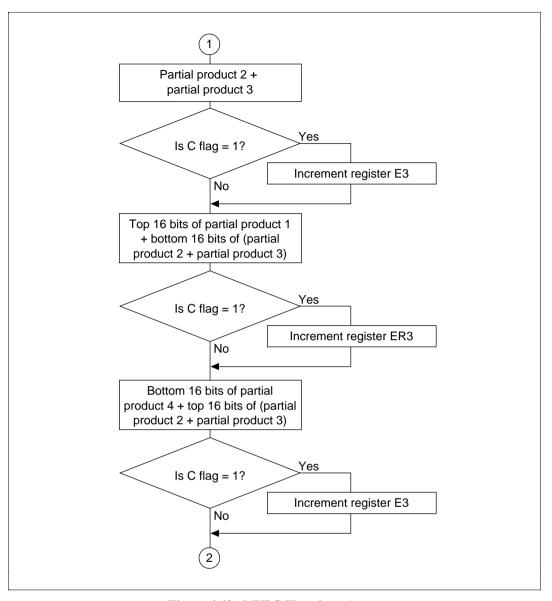

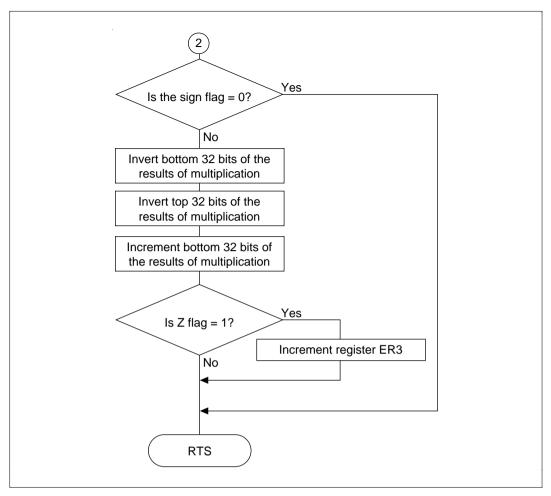

| 4.13 | _      | 32-Bit Binary Multiplication    |     |

|      |        | Description of Functions        |     |

|      |        | Cautions for Use                |     |

|      |        | Description of Data Memory      |     |

|      | 4.13.4 | Examples of Use                 | 127 |

|      | 4.13.5  | Principles of Operation                 | 128 |

|------|---------|-----------------------------------------|-----|

|      | 4.13.6  | Program Listing                         | 132 |

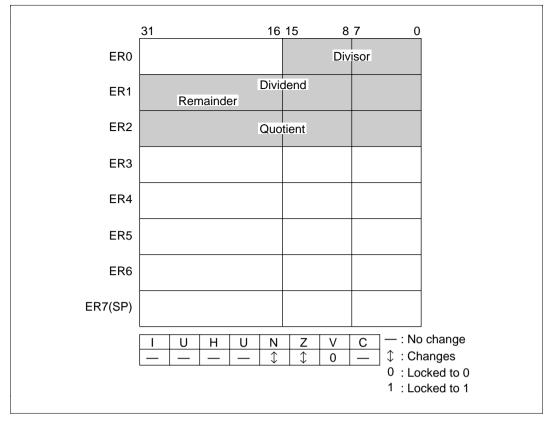

| 4.14 | Signed  | 32-Bit Binary Division (16-Bit Divisor) | 133 |

|      | 4.14.1  | Description of Functions                | 136 |

|      | 4.14.2  | Cautions for Use                        | 136 |

|      | 4.14.3  | Description of Data Memory              | 136 |

|      | 4.14.4  | Examples of Use                         | 137 |

|      | 4.14.5  | Principles of Operation.                | 137 |

|      | 4.14.6  | Program Listing                         | 140 |

| 4.15 | Signed  | 32-Bit Binary Division (32-Bit Divisor) | 141 |

|      | 4.15.1  | Description of Functions                | 144 |

|      | 4.15.2  | Cautions for Use                        | 144 |

|      | 4.15.3  | Description of Data Memory              | 144 |

|      | 4.15.4  | Examples of Use                         | 145 |

|      | 4.15.5  | Principles of Operation                 | 146 |

|      | 4.15.6  | Program Listing                         | 147 |

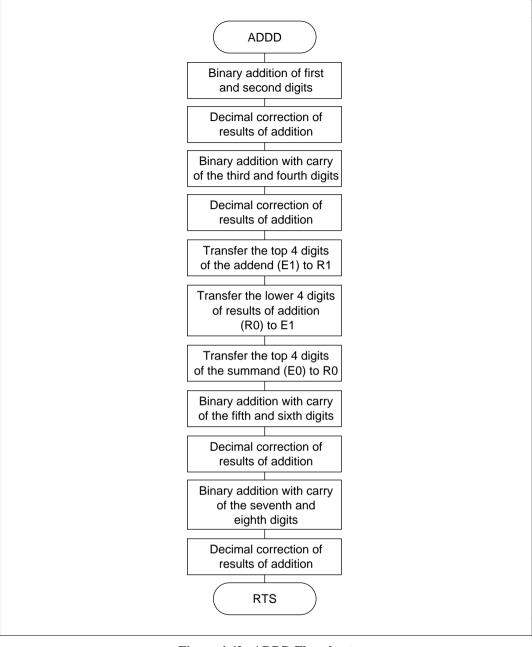

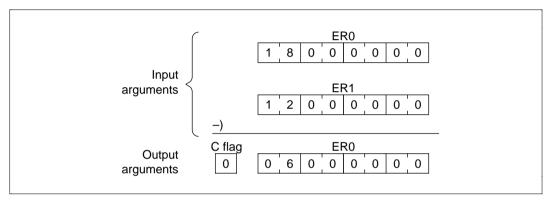

| 4.16 | 8-Digit | Decimal Addition                        | 148 |

|      | 4.16.1  | Description of Functions                | 151 |

|      | 4.16.2  | Cautions for Use                        | 151 |

|      | 4.16.3  | Description of Data Memory              | 151 |

|      | 4.16.4  | Examples of Use                         | 152 |

|      | 4.16.5  | Principles of Operation                 | 152 |

|      | 4.16.6  | Program Listing                         | 154 |

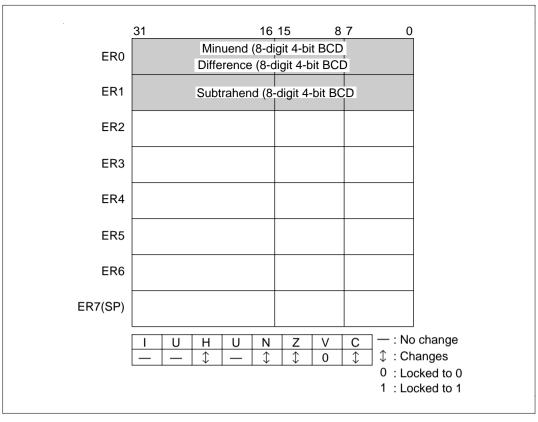

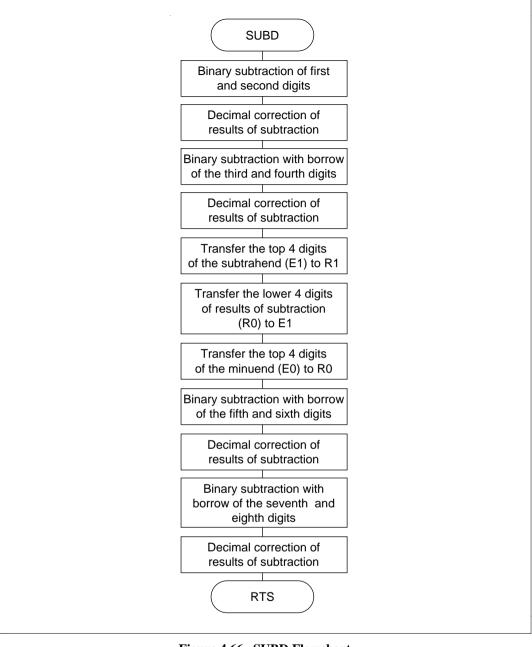

| 4.17 | 8-Digit | Decimal Subtraction                     | 155 |

|      | 4.17.1  | Description of Functions                | 158 |

|      |         | Cautions for Use                        |     |

|      | 4.17.3  | Description of Data Memory              | 158 |

|      | 4.17.4  | Examples of Use                         | 159 |

|      |         | Principles of Operation.                |     |

|      |         | Program Listing                         |     |

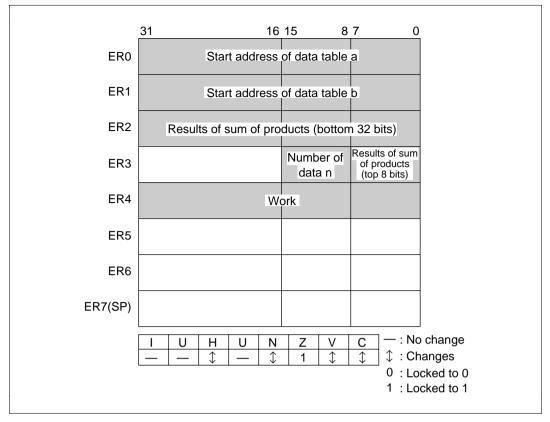

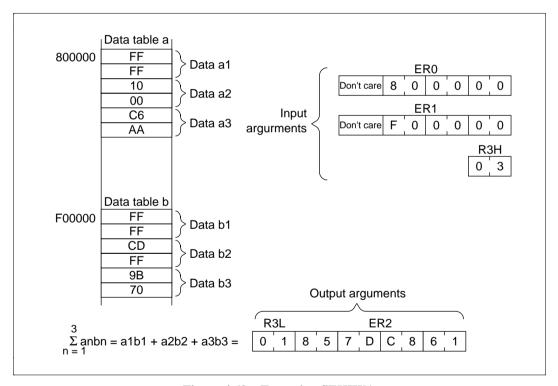

| 4.18 |         | Products                                |     |

|      |         | Description of Functions                |     |

|      |         | Cautions for Use                        |     |

|      |         | Description of Data Memory              |     |

|      |         | Examples of Use                         |     |

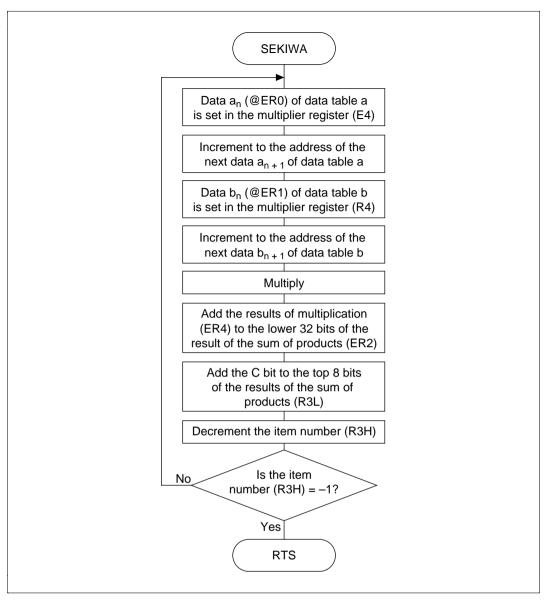

|      |         | Principles of Operation                 |     |

|      |         | Program Listing                         |     |

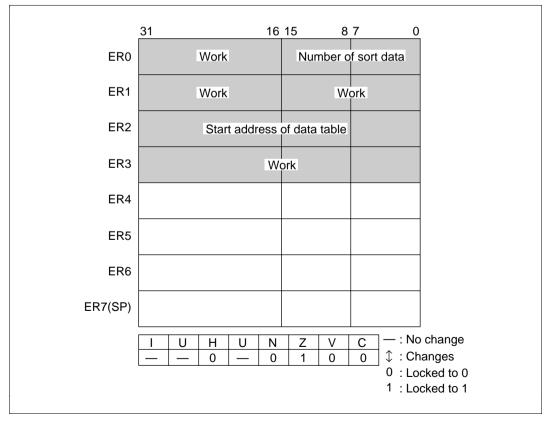

| 4.19 | _       |                                         |     |

|      |         | Description of Functions                |     |

|      |         | Description of Data Memory              |     |

|      |         | Examples of Use                         |     |

|      |         | Principles of Operation.                |     |

|      | 4.19.5  | Processing Method in Program            | 173 |

|      | 4.19.6 Program Listing     | 175 |

|------|----------------------------|-----|

| Арре | endix A Instruction Set    | 177 |

| A.1  | Number of Execution States | 178 |

| Арре | endix B Assembler          | 190 |

| B.1  | .CPU                       | 190 |

| B.2  | SECTION                    | 191 |

| B.3  | .EQU                       | 193 |

| B.4  | .ORG                       | 194 |

| B.5  | .DATA                      | 195 |

| B.6  | .RES                       | 196 |

| B.7  | .END                       | 197 |

# Section 1 CPU Architecture

#### 1.1 Introduction

The H8/300H is a high-speed CPU with an internal 32-bit configuration and architecture that is upward-compatible with the H8/300. The H8/300H CPU has sixteen 16-bit general registers, can handle 16 Mbyte of linear address space, and is ideal for realtime control.

#### 1.1.1 Features

The H8/300H has the following features:

- Upward compatibility with the H8/300: H8/300 object programs can be run without any changes

- Sixteen 16-bit general registers (can also be used as a sixteen 8-bit registers or eight 32-bit registers)

- Sixty two basic instructions: 8/16/32 bit operation instructions, multiplication/division instructions, powerful bit-manipulation instructions

- Eight types of addressing modes:

- Register direct (Rn)

- Register indirect (@ERn)

- Register indirect with displacement (@(d:16, ERn)/@(d:24, ERn))

- Post-increment/pre-decrement register indirect (@ERn+/@-ERn),

- Absolute addressing (@aa:8/@aa:16/@aa:24)

- Immediate (#xx:8/#xx:16/#xx:32)

- Program counter relative (d:8, d:16)

- Memory indirect (@@aa:8)

- 16 Mbyte address space

- High-speed operation:

- Almost all common instructions executed in 2, 4, or 6 states

- Maximum operating frequency: 16 MHz

- Addition/subtraction between 8/16/32-bit registers: 0.17 μs

- Multiplication of two 8-bit registers: 1.2 μs

- Division of a 16-bit by an 8-bit register: 1.2 μs

- Multiplication of two 16-bit registers: 1.8 μs

- Division of a 32-bit by a 16-bit register: 1.8 μs

- Two CPU operating modes: Normal mode/advanced mode

- Power-down mode: SLEEP instruction activates power-down mode

#### 1.1.2 Register Configuration

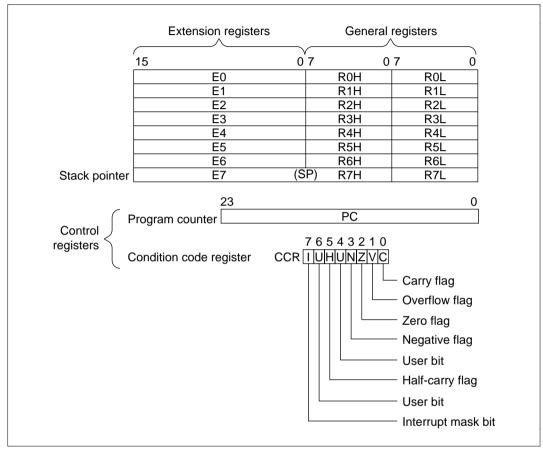

Figure 1.1 shows the register configuration for the H8/300H. The H8/300H CPU is composed of sixteen 8-bit general register (R0H/R0L–R7H/R7L), eight 16-bit extended registers (E0–E7), one 24-bit program counter (PC) and one 8-bit condition code register (CCR), which are used as control registers.

Figure 1.1 Composition of Registers

**Extended Registers:** There are two ways of using extended registers:

- When working with 32-bit data and addresses (24 bits), 16-bit general registers (R0–R7) are combined as shown in table 1.1 and used as the upper 16 bits of 32-bit registers (ERn).

- They can also be used as independent 16-bit registers (En).

Note: The function of E7 as the upper 16 bits of the stack pointer (SP) is already allocated and is used implicitly in exception processing and subroutine calls.

#### **General Registers:**

- General registers can be used as independent 8-bit registers (R0H/R0L–R7H/R7L).

- 8-bit registers can be combined with each other as shown in figure 1.2 for use as 16-bit registers (Rn).

- When working with 32-bit data and addresses (24 bits) and combining extended registers (E0–E7) as shown in figure 1.3, general registers can be used as the lower 16 bits of 32-bits registers (ERn).

Note: The function of R7 as the lower 16 bits of the stack pointer (SP) is already allocated and is used implicitly in exception processing and subroutine calls.

| R0 | R0H | R0L | E0 |

|----|-----|-----|----|

| R1 | R1H | R1L | E1 |

| R2 | R2H | R2L | E2 |

| R3 | R3H | R3L | E3 |

| R4 | R4H | R4L | E4 |

| R5 | R5H | R5L | E5 |

| R6 | R6H | R6L | E6 |

| R7 | R7H | R7L | E7 |

Figure 1.2 16-Bit Registers (Rn)

| ER0 | E0 | R0       |

|-----|----|----------|

| ER1 | E1 | R1       |

| ER2 | E2 | R2       |

| ER3 | E3 | R3       |

| ER4 | E4 | R4       |

| ER5 | E5 | R5       |

| ER6 | E6 | R6       |

| ER7 | E7 | R7       |

|     |    | <u> </u> |

Figure 1.3 32-Bit Registers (ERn)

**Program counter (PC):** The PC is a 24-bit counter that indicates the address of the next instruction to be executed by the CPU.

**Condition Code Register (CCR):** The CCR is an 8-bit register that indicates the internal status of the CPU (table 1.1).

**Table 1.1** Condition Code Register

| Bit | Function               | Description                                                                                                                                                                                                                                                                                                                                                                        |

|-----|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Interrupt mask bit (I) | When this bit is 1, interrupts are masked. Note that a nonmaskable interrupt is received regardless of the status of the I bit. When exception processing begins, this bit is set to 1.                                                                                                                                                                                            |

| 6   | User bit (UI)          | Can read/write using software (LDC, STC, ANDC, ORC, XORC instructions). Can also be used as an interrupt mask bit. For more information, see the hardware manual for the product in question.                                                                                                                                                                                      |

| 5   | Half carry flag (H)    | When executing the ADD.B, ADDX.B, SUB.B, SUBX.B, CMP.B, or NEG.B instructions results in a borrow or carry at bit 3, or when executing an ADD.W, SUB.W, CMP.W, or NEG.W instruction results in a borrow or carry at bit 11, or when executing an ADD.L, SUB.L, CMP.L, or NEG.L instruction results in a borrow or carry at bit 27, the bit is set to 1; otherwise, it is set to 0. |

| 4   | User bit (U)           | Can read/write using software (LDC, STC, ANDC, ORC, XORC instructions).                                                                                                                                                                                                                                                                                                            |

| 3   | Negative flag (N)      | The MSB of the data is considered a sign bit and its value is saved.                                                                                                                                                                                                                                                                                                               |

| 2   | Zero flag (Z)          | When the data is zero this bit is set to 1; when the data is nonzero, the bit is cleared to 0.                                                                                                                                                                                                                                                                                     |

| 1   | Overflow flag (V)      | When execution of an arithmetic operation instruction creates an overflow, this bit is set to 1. In all other cases, it is set to 0.                                                                                                                                                                                                                                               |

| 0   | Carry flag (C)         | When execution of an operation creates a carry, this bit is set to 1; otherwise, it is set to 0. There are three types of carries:                                                                                                                                                                                                                                                 |

|     |                        | 1. Carries caused by addition                                                                                                                                                                                                                                                                                                                                                      |

|     |                        | 2. Borrows caused by subtraction                                                                                                                                                                                                                                                                                                                                                   |

|     |                        | 3. Carries caused by shift/rotates                                                                                                                                                                                                                                                                                                                                                 |

|     |                        | The carry flag has a bit accumulator function that can be used by bit manipulation instructions.                                                                                                                                                                                                                                                                                   |

# 1.1.3 Data Configuration

The H8/300H can work with 1-bit, 4-bit BCD, 8-bit (byte), 16-bit (word), and 32-bit (longword) data. 1-bit data is handled with bit manipulation instructions and accessed as the nth bit (n = 0, 1, 1)

2, ..., 7) of the operand data (byte). In the DAA and DAS decimal adjust instructions, byte data is two columns of 4-bit BCD data.

**Data Configuration of Registers:** Table 1.2 shows the configuration of data in the registers.

**Table 1.2** Register Data Configuration

| Data Type | Register No. | Data Image                         |

|-----------|--------------|------------------------------------|

| 1 bit     | RnH          | 7 0<br>76543210 Don't care         |

|           | RnL          | 7 0<br>7 6 5 4 3 2 1 0  Don't care |

| 4-bit BCD | RnH          | Lower column                       |

|           |              | 7 43 0 Don't care                  |

|           |              | Upper column                       |

|           | RnL          | Lower column                       |

|           |              | 7 43 0<br>Don't care 4 V           |

|           |              | Upper column                       |

| Byte      | RnH          | 7 0<br>Don't care                  |

|           | RnL          | 7 0<br>Don't care                  |

| Word      | Rn           | 15 0                               |

|           | En           | 15 0                               |

| Long word | ERn          | 31 1615 0<br>En Rn                 |

|           |              |                                    |

Legend

ERn: General register (long word size)

RnH: Top of general register

RnL: Bottom of general register

MSB: Most significant bit LSB: Least significant bit

**Data Configuration in Memory:** Table 1.3 shows the configuration of data in memory. The H8/300H CPU can access word and longword data in memory. The MOV.W and MOV.L instructions are limited to data that starts from even addresses. When accessing word or long word

data that starts from odd addressees, the LSB of the address is considered 0 and data is accessed starting from the address one before. In such cases, no address errors are produced. The same applies to instruction code.

**Table 1.3** Memory Data Configuration

| Data Type | Memory Image |                 |

|-----------|--------------|-----------------|

| 1 bit     | nth address  | 7 6 5 4 3 2 1 0 |

| Byte      | •            |                 |

|           | nth address  | MSB LSB         |

| Word      |              |                 |

|           | Even address | MSB             |

|           | Odd address  | LSB             |

| Long word |              | <u> </u>        |

|           | Even address | MSB             |

|           | Odd address  |                 |

|           | Even address |                 |

|           | Odd address  | LSB             |

## 1.1.4 Address Space

There are two H8/300H operating modes: normal mode and advanced mode. Table 1.4 describes the operating modes and figure 1.4 shows the memory maps for these two modes. The mode pin of the LSI is used to select the mode. See the hardware manual of the product in question for more information.

Table 1.4 Address Space for Normal and Advanced Operating Modes

| <b>CPU Operating Mode</b> | Description                                                                                                                                                 |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Normal                    | Supports up to a maximum of 64 kbytes of address space. In this mode, the top 8 bits of the address are ignored and memory is accessed on 16-bit addresses. |  |  |

| Advanced                  | Supports up to a maximum of 16 Mbytes of address space. Can access continuous space by using the 24-bit PC and extended registers in combination.           |  |  |

Figure 1.4 Memory Map

# 1.1.5 Addressing Mode

The H8/300H supports the eight addressing modes shown in table 1.5. The usable addressing modes vary for each instruction. Addressing modes are explained below using the various MOV commands as the primary example.

**Table 1.5 Addressing Modes**

| Addressing Mode                     | Use               |

|-------------------------------------|-------------------|

| Register direct                     | Specify registers |

| Absolute addressing                 | Specify address   |

| Register indirect                   |                   |

| Post-increment register indirect    |                   |

| Pre-decrement register indirect     |                   |

| Register indirect with displacement |                   |

| Memory indirect                     |                   |

| Program counter relative            |                   |

| Immediate                           | Specify constants |

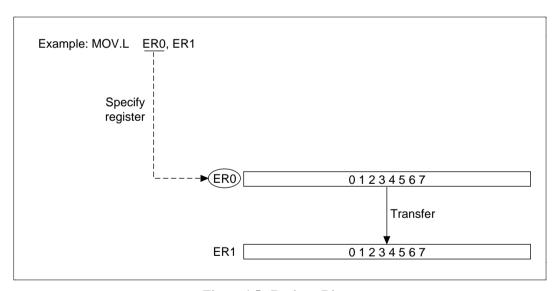

**Register Direct:** The register name (ER0–ER7, R0–R7, E0–E7, R0H/R0L–R7H/R7L) is written in the operand and the contents of that register become the subject of the instruction (figure 1.5).

Figure 1.5 Register Direct

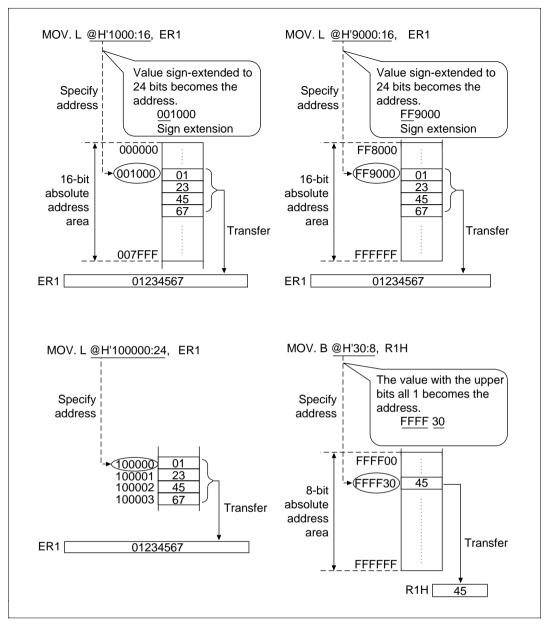

**Absolute Addressing:** Specifies the address directly. Addresses are usually specified as 24 bits in advanced mode and 16 bits in normal mode, but can be accessed by specifying only the lowest 16 bits or 8 bits when the absolute address area is 16 bits (H'000000–H'007FFF, H'FF8000–H'FFFFFF) or 8 bits (H'FFFF00–H'FFFFFF) (figure 1.6).

Figure 1.6 Absolute Addressing

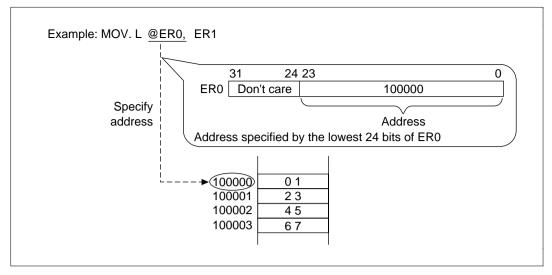

**Register Indirect:** The address is specified by the lowest 24 bits of the 32 bit register (figure 1.7).

Figure 1.7 Register Indirect

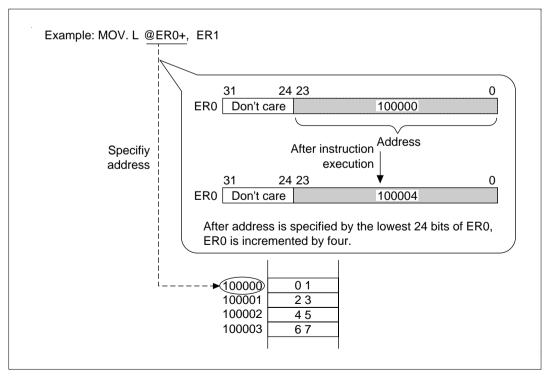

**Post-Increment Register Indirect:** The address is specified by the lowest 24 bits of the 32 bit register ERn. After instruction execution, the operand size value (B: 1, W: 2, L: 4) is added to the contents of the 32-bit register ERn (figure 1.8).

Figure 1.8 Post-Increment Register Indirect

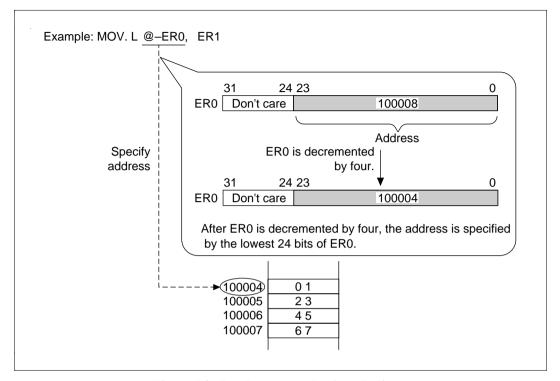

**Pre-Decrement Register Indirect:** The address is specified by the lowest 24 bits of the 32 bit register ERn. Before instruction execution, the operand size value (B: 1, W: 2, L: 4) is subtracted from the contents of the 32-bit register ERn (figure 1.9).

Figure 1.9 Pre-Decrement Register Indirect

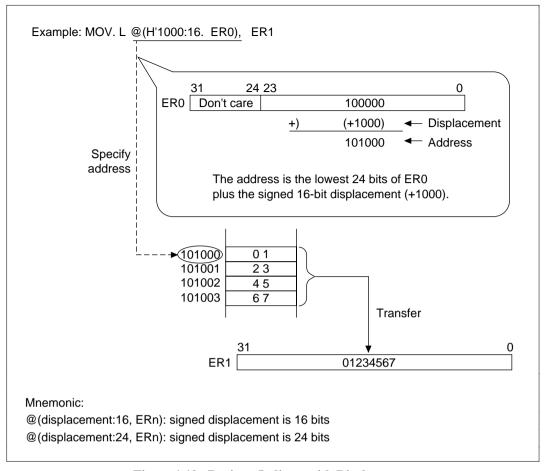

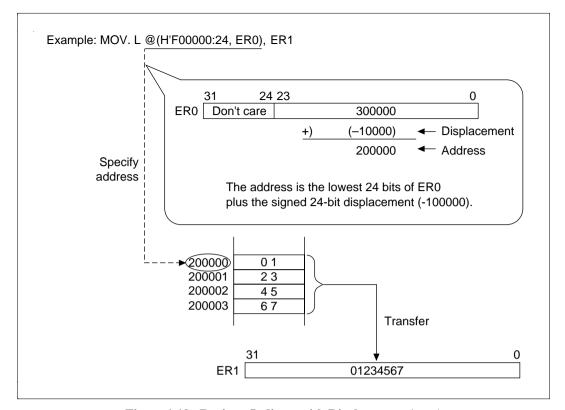

**Register Indirect with Displacement:** The address is specified by the lowest 24 bits of the 32 bit register ERn plus a signed displacement of 16 bits or 24 bits. The results of this addition are not saved in the 32-bit register ERn (figure 1.10).

Figure 1.10 Register Indirect with Displacement

Figure 1.10 Register Indirect with Displacement (cont)

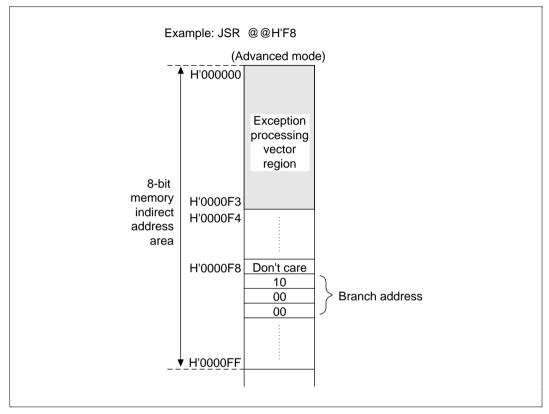

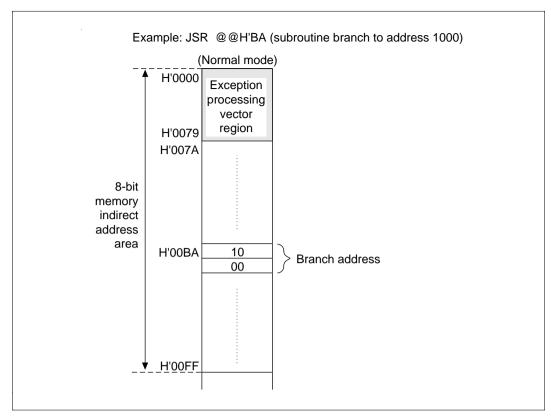

**Memory Indirect:** Uses branch address specification with the JSR and JMP instructions. The branch address is on the 8-bit memory indirect address area (advanced mode: H'00000–H'0000FF, normal mode: H'0000–H'00FF). To specify the branch address, specify the lower 8 bits of the address that stores the branch address. The address is stored in 2-byte units in normal mode and in 4-byte units for advanced mode (the first byte is ignored). Note that the top region of the 8-bit memory indirect address area is shared with the exception processing vector area. For more information, see the hardware manual for the LSI in question (figure 1.11).

Figure 1.11 Memory Indirect

Figure 1.11 Memory Indirect (cont)

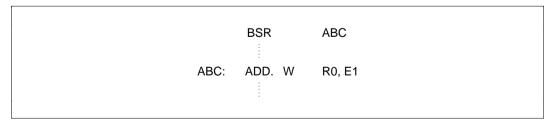

**Program Counter Relative:** Used to specify branch addresses using the Bcc or BSR instructions. It specifies the displacement of the branch address (signed 8-bit or signed 16-bit). Displacement is added to the contents of the PC and the address at the branch destination is generated. The PC contents become the start address of the next instruction, so the branchable area for the Bcc and BSR instructions are -126 to +128 bytes or -32766 to +32678 bytes. Normally, the branch destination symbol is specified rather than the displacement (figure 1.12).

Figure 1.12 Program Counter Relative

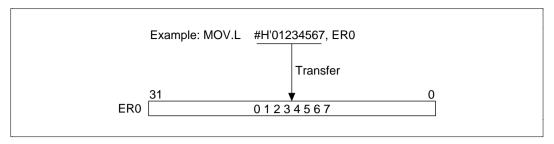

**Immediate:** Directly specifies the data on the instruction (figure 1.13).

Figure 1.13 Immediate Addressing

#### 1.1.6 Instructions

H8/300H CPU instructions have the following features:

- Instructions use a general register architecture

- A simplified and optimized 62-instruction basic set

- The common instruction length is 2 or 4 bytes

- High-speed executable multiplication and division instructions and powerful bit manipulation instructions

- 8 types of addressing modes

**Instruction Types:** There are a total of 62 H8/300H CPU instructions that are categorized according to function (table 1.6).

**Table 1.6 Instruction Categories**

| Function                           | Instruction                                                                                            | Type |

|------------------------------------|--------------------------------------------------------------------------------------------------------|------|

| Data transfer instructions         | MOV, PUSH, POP                                                                                         | 3    |

| Arithmetic operations instructions | ADD, SUB, ADDX, SUBX, INC, DEC, ADDS, SUBS, DAA, DAS, MULXU, DIVXU, MULXS, DIVXS, CMP, NEG, EXTS, EXTU | 18   |

| Logic operations instructions      | AND, OR, XOR, NOT                                                                                      | 4    |

| Shift instructions                 | SHAL, SHAR, SHLL, SHLR, ROTL, ROTR, ROTXL, ROTXR                                                       | 8    |

| Bit manipulation instructions      | BSET, BCLR, BNOT, BTST, BAND, BIAND, BOR, BIOR, BXOR, BIXOR, BLD, BILD, BST, BIST                      | 14   |

| Branching instructions             | Bcc, JMP, BSR, JSR, RTS                                                                                | 5    |

| System control instructions        | RTE, SLEEP, LDC, STC, ANDC, ORC, XORC, NOP, TRAPA                                                      | 9    |

| Block transfer instructions        | EEPMOV                                                                                                 | 1    |

# Section 2 Instructions

# 2.1 Data Transfer Instructions

#### 2.1.1 MOV

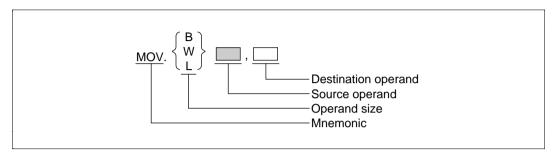

MOV (Move): Transfers 8-bit, 16-bit or 32-bit data (figure 2.1).

Figure 2.1 MOV

Table 2.1 MOV

| Mnem-<br>onic | Op.<br>Sz. | Source<br>Operand                           | Dest.<br>Op.                         | Description                      |

|---------------|------------|---------------------------------------------|--------------------------------------|----------------------------------|

| MOV           | В          | RnH or RnL                                  | RnH or<br>RnL                        | 7 0 7 0<br>RnH or RnL RnH or RnL |

|               | W          | Rn or En                                    | Rn or<br>En                          | 15 0 15 0                        |

|               | L          | ERn                                         | ERn                                  | 31 0 31 0<br>ERn ERn             |

|               | В          | @ERn<br>@(d:16,ERn)<br>@(d:24,ERn)<br>@-ERn | RnH or<br>RnL                        | 7 0 RnH or RnL                   |

|               | W          | @aa:8<br>@aa:16<br>@aa:24                   | Rn or<br>En                          | 15 ▼Rn or En ▼ 0                 |

|               | L          |                                             | ERn                                  | Even address                     |

|               | В          | RnH or RnL                                  | @ERn<br>@(d:16,<br>ERn)<br>- @(d:24, | 7 0 RnH or RnL                   |

|               | W          | Rn or En                                    | @ERn+<br>@aa:8<br>@aa:16<br>@aa:24   | Even address                     |

|               | L          | ERn                                         |                                      | Even address                     |

Table 2.1 MOV (cont)

| Mnem-<br>onic | Op.<br>Siz<br>e | Source<br>Operand | Dest.<br>Op.     | Description               |

|---------------|-----------------|-------------------|------------------|---------------------------|

| MOV<br>(cont) | В               | #xx:8             | RnH<br>or<br>RnL | #xx:8                     |

|               | W               | #xx:16            | Rn or<br>En      | #xx:16 — 15 0<br>Rn or En |

|               | L               | #xx:32            | ERn              | #xx:32 → 0<br>ERn         |

## 2.1.2 **PUSH, POP**

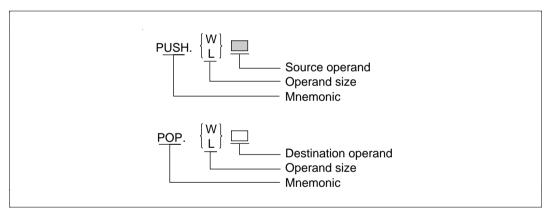

PUSH (Push Data): Saves the contents of register to stack (figure 2.2).

POP (Pop Data): Recovers the contents of register from stack (figure 2.2).

Figure 2.2 PUSH, POP

Table 2.2 PUSH, POP

| Mnem-<br>onic | Source<br>Operand | Destination<br>Operand<br>(Source<br>Operand) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|-------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PUSH          | W                 | (Rn, En)                                      | After 2 is subtracted from the stack pointer, the contents of 16-bit registers Rn and En are saved to the stack.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|               |                   |                                               | 15 Stack SP -2 H'xx xx En or Rn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                   |                                               | The instruction is the same as MOV.W Rn, @-SP or MOV.W En, @-SP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|               | L                 | (ERn)                                         | After 4 is subtracted from the stack pointer, the contents of 32-bit register ERn are saved to the stack.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|               |                   |                                               | Stack SP -4  31  H'xx xx xx xx  ERn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               |                   |                                               | The instruction is the same as MOV.L ERn, @SP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| POP           | W                 | Rn, En                                        | The contents of 16-bit registers Rn and En saved to the stack are recovered. After recovery 2 is added to the stack pointer.    Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|               |                   |                                               | 15 \rightarrow 0 SP \rightarrow SP \ |

|               |                   |                                               | The instruction is the same as MOV.W @SP+,Rn or MOV.W @SO+, En.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | L                 | ERn                                           | The contents of 32-bit register ERn saved to the stack are recovered. After recovery 4 is added to the stack pointer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|               |                   |                                               | Stack H'xx SP +4  31 ERn  The instruction is the same as MOV.> @SP+, ERn.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# 2.2 Arithmetic Operation Instructions

#### 2.2.1 ADD, SUB

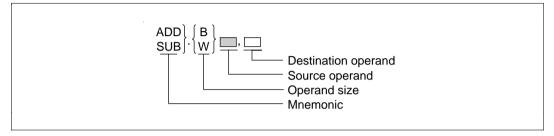

ADD (ADD binary): Summand (8 bit) + addend (8 bit) = sum (8 bit), or

Summand (16 bit) + addend (16 bit) = sum (16 bit), or Summand (32 bit) + addend (32 bit) = sum (32 bit)

SUB (Subtract binary): Subtrahend (8 bit) – minuend (8 bit) = difference (8 bit), or

Subtrahend (16 bit) – minuend (16 bit) = difference (16 bit), or Subtrahend (32 bit) – minuend (32 bit) = difference (32 bit)

Figure 2.3 shows examples of ADD and SUB.

Figure 2.3 ADD, SUB

Table 2.3 ADD, SUB

| Mnem-<br>onic | Operand<br>Size | Destination<br>Operand | Source<br>Operand         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

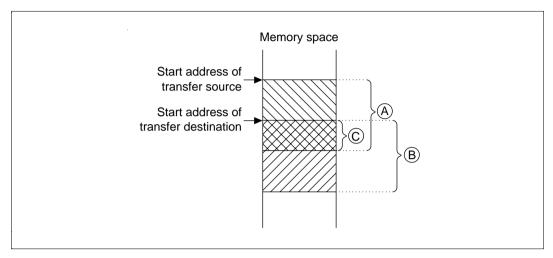

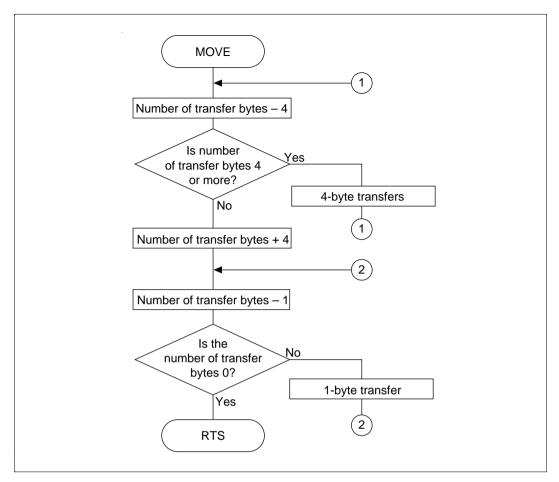

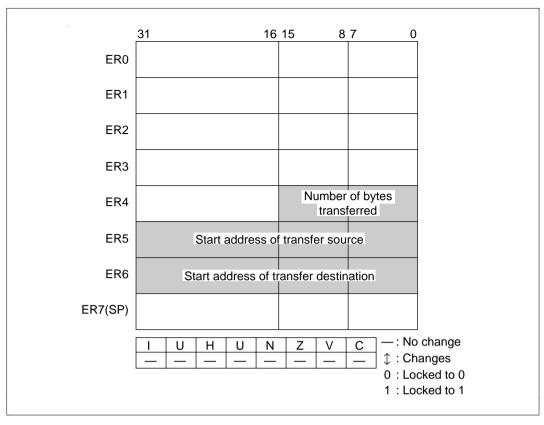

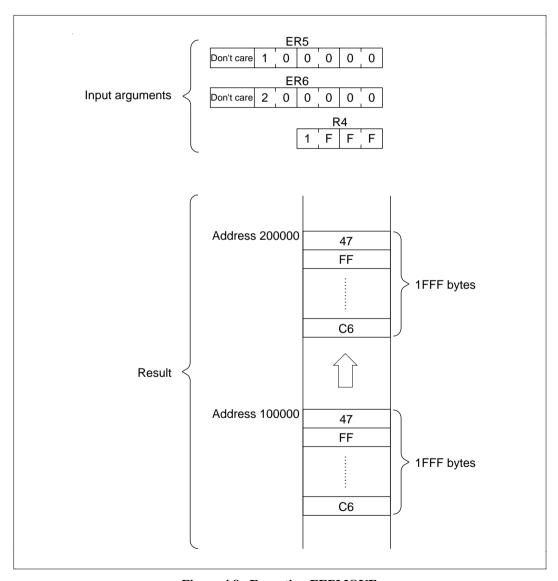

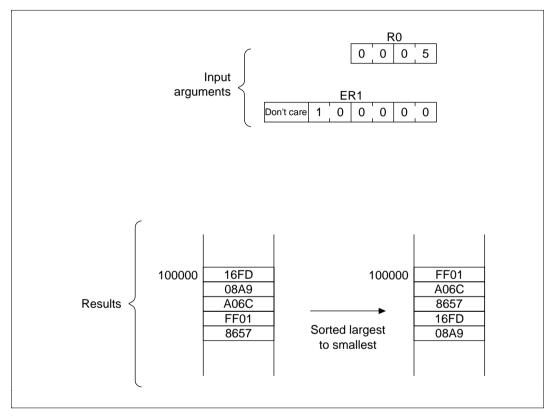

|---------------|-----------------|------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|