HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS

# HMS81020ET HMS81032ET

User's Manual (Ver. 1.00)

Version 1.00 Published by MCU Application Team ©2002 Hynix Semiconductor, Inc. All right reserved.

Additional information of this manual may be served by Hynix Semiconductor offices in Korea or Distributors and Representatives listed at address directory.

Hynix Semiconductor reserves the right to make changes to any information here in at any time without notice.

The information, diagrams and other data in this manual are correct and reliable; however, Hynix Semiconductor is in no way responsible for any violations of patents or other rights of the third party generated by the use of this manual.

| OVERVIEW<br>Description<br>Features<br>Development Tools | .1<br>.1                   |

|----------------------------------------------------------|----------------------------|

| BLOCK DIAGRAM                                            | . 3                        |

| PIN ASSIGNMENT (Top View)                                | .4                         |

| PACKAGE DIMENSION                                        | .5                         |

| PIN FUNCTION<br>Standard mode pin function               |                            |

| PORT STRUCTURES1                                         | 0                          |

| ELECTRICAL CHARACTERISTICS1<br>Absolute Maximum Ratings  | 12<br>12<br>12<br>14<br>14 |

| MEMORY ORGANIZATION                                      | 16<br>19<br>22<br>23       |

| I/O PORTS                                                | 29<br>29                   |

| CLOCK GENERATOR                                          |                            |

| BASIC INTERVAL TIMER                                     | 34                         |

\_\_\_\_\_

| WATCH DOG TIMER                                                                                                                                                                                                                                                   | 36                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Timer0, Timer1, Timer2                                                                                                                                                                                                                                            | 37                                                 |

| INTERRUPTS<br>Interrupt priority and sources<br>Interrupt control register<br>Interrupt accept mode<br>Interrupt Sequence<br>BRK Interrupt<br>Multi Interrupt<br>External Interrupt<br>Key Scan Input Processing                                                  | 46<br>46<br>47<br>48<br>50<br>50<br>50             |

| STANDBY FUNCTION<br>Sleep Mode<br>Stop Mode<br>Standby mode release<br>Operation of standby mode release                                                                                                                                                          | 53<br>53<br>54                                     |

| RESET FUNCTION<br>External RESET<br>Power on RESET<br>Low voltage detection mode                                                                                                                                                                                  | 59<br>59                                           |

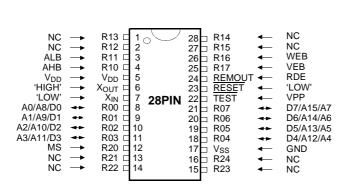

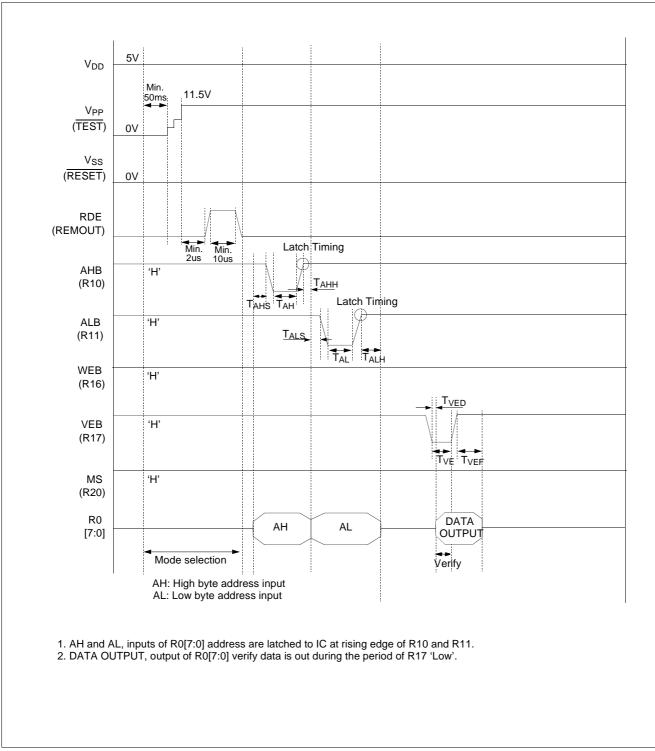

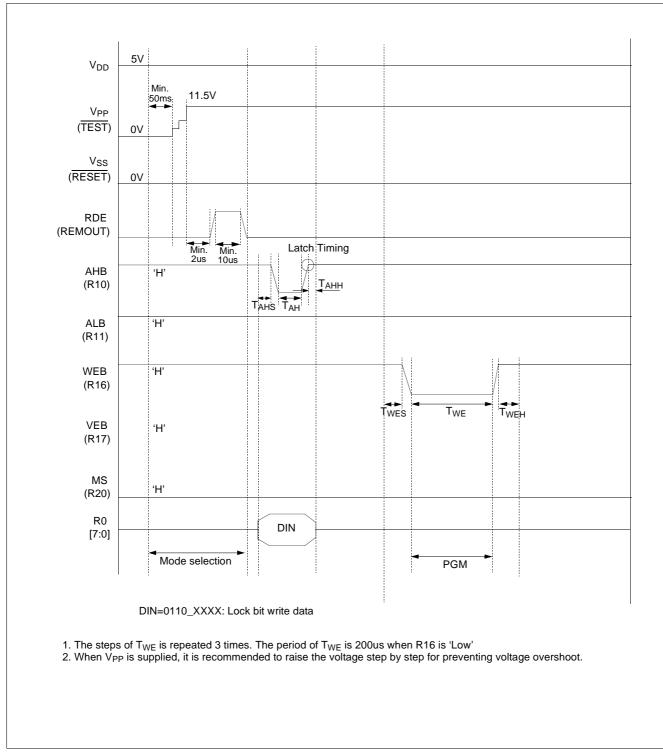

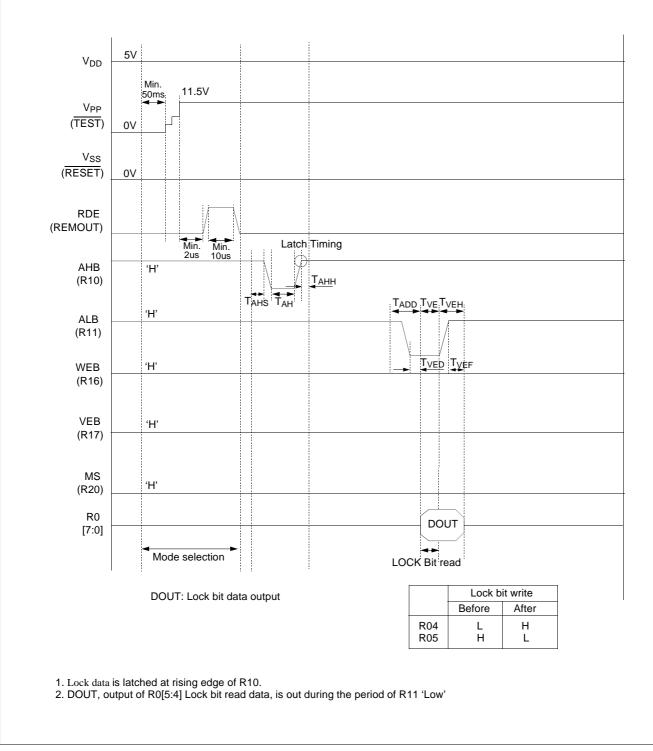

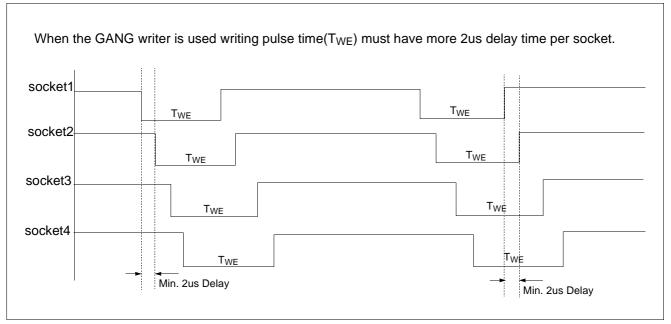

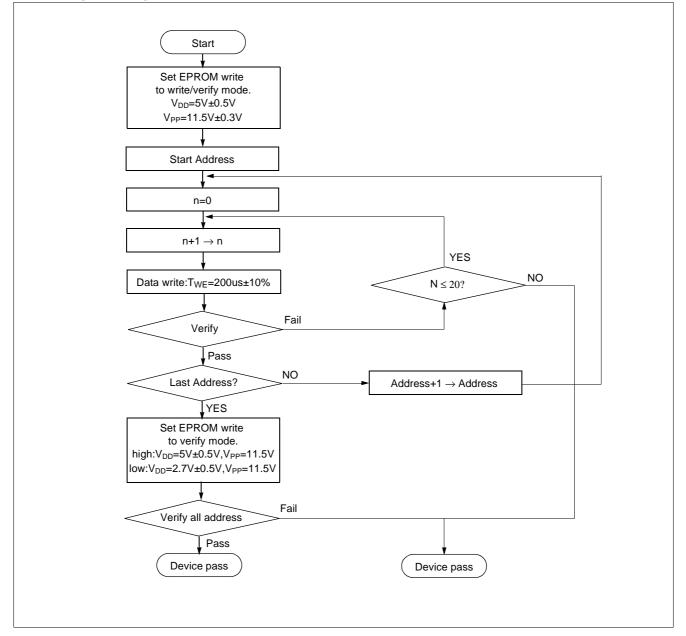

| EPROM MODE<br>PIN ASSIGNMENT (Top View)<br>EPROM mode pin function<br>EPROM Mode setting<br>General view of EPROM operation<br>EPROM write & verify<br>EPROM verify<br>LOCK bit write<br>LOCK bit read<br>Considerations on programming<br>Programming flow chart | 64<br>65<br>66<br>67<br>68<br>69<br>70<br>71<br>72 |

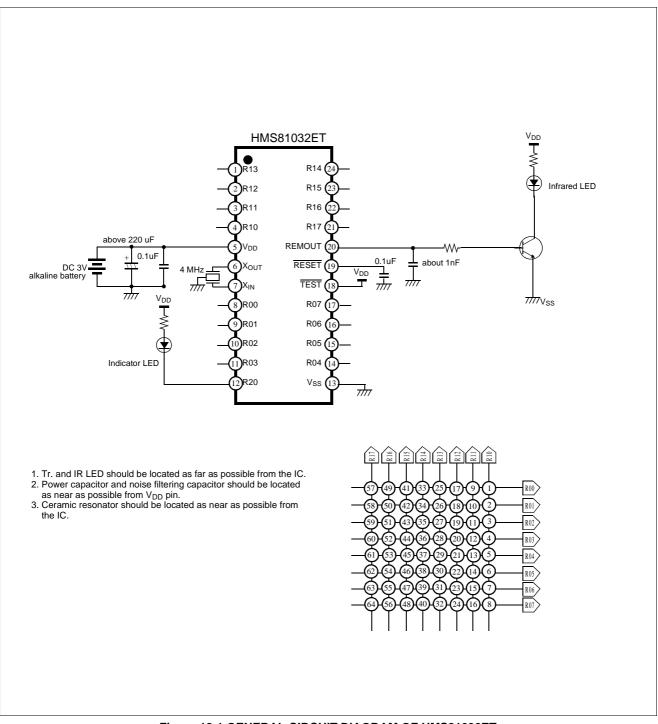

| Recommended circuit diagram of                                                                                                                                                                                                                                    |                                                    |

| HMS81032ET                                                                                                                                                                                                                                                        | 74                                                 |

# HMS81020ET/HMS81032ET

# CMOS SINGLE- CHIP 8-BIT MICROCONTROLLER FOR UNIVERSAL REMOTE CONTROLLER

# **1. OVERVIEW**

## **1.1 Description**

The HMS81020ET/HMS81032ET is an advanced CMOS 8-bit microcontroller with 20K/32K bytes of EPROM. The device is one of GMS800 family. The HYNIX HMS81020ET/HMS81032ET is a powerful microcontroller which provides a highly flexible and cost effective solution to many UR applications. The HMS81020ET/HMS81032ET provides the following standard features: 20K/32K bytes of EPROM, 448 bytes of RAM, 8-bit timer/counter, on-chip oscillator and clock circuitry. In addition, the HMS81020ET/HMS81032ET supports power saving modes to reduce power consumption, low voltage indication circuit(LVIR) to display the consumption of batteries and low voltage detection control register(LVDC) to disable or enable LVD function during transmission.

| Device Name | EPROM Size | RAM Size                   | Package                                |

|-------------|------------|----------------------------|----------------------------------------|

| HMS81020ET  | 20K Bytes  | 448 Bytes (included        | 20 SOP/PDIP                            |

| HMS81032ET  | 32K Bytes  | 256 bytes<br>stack memory) | 24 SOP/Skinny DIP<br>28 SOP/Skinny DIP |

#### 1.2 Features

- Minimum instruction execution time: 1uS at 4MHz (2 cycle NOP Instruction)

- Programmable I/O pins

|        | 20 PIN | 24 PIN | 28 PIN |

|--------|--------|--------|--------|

| INPUT  | 3      | 3      | 3      |

| OUTPUT | 2      | 2      | 2      |

| I/O    | 13     | 17     | 21     |

- Operating voltage

- 2.0 ~ 4.0 V @ 1~4MHz

- One 16-bit Timer/Counter

- Two 8-bit Timer/Counter

- One 8-bit Basic interval timer

- One 6-bit Watch dog timer

- 8 Interrupt sources

- Nested interrupt control is available.

- External input: 2

- Keyscan input: 1

- Basic interval timer: 1

- Watchdog timer: 1

- Timer : 3

- Power on reset

- Power saving operation modes

STOP operation

- SLEEP operation

- Low voltage detection(LVD) circuit to get into back-up mode

- Watchdog timer auto start (during 1second after power on reset)

- Low voltage indication circuit(LVIR) to display the consumption of batteries

- LVIR0: 2.2V(Typ.) 300mV ~ +200mV

- LVIR1: 2.0V(Typ.) 300mV ~ +200mV

- Low voltage detection control register(LVDC)

идиіх

#### **1.3 Development Tools**

The HMS81020ET/HMS81032ET are supported by a full-featured macro assembler, an in-circuit emulator CHOICE-Dr.<sup>TM</sup> and OTP programmers. Macro assembler operates under the MS-Windows 95/98<sup>TM</sup> /NT4/2000/XP.The OTP programmer can be supplied two types of programmer such as universal single programmer (CHOICE-SIGMA<sup>TM</sup>) and stand alone gran4 programmer.

| Software               | - MS- Window base assembler<br>- Linker / Editor / Debugger                           |

|------------------------|---------------------------------------------------------------------------------------|

| Hardware<br>(Emulator) | - CHOICE-Dr. (ICE main body)<br>- EVA 81C50 (Evaluation board)                        |

| OTP program-<br>mer    | <ul> <li>Universal single programmer</li> <li>stand alone gang4 programmer</li> </ul> |

EVA81C50 B/D

CHPOD810D-28SK

# **1.4 Ordering Information**

| Device name                                                                                               | Package                                                          | ROM Size (bytes) | RAM size  |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------|-----------|

| HMS81020ET 20<br>HMS81020ET 20D<br>HMS81020ET 24SK<br>HMS81020ET 24D<br>HMS81020ET 28SK<br>HMS81020ET 28D | 20DIP<br>20SOP<br>24Skinny DIP<br>24SOP<br>28Skinny DIP<br>28SOP | 20K bytes OTP    | 448 bytes |

| HMS81032ET 20<br>HMS81032ET 20D<br>HMS81032ET 24SK<br>HMS81032ET 24D<br>HMS81032ET 28SK<br>HMS81032ET 28D | 20DIP<br>20SOP<br>24Skinny DIP<br>24SOP<br>28Skinny DIP<br>28SOP | 32K bytes OTP    | 448 bytes |

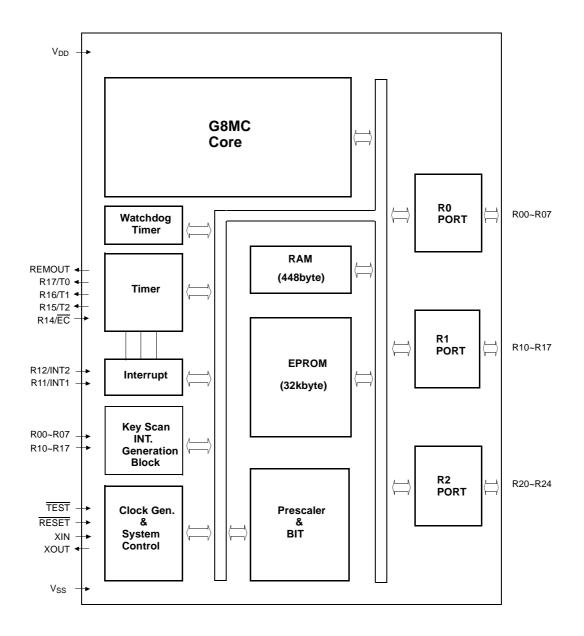

# 2. BLOCK DIAGRAM

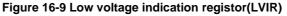

# 3. PIN ASSIGNMENT (Top View)

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ |

|---------------------------------------------------------|

|---------------------------------------------------------|

| $\begin{array}{c} R13 & \Box & 1 \\ R12 & \Box & 2 \\ R11 & \Box & 3 \\ R10 & \Box & 4 \\ V_{DD} & \Box & 5 \\ X_{OUT} & \Box & 6 \\ X_{IN} & \Box & 7 \\ R00 & \Box & 8 \\ R01 & \Box & 9 \\ R02 & \Box & 10 \\ R03 & \Box & 11 \\ R20 & \Box & 12 \\ \end{array}$ | 24 R14<br>23 R15<br>22 R16<br>21 R17<br>20 <u>REMOUT</u><br>19 <u>RESET</u><br>18 TEST<br>17 R07<br>16 R06<br>15 R05<br>14 R04<br>13 V <sub>SS</sub> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

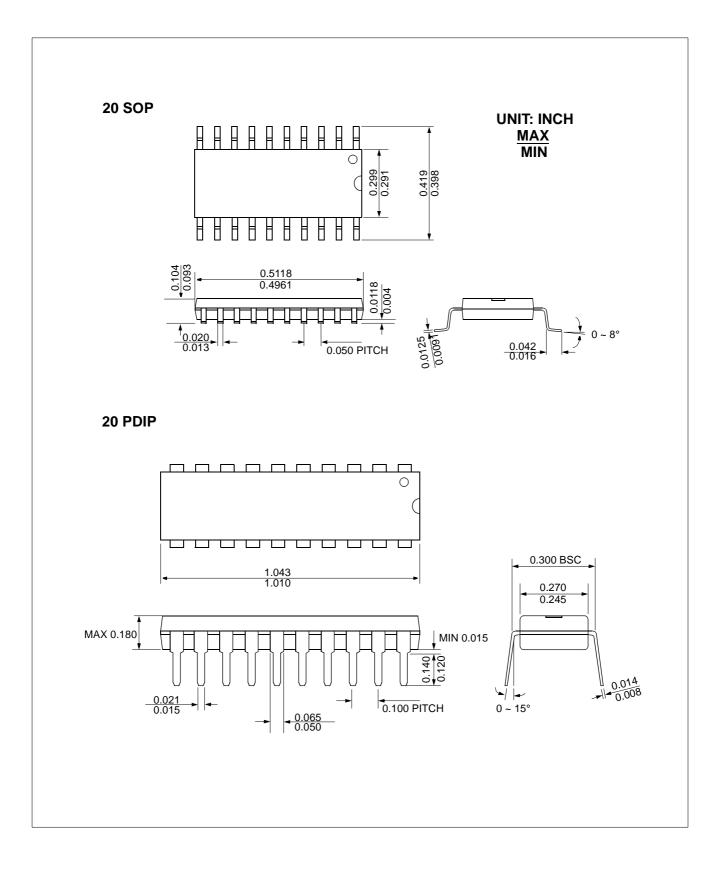

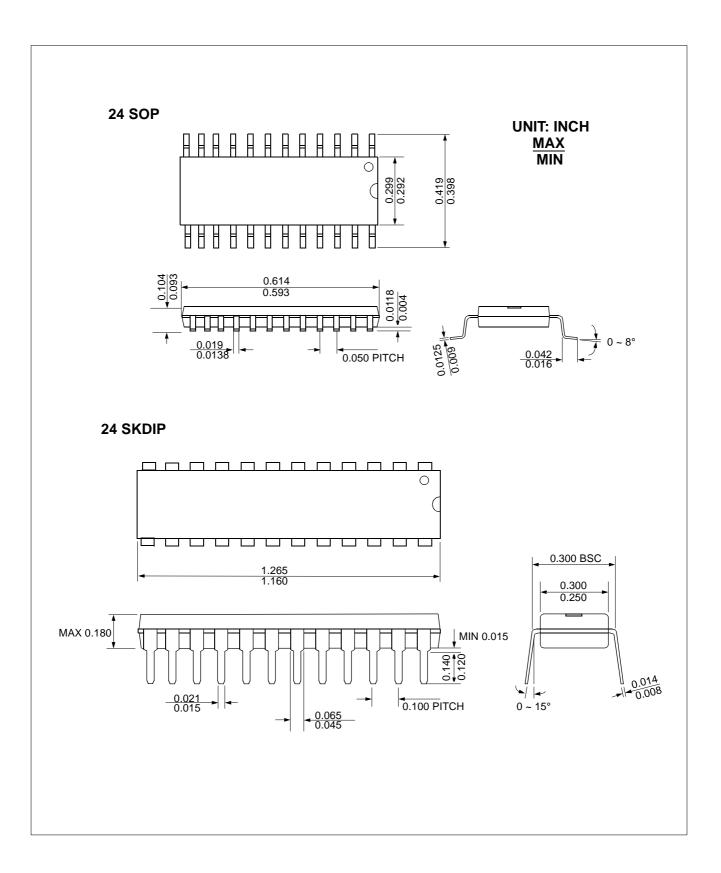

# 4. PACKAGE DIMENSION

# **5. PIN FUNCTION**

V<sub>DD</sub>: Supply voltage.

VSS: Circuit ground.

**TEST**: Used for shipping inspection of the IC. For normal operation, it should be connected to  $V_{DD}$ .

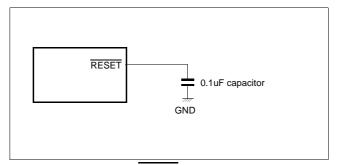

**RESET**: Reset the MCU.

$\mathbf{X}_{IN}$ : Input to the inverting oscillator amplifier and input to the internal main clock operating circuit.

**XOUT**: Output from the inverting oscillator amplifier.

**R00~R07**: R0 is an 8-bit CMOS bidirectional I/O port. R0 pins 1 or 0 written to the Port Direction Register can be used as outputs or inputs.

**R10~R17**: R1 is an 8-bit CMOS bidirectional I/O port. R1 pins 1 or 0 written to the Port Direction Register can be

used as outputs or inputs.

In addition, R1 serves the functions of the various following special features.

| Port pin | Alternate function                |

|----------|-----------------------------------|

| R11      | INT1 (External Interrupt input 1) |

| R12      | INT2 (External Interrupt input 2) |

| R14      | EC (Event Counter input)          |

| R15      | T2 (Timer / Counter output 2)     |

| R16      | T1 (Timer / Counter output 1)     |

| R17      | T0 (Timer / Counter output 0)     |

**R20~R24**: R2 is an 8-bit CMOS bidirectional I/O port. R2 pins 1 or 0 written to the Port Direction Register can be used as outputs or inputs.

# 5.1 Standard mode pin function

| PIN NAME         | INPUT/<br>OUTPUT | Function                                                                                                              | @RESET     | @STOP              |

|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------|------------|--------------------|

| R00              | I/O              |                                                                                                                       |            |                    |

| R01              | I/O              | - Each bit of the port can be individually configured<br>as an input or an output by user software                    |            |                    |

| R02              | I/O              | - 8bit Push-pull output                                                                                               |            |                    |

| R03              | I/O              | - 8bit CMOS input with pull-up resister (can be                                                                       |            | State of           |

| R04              | I/O              | <ul> <li>selectable by user software)</li> <li>Can be programmable as key scan input or open</li> </ul>               | INPUT      | before<br>Stop     |

| R05              | I/O              | drain output                                                                                                          |            |                    |

| R06              | I/O              | <ul> <li>Pull-up resisters are automatically disabled at output<br/>mode</li> </ul>                                   |            |                    |

| R07              | I/O              |                                                                                                                       |            |                    |

| R10              | I/O              | <ul> <li>- Each bit of the port can be individually configured</li> </ul>                                             |            |                    |

| R11/INT1         | I/O              | as an input or an output by user software                                                                             |            |                    |

| R12/INT2         | I/O              | - 8bit Push-pull output                                                                                               |            |                    |

| R13              | I/O              | <ul> <li>- 8bit CMOS input with pull-up resister (can be<br/>selectable by user software)</li> </ul>                  |            | State of           |

| R14/EC           | I/O              | - Can be programmable as key scan input or open                                                                       | INPUT      | before<br>Stop     |

| R15/T2           | I/O              | <ul> <li>drain output</li> <li>- Pull-up resisters are automatically disabled at output</li> </ul>                    |            |                    |

| R16/T1           | I/O              | mode                                                                                                                  |            |                    |

| R17/T0           | I/O              | - Direct driving of LED(N-Tr.)                                                                                        |            |                    |

| R20              | I/O              | - Each bit of the port can be individually configured                                                                 |            |                    |

| R21              | I/O              | as an input or an output by user software - 5bit Push-pull output                                                     |            |                    |

| R22              | I/O              | - 5bit CMOS input with pull-up resister (can be                                                                       | INPUT      | State of<br>before |

| R23              | I/O              | <ul> <li>selectable by user software)</li> <li>- Pull-up resisters are automatically disabled at output</li> </ul>    | INFUT      | Stop               |

| R24              | I/O              | <ul> <li>Pull-up resisters are automatically disabled at output mode</li> <li>Direct driving of LED(N-Tr.)</li> </ul> |            |                    |

| X <sub>IN</sub>  | I                | Oscillator input                                                                                                      |            | Low                |

| X <sub>OUT</sub> | 0                | Oscillator output                                                                                                     |            | Low                |

| REMOUT           | 0                | High current output                                                                                                   | 'L' output | 'L' output         |

| RESET            | I                | Low active, includes pull-up resistor                                                                                 | 'L' level  | state of           |

| TEST             | I                | Low active, includes pull-up resistor                                                                                 |            | before stop        |

| V <sub>DD</sub>  | Р                | Positive power supply                                                                                                 |            |                    |

| V <sub>SS</sub>  | Р                | Ground                                                                                                                |            |                    |

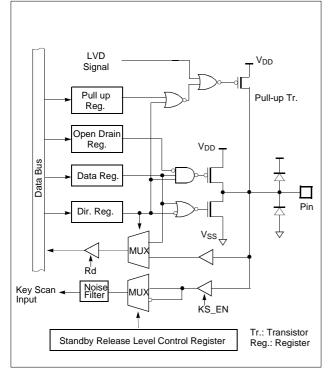

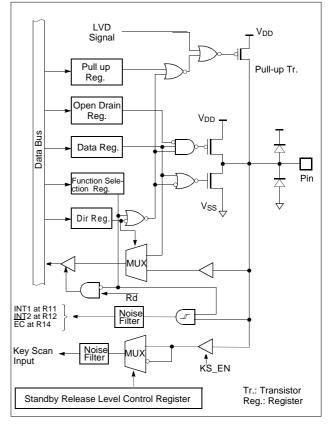

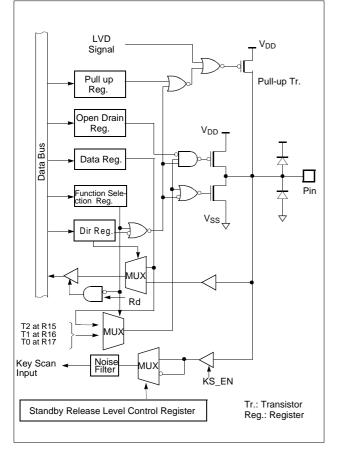

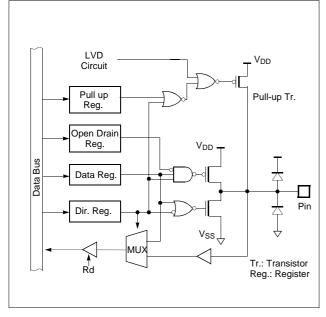

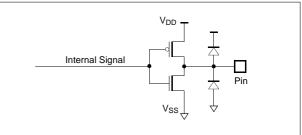

# **6. PORT STRUCTURES**

#### R0[0:7]/KS[0:7]

#### R10/KS10,R11/K<u>S11</u>/INT1, R12/KS12/INT2, R13/ KS13,R14/KS14/EC

#### R15/KS15/T2, R16/KS16/T1, R17/KS17/T0

#### R2[0:4]

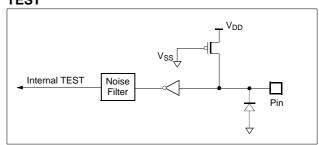

#### TEST

#### REMOUT

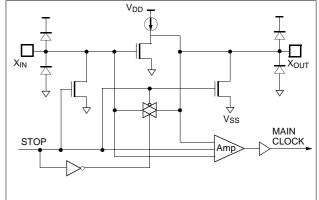

# X<sub>IN</sub>, X<sub>OUT</sub>

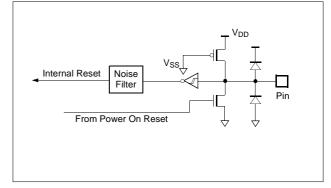

#### RESET

# 7. ELECTRICAL CHARACTERISTICS

#### 7.1 Absolute Maximum Ratings

| Supply voltage        | 0.3 to +6.0 V          |

|-----------------------|------------------------|

| Input Voltage         | 0.3 to $V_{DD}$ +0.3 V |

| Output Voltage        | 0.3 to $V_{DD}$ +0.3 V |

| Operating Temperature | 0~70°C                 |

| Storage Temperature   | 65~150°C               |

| Power Dissipation     | 700 mW                 |

**Note:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### 7.2 Recommended Operating Conditions

| Deremeter             | Symbol           | Specifi | Specifications |      |

|-----------------------|------------------|---------|----------------|------|

| Parameter             | Symbol           | Min.    | Max.           | Unit |

| Supply Voltage        | V <sub>DD</sub>  | 2.0     | 4.0            | V    |

| Operating Frequency   | f <sub>XIN</sub> | 1.0     | 4.0            | MHz  |

| Operating Temperature | T <sub>OPR</sub> | 0       | +70            | °C   |

## 7.3 DC Electrical Characteristics

(T<sub>A</sub>=-0~70°C, V<sub>DD</sub>=2.0~4.0V, GND=0V)

| Demonstra                            | Querra have      | O an diti an                                                                    | Sp                   | 11 11 |                     |      |

|--------------------------------------|------------------|---------------------------------------------------------------------------------|----------------------|-------|---------------------|------|

| Parameter                            | Symbol           | Condition                                                                       | Min.                 | Тур.  | Max.                | Unit |

| High level                           | VIH1             | R11,R12,R14(using the EXT. interrupt input),RESET                               | 0.8 V <sub>DD</sub>  | -     | V <sub>DD</sub>     | V    |

| input Voltage                        | V <sub>IH2</sub> | R0,R1,R2                                                                        | 0.7 V <sub>DD</sub>  | -     | V <sub>DD</sub>     | V    |

| Low level                            | V <sub>IL1</sub> | R11,R12,R14(using the EXT. interrupt input),RESET                               | 0                    | -     | 0.2 V <sub>DD</sub> | V    |

| input Voltage                        | V <sub>IL2</sub> | R0,R1,R2                                                                        | 0                    | -     | 0.3 V <sub>DD</sub> | V    |

| High level input<br>Leakage Current  | IIН              | $R0,R1,R2,\overline{RESET}$ (without pull-up),V <sub>IH</sub> = V <sub>DD</sub> | -                    | -     | 1                   | μA   |

| Low level input<br>Leakage Current   | IIL              | $R0,R1,R2,\overline{RESET}$ (without pull-up), $V_{IL}=0$                       | -                    | -     | -1                  | μΑ   |

|                                      | V <sub>OH1</sub> | R0, I <sub>OH</sub> =-0.5mA                                                     | V <sub>DD</sub> -0.4 | -     | -                   | V    |

| High level<br>output Voltage         | V <sub>OH2</sub> | R1, R2, I <sub>OH</sub> =-1.0mA                                                 | V <sub>DD</sub> -0.4 | -     | -                   | V    |

| ouput vonago                         | V <sub>OH3</sub> | XOUT,I <sub>OH</sub> =-50μA                                                     | V <sub>DD</sub> -0.9 | -     | -                   | V    |

|                                      | V <sub>OL1</sub> | R0, I <sub>OL</sub> =1mA                                                        | -                    | -     | 0.4                 | V    |

| Low level<br>output Voltage          | V <sub>OL2</sub> | R1, R2, I <sub>OL</sub> =5mA                                                    | -                    | -     | 0.8                 | V    |

|                                      | V <sub>OL3</sub> | XOUT,I <sub>OL</sub> =50μA                                                      | -                    | -     | 0.8                 | V    |

| High level output<br>Leakage Current | I <sub>OHL</sub> | R0,R1,R2, V <sub>OH</sub> =V <sub>DD</sub>                                      | -                    | -     | 1                   | μA   |

| Deveryoter                          | Cumhal            | Condition                                                   | S    | pecificatio | ns   | – Unit |

|-------------------------------------|-------------------|-------------------------------------------------------------|------|-------------|------|--------|

| Parameter                           | Symbol            | Condition                                                   | Min. | Тур.        | Max. |        |

| Low level output<br>Leakage Current | I <sub>OLL</sub>  | R0,R1,R2, V <sub>OL</sub> = 0                               | -    | -           | -1   | μΑ     |

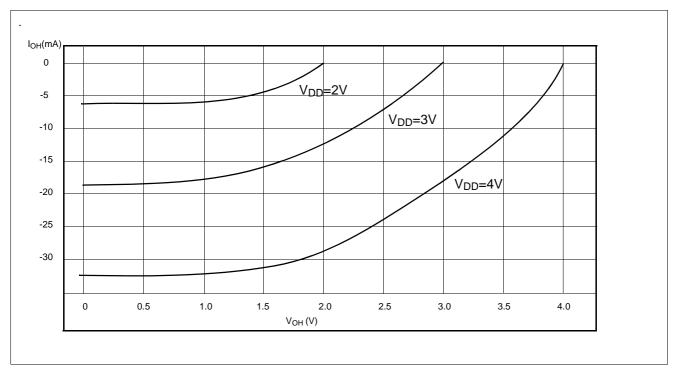

| High Level<br>output current        | I <sub>OH</sub>   | REMOUT, V <sub>OH</sub> =2V                                 | -24  | -12         | -5   | mA     |

| Low Level<br>output current         | I <sub>OL</sub>   | REMOUT, V <sub>OL</sub> =1V                                 | 0.3  | -           | 3    | mA     |

| Input pull-up current               | lp                | R0,R1,R2, RESET, TEST, VDD=3V                               | 15   | 30          | 60   | μA     |

| Feedback resistance                 | RFD               | X <sub>IN</sub> , V <sub>DD</sub> =3V                       | 0.1  | 0.4         | 1.0  | MΩ     |

|                                     | I <sub>DD1</sub>  | Operating current, fxin=4Mhz, V <sub>DD</sub> =4.0V         | -    | 4           | 10   | mA     |

|                                     | I <sub>DD2</sub>  | Operating current, fxin=4Mhz, V <sub>DD</sub> =2.0V         | -    | 2.4         | 6    | mA     |

|                                     | I <sub>SLP1</sub> | Sleep mode current, fxin=4Mhz,<br>V <sub>DD</sub> =4.0V     | -    | 2           | 3    | mA     |

| Power Supply Current                | I <sub>SLP2</sub> | Sleep mode current, fxin=4Mhz,<br>V <sub>DD</sub> =2.0V     | -    | 1           | 2    | mA     |

|                                     | I <sub>STP1</sub> | Stop mode current, Oscillator Stop<br>V <sub>DD</sub> =4.0V | -    | 3           | 10   | μA     |

|                                     | I <sub>STP2</sub> | Stop mode current, Oscillator Stop<br>V <sub>DD</sub> =2.0V | -    | 2           | 8    | μΑ     |

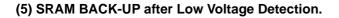

| RAM retention<br>supply voltage     | V <sub>RET</sub>  | -                                                           | 0.7  | -           | -    | V      |

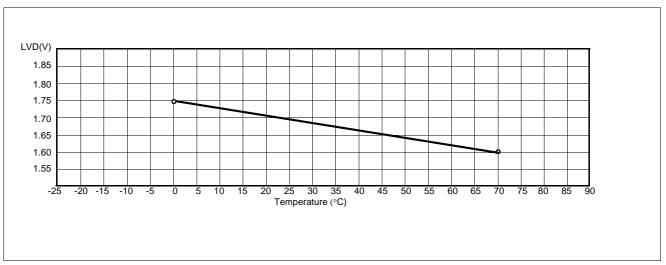

| Low voltage detection voltage       | LVD               | To get into back-up mode, Ta=25°C                           | 1.55 | 1.70        | 1.85 | V      |

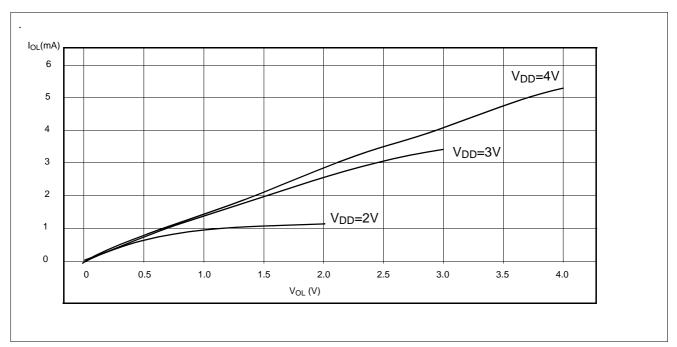

# 7.4 REMOUT Port Ioh Characteristics Graph

$(T_A=25^{\circ}C)$

Figure 7-1 I<sub>OH</sub> vs V<sub>OH</sub>

# 7.5 REMOUT Port Iol Characteristics Graph

$(T_A = 25^{\circ}C)$

Figure 7-2  $I_{OL}$  vs  $V_{OL}$

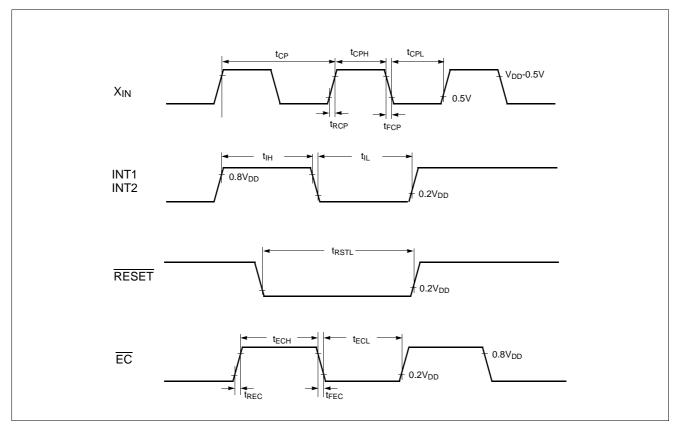

# 7.6 AC Characteristics

$(T_A=0 \rightarrow 70^{\circ}C, V_{DD}=2.0 \rightarrow 4.0V, V_{SS}=0V)$

| Banamatan                              | Symbol           | Dine            | S    | Specifications |      |                  |

|----------------------------------------|------------------|-----------------|------|----------------|------|------------------|

| Parameter                              |                  | Pins            | Min. | Тур.           | Max. | Unit             |

| External clock input cycle time        | t <sub>CP</sub>  | X <sub>IN</sub> | 250  | 500            | 1000 | ns               |

| System clock cycle time                | t <sub>SYS</sub> |                 | 500  | 1000           | 2000 | ns               |

| External clock pulse width High        | t <sub>CPH</sub> | X <sub>IN</sub> | 40   | -              | -    | ns               |

| External clock pulse width Low         | tCPL             | X <sub>IN</sub> | 40   | -              | -    | ns               |

| External clock rising time             | t <sub>RCP</sub> | X <sub>IN</sub> | -    | -              | 40   | ns               |

| External clock falling time            | tFCP             | X <sub>IN</sub> | -    | -              | 40   | nS               |

| Interrupt pulse width High             | t <sub>IH</sub>  | INT1, INT2      | 2    | -              | -    | tsys             |

| Interrupt pulse width Low              | t <sub>IL</sub>  | INT1, INT2      | 2    | -              | -    | t <sub>SYS</sub> |

| RESET Input pulse width low            | <b>t</b> RSTL    | RESET           | 8    | -              | -    | tsys             |

| Event counter input pulse width high   | t <sub>ECH</sub> | EC              | 2    | -              | -    | t <sub>SYS</sub> |

| Event counter input pulse width low    | t <sub>ECL</sub> | EC              | 2    | -              | -    | t <sub>SYS</sub> |

| Event counter input pulse rising time  | tREC             | EC              | -    | -              | 40   | ns               |

| Event counter input pulse falling time | tFEC             | EC              | -    | -              | 40   | ns               |

Figure 7-3 Timing Diagram

The HMS81020ET/HMS81032ET has separate address spaces for Program memory and Data Memory. Program memory can only be read, not written to. It can be up to

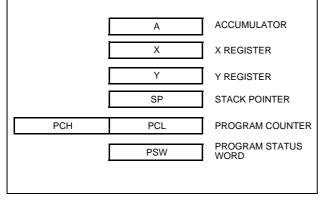

#### 8.1 Registers

This device has six registers that are the Program Counter (PC), an Accumulator (A), two index registers (X, Y), the Stack Pointer (SP), and the Program Status Word (PSW). The Program Counter consists of 16-bit register.

Figure 8-1 Configuration of Registers

#### Accumulator:

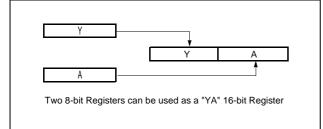

The Accumulator is the 8-bit general purpose register, used for data operation such as transfer, temporary saving, and conditional judgement, etc. The Accumulator can be used as a 16-bit register with Y Register as shown below.

In the case of multiplication instruction, execute as a multiplier register. After multiplication operation, the lower 8-bit of the result enters. (Y\*A => YA). In the case of division instruction, execute as the lower 8-bit of dividend. After division operation, quotient enters.

Figure 8-2 Configuration of YA 16-bit Register

#### X, Y Registers:

In the addressing mode which uses these index registers,

32K bytes of Program memory. Data memory can be read and written to up to 448 bytes including the stack area.

the register contents are added to the specified address, which becomes the actual address. These modes are extremely effective for referencing subroutine tables and memory tables. The index registers also have increment, decrement, comparison and data transfer functions, and they can be used as simple accumulators.

#### • X Register

In the case of division instruction, execute as register.

#### • Y Register

In the case of 16-bit operation instruction, execute as the upper 8-bit of YA. (16-bit accumulator). In the case of multiplication instruction, execute as a multiplicand register. After multiplication operation, the upper 8-bit of the result enters. In the case of division instruction, execute as the upper 8-bit of dividend. After division operation, remains enters. Y register can be used as loop counter of conditional branch command. (e.g.DBNE Y, rel)

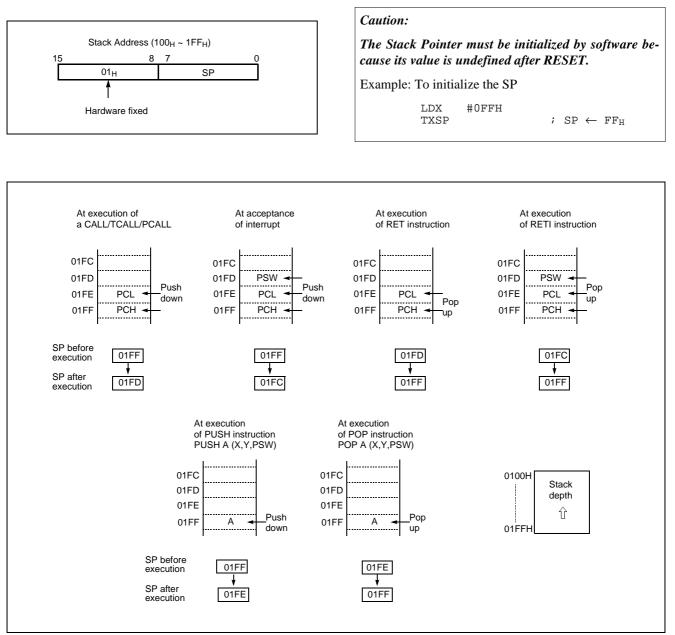

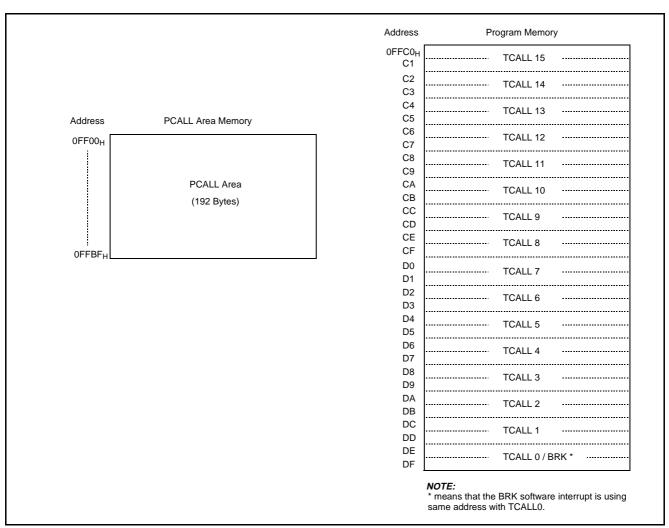

#### **Stack Pointer:**

The Stack Pointer is an 8-bit register used for occurrence interrupts, calling out subroutines and PUSH, POP, RETI, RET instruction. Stack Pointer identifies the location in the stack to be accessed (save or restore).

Generally, SP is automatically updated when a subroutine call is executed or an interrupt is accepted. However, if it is used in excess of the stack area permitted by the data memory allocating configuration, the user-processed data may be lost. The SP is post-decremented when a subroutine call or a push instruction is executed, or when an interrupt is accepted. The SP is pre-incremented when a return or a pop instruction is executed.

The stack can be located at any position within  $100_{\rm H}$  to  $1FF_{\rm H}$  of the internal data memory. The SP is not initialized by hardware, requiring to write the initial value (the location with which the use of the stack starts) by using the initialization routine. Normally, the initial value of "FF<sub>H</sub>" is used.

илиіх

Figure 8-3 Stack Operation

#### **Program Counter:**

The Program Counter is a 16-bit wide which consists of two 8-bit registers, PCH and PCL. This counter indicates the address of the next instruction to be executed. In reset state, the program counter has reset routine address ( $PC_H:OFF_H$ ,  $PC_L:OFE_H$ ).

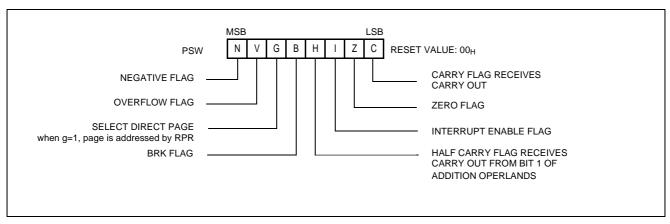

#### **Program Status Word:**

The Program Status Word (PSW) contains several bits that

reflect the current state of the CPU. The PSW is described in Figure 8-4. It contains the Negative flag, the Overflow flag, the Break flag the Half Carry (for BCD operation), the Interrupt enable flag, the Zero flag, and the Carry flag.

#### [Carry flag C]

This flag stores any carry or borrow from the ALU of CPU after an arithmetic operation and is also changed by the Shift Instruction or Rotate Instruction.

#### [Zero flag Z]

This flag is set when the result of an arithmetic operation or data transfer is "0" and is cleared by any other result.

Figure 8-4 PSW (Program Status Word) Register

#### [Interrupt disable flag I]

This flag enables/disables all interrupts except interrupt caused by Reset or software BRK instruction. All interrupts are disabled when cleared to "0". This flag immediately becomes "0" when an interrupt is served. It is set by the EI instruction and cleared by the DI instruction.

#### [Half carry flag H]

After operation, this is set when there is a carry from bit 3 of ALU or there is no borrow from bit 4 of ALU. This bit can not be set or cleared except CLRV instruction with Overflow flag (V).

#### [Break flag B]

This flag is set by software BRK instruction to distinguish BRK from TCALL instruction with the same vector address.

#### [Direct page flag G]

This flag assigns RAM page for direct addressing mode. In

the direct addressing mode, addressing area is from zero page  $00_H$  to  $0FF_H$  when this flag is "0". If it is set to "1", addressing area is 1 Page. It is set by SETG instruction and cleared by CLRG.

#### [Overflow flag V]

This flag is set to "1" when an overflow occurs as the result of an arithmetic operation involving signs. An overflow occurs when the result of an addition or subtraction exceeds  $+127(7F_H)$  or  $-128(80_H)$ . The CLRV instruction clears the overflow flag. There is no set instruction. When the BIT instruction is executed, bit 6 of memory is copied to this flag.

#### [Negative flag N]

This flag is set to match the sign bit (bit 7) status of the result of a data or arithmetic operation. When the BIT instruction is executed, bit 7 of memory is copied to this flag.

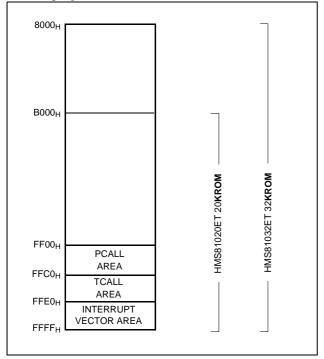

#### 8.2 Program Memory

A 16-bit program counter is capable of addressing up to 64K bytes, but this device has 20K/32K bytes program memory space only physically implemented. Accessing a location above FFFF<sub>H</sub> will cause a wrap-around to  $0000_{\text{H}}$ .

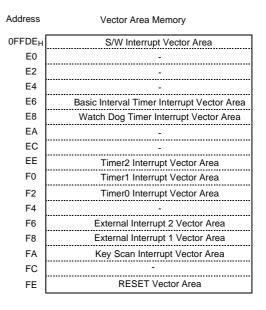

Figure 8-5, shows a map of Program Memory. After reset, the CPU begins execution from reset vector which is stored in address  $FFFE_H$  and  $FFFF_H$  as shown in Figure 8-6.

As shown in Figure 8-5, each area is assigned a fixed location in Program Memory. Program Memory area contains the user program.

Figure 8-5 Program Memory Map

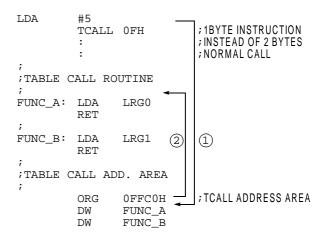

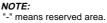

Page Call (PCALL) area contains subroutine program to reduce program byte length by using 2 bytes PCALL instead of 3 bytes CALL instruction. If it is frequently called, it is more useful to save program byte length.

Table Call (TCALL) causes the CPU to jump to each TCALL address, where it commences the execution of the service routine. The Table Call service area spaces 2-byte for every TCALL:  $0FFCO_H$  for TCALL15,  $0FFC2_H$  for TCALL14, etc., as shown in Figure 8-7.

Example: Usage of TCALL

The interrupt causes the CPU to jump to specific location, where it commences the execution of the service routine. The External interrupt 0, for example, is assigned to location  $0FFFA_H$ . The interrupt service locations spaces 2-byte interval:  $0FFF8_H$  and  $0FFF9_H$  for External Interrupt 1,  $0FFFA_H$  and  $0FFFB_H$  for External Interrupt 0, etc.

Any area from  $0FF00_H$  to  $0FFFF_H$ , if it is not going to be used, its service location is available as general purpose Program Memory.

Figure 8-6 Interrupt Vector Area

Figure 8-7 PCALL and TCALL Memory Area

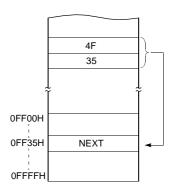

#### $\textbf{PCALL} \rightarrow \textbf{rel}$

4F35 PCALL 35H

# $TCALL \rightarrow n$

4A TCALL 4

Example: The usage software example of Vector address and the initialize part.

|                     | ORG                | OFFEOH                                 |                                                   |

|---------------------|--------------------|----------------------------------------|---------------------------------------------------|

|                     | DW                 | NOT_USED                               |                                                   |

|                     | DW                 | NOT_USED                               |                                                   |

|                     | DW                 | NOT_USED                               |                                                   |

|                     | DW                 | BIT_INT                                | ; BIT                                             |

|                     | DW                 | WDT_INT                                | ; Watch Dog Timer                                 |

|                     | DW                 | NOT_USED                               |                                                   |

|                     | DW                 | NOT_USED                               |                                                   |

|                     | DW                 | TMR2_INT                               | ; Timer-2                                         |

|                     | DW                 | TMR1_INT                               | ; Timer-1                                         |

|                     | DW                 | TMR0_INT                               | ; Timer-0                                         |

|                     | DW<br>DW           |                                        | ;                                                 |

|                     |                    | NOT_USED                               | ; Int.2                                           |

|                     | DW                 | INT2                                   |                                                   |

|                     | DW                 | INT1                                   | ; Int.1                                           |

|                     | DW                 | KEY_INT                                | ; Key Scan                                        |

|                     | DW                 | NOT_USED                               |                                                   |

|                     | DW                 | RESET                                  | ; Reset                                           |

|                     |                    |                                        |                                                   |

|                     | ORG                | 08000H                                 | ;HMS81032E Program start address                  |

| ;<br>; *******<br>; | 1<br>* * * * * * * | ************************************** | *                                                 |

| RESET:              | NOP<br>CLRG        |                                        |                                                   |

|                     | DI                 |                                        | ;Disable All Interrupts                           |

|                     | LDX                | #0                                     | Dibabie mii incertapes                            |

| RAM CLR:            | LDA                | #0                                     | ;RAM Clear(!0000H->!00BFH)                        |

|                     | STA                | $\{X\} +$                              |                                                   |

|                     | CMPX               | #0C0H                                  |                                                   |

|                     | BNE                | RAM_CLR                                | i                                                 |

|                     | DNE                |                                        |                                                   |

|                     | LDX<br>TXSP        | #ОFFH                                  | ;Stack Pointer Initialize                         |

|                     | LDM                | R0, #0                                 | ;Normal Port 0                                    |

|                     | LDM                | R0DD,#1000_0010B                       | ;Normal Port Direction                            |

|                     | LDM                | P0PC,#1000_0010B                       | ;Pull Up Selection Set                            |

|                     | LDM                | PMR1,#0000_0010B                       | R1 port / int                                     |

|                     | :                  | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,     |                                                   |

|                     | :                  |                                        |                                                   |

|                     | LDM                | CKCTLR,#0011_1101B                     | ;WDT ON, 16mS Time delay after stop mode release  |

|                     | :                  | encerance, moter_return                | , MDI SI, ISMB IIME GEIGY GIEEL BEOP MODE LEICABE |

|                     | :                  |                                        |                                                   |

|                     |                    |                                        |                                                   |

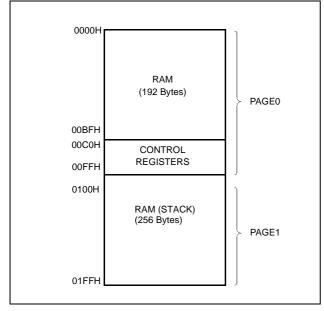

#### 8.3 Data Memory

Figure 8-8 shows the internal Data Memory space available. Data Memory is divided into 3 groups, a user RAM, control registers, Stack.

Figure 8-8 Data Memory Map

#### **User Memory**

The HMS81020ET/HMS81032ET has  $448 \times 8$  bits for the user memory (RAM).

#### **Control Registers**

The control registers are used by the CPU and Peripheral function blocks for controlling the desired operation of the device. Therefore these registers contain control and status bits for the interrupt system, the timer/ counters, analog to digital converters and I/O ports. The control registers are in address range of  $0CO_H$  to  $0FF_H$ .

Note that unoccupied addresses may not be implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate effect.

More detailed informations of each register are explained in each peripheral section.

**Note:** Write only registers can not be accessed by bit manipulation instruction. Do not use read-modify-write instruction. Use byte manipulation instruction.

Example; To write at CKCTLR

LDM CLCTLR, #09H ; Divide ratio ÷16

#### **Stack Area**

The stack provides the area where the return address is saved before a jump is performed during the processing routine at the execution of a subroutine call instruction or the acceptance of an interrupt.

When returning from the processing routine, executing the subroutine return instruction [RET] restores the contents of the program counter from the stack; executing the interrupt return instruction [RETI] restores the contents of the program counter and flags.

The save/restore locations in the stack are determined by the stack pointed (SP). The SP is automatically decreased after the saving, and increased before the restoring. This means the value of the SP indicates the stack location number for the next save. Refer to Figure 8-3 on page 17.

# **8.4** List for Control Registers

| Address | Function Register              | Symbol | Read<br>Write | RESET Value |

|---------|--------------------------------|--------|---------------|-------------|

| 00C0h   | PORT R0 DATA REG.              | R0     | R/W           | undefined   |

| 00C1h   | PORT R0 DATA DIRECTION REG.    | R0DD   | W             | 0000000b    |

| 00C2h   | PORT R1 DATA REG.              | R1     | R/W           | undefined   |

| 00C3h   | PORT R1 DATA DIRECTION REG.    | R1DD   | W             | 0000000b    |

| 00C4h   | PORT R2 DATA REG.              | R2     | R/W           | undefined   |

| 00C5h   | PORT R2 DATA DIRECTION REG.    | R2DD   | W             | 00000b      |

| 00C6h   | Reserved                       |        |               |             |

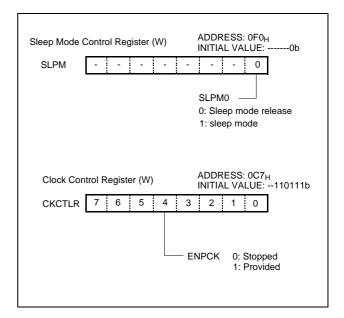

| 00C7h   | CLOCK CONTROL REG.             | CKCTLR | W             | 110111b     |

|         | BASIC INTERVAL REG.            | BITR   | R             | undefined   |

| 00C8h   | WATCH DOG TIMER REG.           | WDTR   | W             | -0001111b   |

| 00C9h   | PORT R1 MODE REG.              | PMR1   | W             | 0000000b    |

| 00CAh   | INT. MODE REG.                 | IMOD   | R/W           | 000000b     |

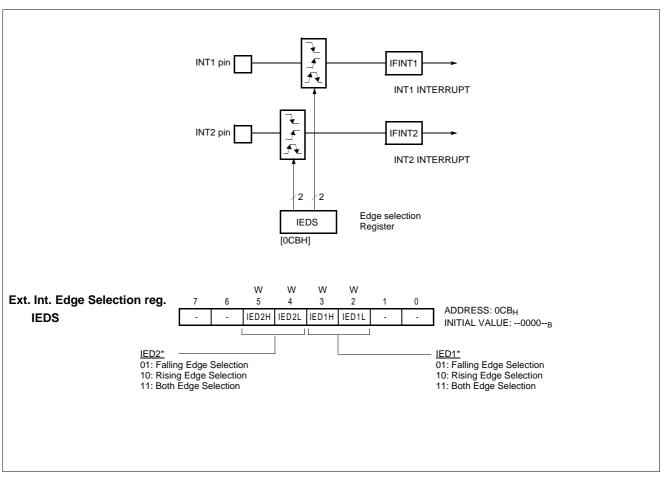

| 00CBh   | EXT. INT. EDGE SELECTION       | IEDS   | W             | 0000b       |

| 00CCh   | INT. ENABLE REG. LOW           | IENL   | R/W           | -00b        |

| 00CDh   | INT. REQUEST FLAG REG. LOW     | IRQL   | R/W           | -00b        |

| 00CEh   | INT. ENABLE REG. HIGH          | IENH   | R/W           | 000-000-b   |

| 00CFh   | INT. REQUEST FLAG REG. HIGH    | IRQH   | R/W           | 000-000-b   |

| 00D0h   | TIMER0 (16bit) MODE REG.       | TM0    | R/W           | 0000000b    |

| 00D1h   | TIMER1 (8bit) MODE REG.        | TM1    | R/W           | 0000000b    |

| 00D2h   | TIMER2 (8bit) MODE REG.        | TM2    | R/W           | 0000000b    |

| 00D3h   | TIMER0 HIGH-MSB DATA REG.      | T0HMD  | W             | undefined   |

| 00D4h   | TIMER0 HIGH-LSB DATA REG.      | TOHLD  | W             | undefined   |

| 00051   | TIMER0 LOW-MSB DATA REG.       | TOLMD  | W             | undefined   |

| 00D5h   | TIMER0 HIGH-MSB COUNT REG.     | TOHMC  | R             | undefined   |

|         | TIMER0 LOW-LSB DATA REG.       | TOLLD  | W             | undefined   |

| 00D6h   | TIMER0 LOW-LSB COUNT REG.      | TOLLC  | R             | undefined   |

| 00D7h   | TIMER1 HIGH DATA REG.          | T1HD   | W             | undefined   |

|         | TIMER1 LOW DATA REG.           | T1LD   | W             | undefined   |

| 00D8h   | TIMER1 LOW COUNT REG.          |        | R             | undefined   |

|         | TIMER2 DATA REG.               | T2DR   | W             | undefined   |

| 00D9h   | TIMER2 COUNT REG.              |        | R             | undefined   |

| 00DAh   | TIMER0 / TIMER1 MODE REG.      | TM01   | R/W           | 0000000b    |

| 00DBh   | Reserved                       |        |               |             |

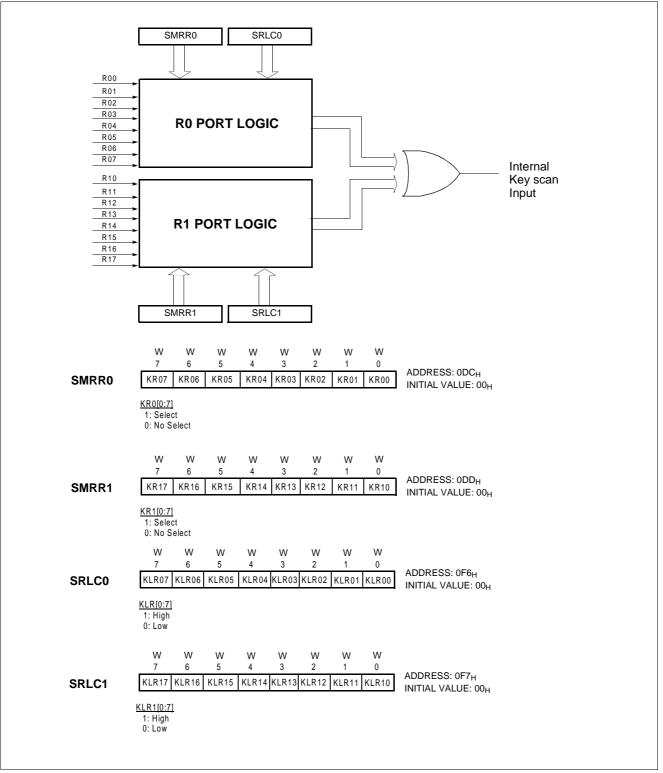

| 00DCh   | STANDBY MODE RELEASE REG0      | SMPR0  | W             | 0000000b    |

| 00DDh   | STANDBY MODE RELEASE REG0      | SMPR1  | W             | 0000000b    |

| 00DEh   | PORT R1 OPEN DRAIN ASSIGN REG. | R1ODC  | W             | 0000000b    |

| 00DFh | PORT R2 OPEN DRAIN ASSIGN REG.     | R2ODC | W | 00000b   |

|-------|------------------------------------|-------|---|----------|

| 00E0h | Reserved                           |       |   |          |

| 00E1h | Reserved                           |       |   |          |

| 00E2h | Reserved                           |       |   |          |

| 00E3h | Reserved                           |       |   |          |

| 00E4h | PORT R0 OPEN DRAIN ASSIGN REG.     | R0ODC | W | 0000000b |

| 00E5h | Reserved                           |       |   |          |

| 00E6h | Reserved                           |       |   |          |

| 00E7h | Reserved                           |       |   |          |

| 00E8h | Reserved                           |       |   |          |

| 00E9h | Reserved                           |       |   |          |

| 00EAh | Reserved                           |       |   |          |

| 00EBh | Reserved                           |       |   |          |

| 00ECh | Reserved                           |       |   |          |

| 00EDh | Reserved                           |       |   |          |

| 00EEh | Reserved                           |       |   |          |

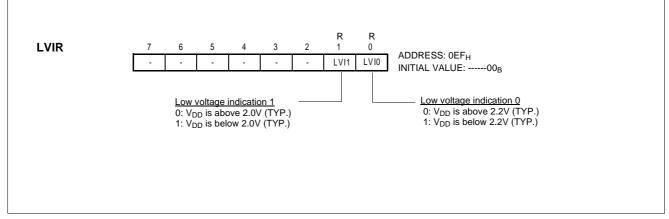

| 00EFh | LOW VOLTAGE INDICATION REG.        | LVIR  | R | 00b      |

| 00F0h | SLEEP MODE REG.                    | SLPM  | W | 0b       |

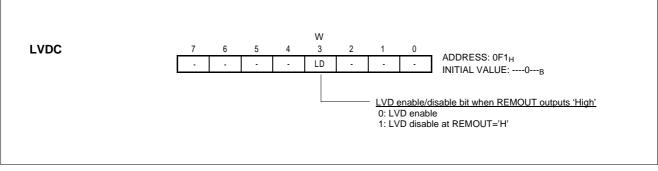

| 00F1h | LVD CONTROL REG.                   | LVDC  | W | b        |

| 00F2h | Reserved                           |       |   |          |

| 00F3h | Reserved                           |       |   |          |

| 00F4h | Reserved                           |       |   |          |

| 00F5h | Reserved                           |       |   |          |

| 00F6h | STANDBY RELEASE LEVEL CONT. REG. 0 | SRLC0 | W | 0000000b |

| 00F7h | STANDBY RELEASE LEVEL CONT. REG. 1 | SRLC1 | W | 0000000b |

| 00F8h | PORT R0 PULL-UP REG. CONT. REG.    | R0PC  | W | 0000000b |

| 00F9h | PORT R1 PULL-UP REG. CONT. REG.    | R1PC  | W | 0000000b |

| 00FAh | PORT R2 PULL-UP REG. CONT. REG.    | R2PC  | W | 00000b   |

| 00FBh | Reserved                           |       |   |          |

| 00FCh | Reserved                           |       |   |          |

| 00FDh | Reserved                           |       |   |          |

| 00FEh | Reserved                           |       |   |          |

| 00FFh | Reserved                           |       |   |          |

|       |                                    |       |   |          |

R/W

Registers are controlled by byte manipulation instruction such as LDM etc., do not use bit manipulation instruction such as SET1, CLR1 etc. If bit manipulation instruction is used on these registers, content of other seven bits are may varied to unwanted value.

Registers are controlled by both bit and byte manipulation instruction.

- : this bit location is reserved.

LVIR,LVDC are newly added in HMS81032ET, but not supported in MASK and EVA version

#### 8.5 Addressing Mode

The HMS81020ET/HMS81032ET uses six addressing modes;

- Register addressing

- Immediate addressing

- Direct page addressing

- Absolute addressing

- Indexed addressing

- Register-indirect addressing

#### (1) Register Addressing

Register addressing accesses the A, X, Y, C and PSW.

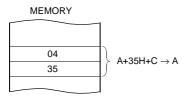

#### (2) Immediate Addressing $\rightarrow$ #imm

In this mode, second byte (operand) is accessed as a data immediately.

#### Example:

0435 ADC #35H

#### E45535 LDM 35H,#55H

#### (3) Direct Page Addressing $\rightarrow$ dp

In this mode, a address is specified within direct page. Example;

C535 LDA 35H ; A  $\leftarrow$  RAM[35H]

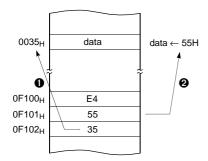

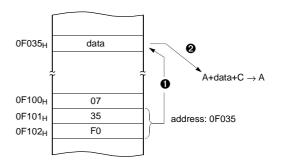

#### (4) Absolute Addressing $\rightarrow$ !abs

Absolute addressing sets corresponding memory data to Data, i.e. second byte(Operand I) of command becomes lower level address and third byte (Operand II) becomes upper level address.

With 3 bytes command, it is possible to access to whole memory area.

ADC, AND, CMP, CMPX, CMPY, EOR, LDA, LDX, LDY, OR, SBC, STA, STX, STY

Example;

| 0735F0 ADC !0F035H | $i  i \land \leftarrow ROM[0F035H]$ |

|--------------------|-------------------------------------|

|--------------------|-------------------------------------|

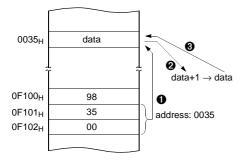

The operation within data memory (RAM) ASL, BIT, DEC, INC, LSR, ROL, ROR

Example; Addressing accesses the address 0135<sub>H</sub>.

983500 INC !0035H ;A ←RAM[035H]

#### (5) Indexed Addressing

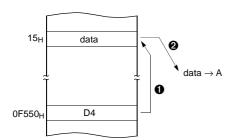

#### X indexed direct page (no offset) $\rightarrow$ {X}

In this mode, a address is specified by the X register.

ADC, AND, CMP, EOR, LDA, OR, SBC, STA, XMA

Example; X=15<sub>H</sub>

D4 LDA  $\{X\}$  ; ACC  $\leftarrow$  RAM[X].

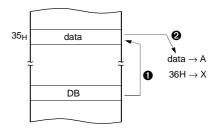

#### X indexed direct page, auto increment $\rightarrow$ {X}+

In this mode, a address is specified within direct page by the X register and the content of X is increased by 1.

LDA, STA

Example; X=35<sub>H</sub>

DB LDA {X}+

#### X indexed direct page (8 bit offset) $\rightarrow$ dp+X

This address value is the second byte (Operand) of command plus the data of X-register. And it assigns the memory in Direct page.

ADC, AND, CMP, EOR, LDA, LDY, OR, SBC, STA STY, XMA, ASL, DEC, INC, LSR, ROL, ROR

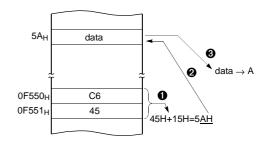

Example; X=015<sub>H</sub>

C645 LDA 45H+X

#### Y indexed direct page (8 bit offset) $\rightarrow$ dp+Y

This address value is the second byte (Operand) of command plus the data of Y-register, which assigns Memory in Direct page.

This is same with above (2). Use Y register instead of X.

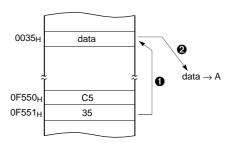

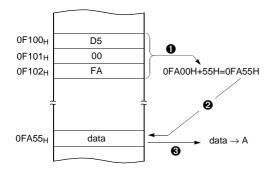

#### Y indexed absolute $\rightarrow$ !abs+Y

Sets the value of 16-bit absolute address plus Y-register data as Memory. This addressing mode can specify memory in whole area.

#### Example; Y=55<sub>H</sub>

D500FA LDA !OFA00H+Y

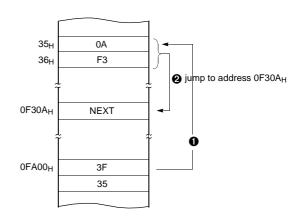

#### (6) Indirect Addressing

#### Direct page indirect $\rightarrow$ [dp]

Assigns data address to use for accomplishing command which sets memory data(or pair memory) by Operand. Also index can be used with Index register X,Y.

JMP, CALL

Example;

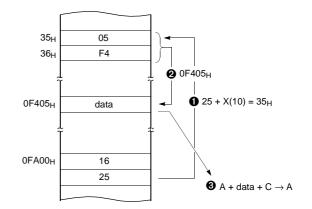

#### X indexed indirect $\rightarrow$ [dp+X]

Processes memory data as Data, assigned by 16-bit pair memory which is determined by pair data [dp+X+1][dp+X] Operand plus X-register data in Direct page.

ADC, AND, CMP, EOR, LDA, OR, SBC, STA

Example; X=10<sub>H</sub>

1625 ADC [25H+X]

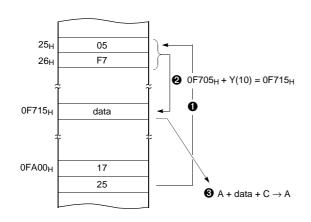

#### Y indexed indirect $\rightarrow$ [dp]+Y

Processes memory data as Data, assigned by the data [dp+1][dp] of 16-bit pair memory paired by Operand in Direct page plus Y-register data.

#### ADC, AND, CMP, EOR, LDA, OR, SBC, STA

#### Example; Y=10<sub>H</sub>

1725 ADC [25H]+Y

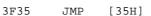

#### Absolute indirect $\rightarrow$ [!abs]

The program jumps to address specified by 16-bit absolute address.

JMP

#### Example;

1F25F0 JMP [!0F025H]

PROGRAM MEMORY

# 9. I/O PORTS

The HMS81020ET/HMS81032ET has 21 I/O ports which are PORT0(8 I/O), PORT1 (8 I/O), PORT2 (5 I/O). Pullup resistor of each port can be selectable by program. Each port contains data direction register which controls I/O and data register which stores port data.

#### 9.1 R0 Ports

R0 is an 8-bit CMOS bidirectional I/O port (address  $0C0_{\rm H}$ ). Each I/O pin can independently used as an input or an output through the R0DD register (address  $0C1_{\rm H}$ ).

R0 has internal pull-ups that is independently connected or disconnected by R0PC. The control registers for R0 are shown below.

|                                   | ADDRESS: 0C0 <sub>H</sub><br>RESET VALUE: Undefined<br>R02 R01 R00                                                  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------|

| R0 Direction Register (W)         | ADDRESS: 0C1 <sub>H</sub><br>RESET VALUE: 00 <sub>H</sub><br>Port Direction<br>0: Input<br>1: Output                |

| R0 Pull-up Control Register (W)   | ADDRESS:0F8 <sub>H</sub><br>RESET VALUE: 00 <sub>H</sub><br>Pull-up select<br>1: Without pull-up<br>0: With pull-up |

| R0 Open drain Assign Register (W) | ADDRESS:0E4 <sub>H</sub><br>RESET VALUE: 00 <sub>H</sub>                                                            |

#### (1) R0 I/O Data Direction Register (R0DD)

R0 I/O Data Direction Register (R0DD) is an 8-bit register, and can assign input state or output state to each bit. If R0DD is "1", port R0 is in the output state, and if "0", it is in the input state. R0DD is write-only register. Since R0DD is initialized as "00h" in reset state, the whole port R0 becomes input state.

#### (2) R0 Data Register (R0)

R0 data register (R0) is an 8-bit register to store data of port R0. When set as the output state by R0DD, and data is written in R0, data is output into R0 pin. When set as the input state, input state of pin is read. The initial value of R0 is unknown in reset state.

#### (3) R0 Open drain Assign Register (R0ODC)

R0 Open Drain Assign Register (R0ODC) is an 8-bit register, and can assign R0 port as open drain output port each bit, if corresponding port is selected as output. If R0ODC is selected as "1", port R0 is open drain output, and if selected as, "0" it is push-pull output. R0ODC is write-only register and initialized as "00h" in reset state.

#### (4) R0 Pull-up Control Register (R0PC)

R0 Pull-up Control Register (R0PC) is an 8-bit register and can control pull-up on or off each bit, if corresponding port is selected as input. If R0PC is selected as "1", pull-up is disabled and if selected as "0", it is enabled. R0PC is writeonly register and initialized as "00h" in reset state. The pull-up is automatically disabled, if corresponding port is selected as output.

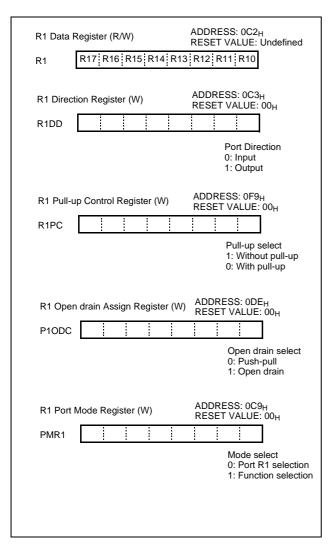

#### 9.2 R1 Ports

R1 is an 8-bit CMOS bidirectional I/O port (address  $0C2_{\rm H}$ ). Each I/O pin can independently used as an input or an output through the R1DD register (address  $0C3_{\rm H}$ ).

R1 has internal pull-ups that is independently connected or disconnected by register R1PC. The control registers for R1 are shown at next page.

#### (1) R1 I/O Data Direction Register (R1DD)

R1 I/O Data Direction Register (R1DD) is an 8-bit register, and can assign input state or output state to each bit. If R1DD is "1", port R1 is in the output state, and if "0", it is in the input state. R1DD is write-only register. Since R1DD is initialized as "00h" in reset state, the whole port R1 becomes input state.

#### (2) R1 Data Register (R1)

R1 data register (R1) is an 8-bit register to store data of port R1. When set as the output state by R1DD, and data is written in R1, data is output into R1 pin. When set as the input state, input state of pin is read. The initial value of R1 is unknown in reset state.

#### (3) R1 Open drain Assign Register (R1ODC)

R1 Open Drain Assign Register (R1ODC) is an 8bit regis-

ter, and can assign R1 port as open drain output port each bit, if corresponding port is selected as output. If R1ODC is selected as "1", port R1 is open drain output, and if selected as "0", it is push-pull output. R1ODC is write-only register and initialized as "00h" in reset state.

#### (4) R1 Port Mode Register (PMR1)

R1 Port Mode Register (PMR1) is an 8-bit register, and can assign the selection mode for each bit. When set as "0", corresponding bit of PMR1 acts as port R1 selection mode, and when set as "1", it becomes function selection mode.

PMR1 is write-only register and initialized as "00h" in reset state. Therefore, becomes Port selection mode. Port R1 can be I/O port by manipulating each R1DD bit, if corresponding PMR1 bit is selected as "0".

| Bit Name | PMR1 | Selection<br>Mode | Remarks                   |

|----------|------|-------------------|---------------------------|

| TOS      | 0    | R17 (I/O)         | -                         |

| 105      | 1    | T0 (O)            | Timer0                    |

| T40      | 0    | R16 (I/O)         | -                         |

| T1S      | 1    | T1 (O)            | Timer1                    |

| TOO      | 0    | R15 (I/O)         | -                         |

| T2S      | 1    | T2 (O)            | Timer2                    |

| ECS      | 0    | R14 (I/O)         | -                         |

| ECS      | 1    | EC (I)            | Timer0 Event              |

|          | 0    | R12 (I/O)         |                           |

| INT2S    | 1    | INT2 (I)          | Timer0 Input Cap-<br>ture |

|          | 0    | R11 (I/O)         |                           |

| INT1S    | 1    | INT1 (I)          |                           |

Table 9-1 Selection mode of PMR1

#### (5) R1 Pull-up Control Register (R1PC)

R1 Pull-up Control Register (R1PC) is an 8-bit register and can control pull-up on or off each bit, if corresponding port is selected as input. If R1PC is selected as "1", pull-up is disabled and if selected as "0", it is enabled. R1PC is writeonly register and initialized as "00h" in reset state. The pull-up is automatically disabled, if corresponding port is selected as output.

#### 9.3 R2 Port

R2 is an 5-bit CMOS bidirectional I/O port (address  $0C4_{\rm H}$ ). Each I/O pin can independently used as an input or an output through the R2DD register (address  $0C5_{\rm H}$ ).

R2 has internal pull-ups that is independently connected or disconnected by R2PC (address  $0FA_H$ ). The control registers for R2 are shown as below.

| R2 Data R<br>R2    | egister (R/W)             | ADDRESS: 0C4 <sub>H</sub><br>RESET VALUE: Undefined<br>3 R22 R21 R20                                                |

|--------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------|

| R2 Directi<br>R2DD | on Register (W)           | ADDRESS: 0C5 <sub>H</sub><br>RESET VALUE: 00 <sub>H</sub><br>Port Direction<br>0: Input<br>1: Output                |

| R2 Pull-u<br>R2PC  | o Control Register (W)    | ADDRESS:0FA <sub>H</sub><br>RESET VALUE: 00 <sub>H</sub><br>Pull-up select<br>1: Without pull-up<br>0: With pull-up |

| R2 Open<br>R2ODC   | drain Assign Register (W) | ADDRESS:0DF <sub>H</sub><br>RESET VALUE: 00 <sub>H</sub><br>Open drain select<br>0: Push-pull<br>1: Open drain      |

#### (1) R2 I/O Data Direction Register (R2DD)

R2 I/O Data Direction Register (R2DD) is an 8-bit register, and can assign input state or output state to each bit. If R2DD is "1", port R2 is in the output state, and if "0", it is in the input state. R2DD is write-only register. Since R2DD is initialized as "00h" in reset state, the whole port R2 becomes input state.

#### (2) R2 Data Register (R2)

R2 data register (R2) is an 8-bit register to store data of port R2. When set as the output state by R2DD, and data is written in R2, data is outputted into R2 pin. When set as the input state, input state of pin is read. The initial value of R2 is unknown in reset state.

#### (3) R2 Open drain Assign Register (R2ODC)

R2 Open Drain Assign Register (R2ODC) is an 8bit register, and can assign R2 port as open drain output port each bit, if corresponding port is selected as output. If R2ODC is selected as "1", port R2 is open drain output, and if selected as "0", it is push-pull output. R2ODC is write-only register and initialized as "00h" in reset state.

#### (4) R2 Pull-up Control Register (R2PC)

R2 Pull-up Control Register (R2PC) is an 8-bit register and can control pull-up on or off each bit, if corresponding port is selected as input. If R2PC is selected as "1", pull-up ia disabled and if selected as "0", it is enabled. R2PC is writeonly register and initialized as "00h" in reset state. The pull-up is automatically disabled, if corresponding port is selected as output.

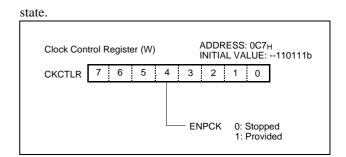

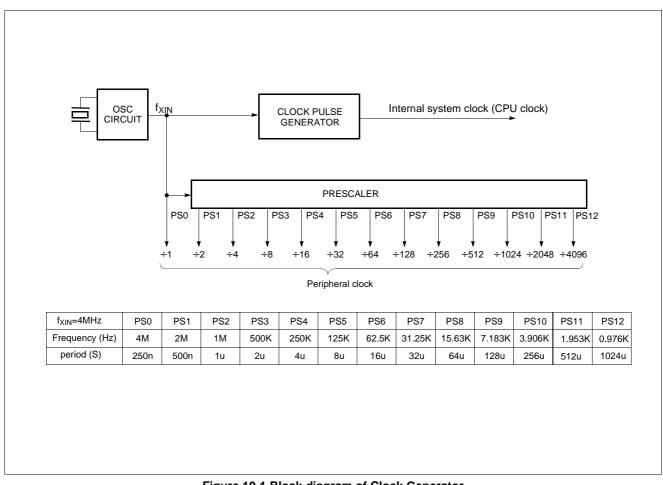

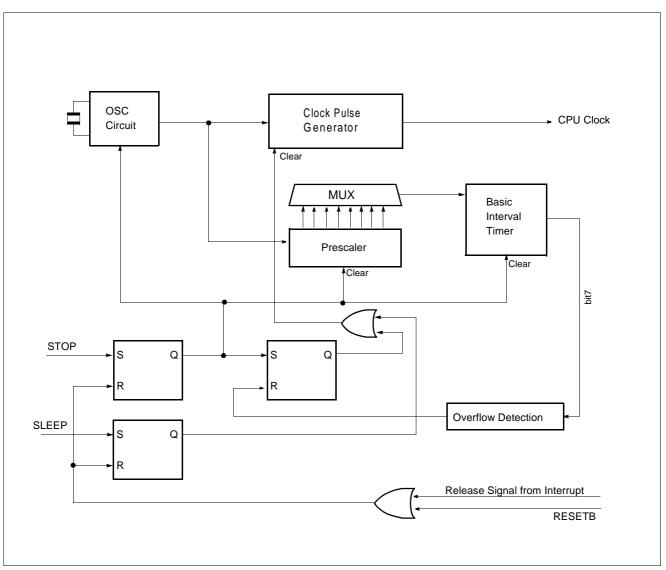

# **10. CLOCK GENERATOR**

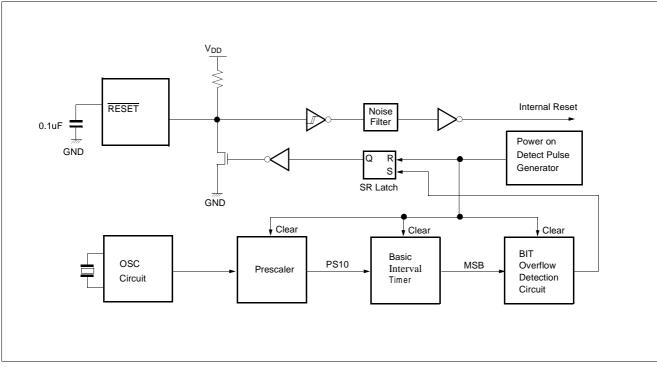

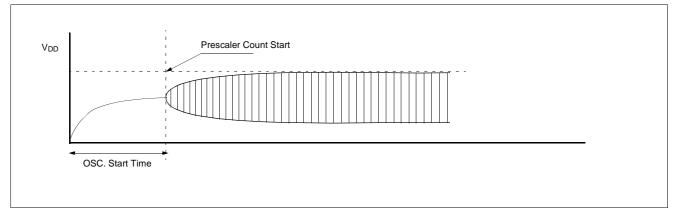

The Clock generating circuit consists of Clock Pulse Generator (C.P.G), Prescaler, Basic Interval Timer (BIT) and Watch Dog Timer. The clock applied to the Xin pin divided by two is used as the internal system clock.

Prescaler consist of 12-bit binary counter. The clock supplied from oscillation circuit is input to  $prescaler(f_{XIN})$

The divided output from each bit of prescaler is provided to peripheral hardware

Clock to peripheral hardware can be stopped by bit4 (EN-PCK) of CKCTLR Register. ENPCK is set to "1" in reset

Figure 10-1 Block diagram of Clock Generator

#### **10.1 Oscillation Circuit**

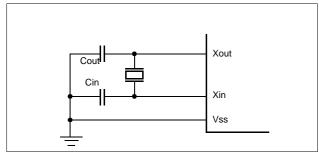

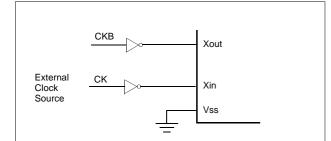

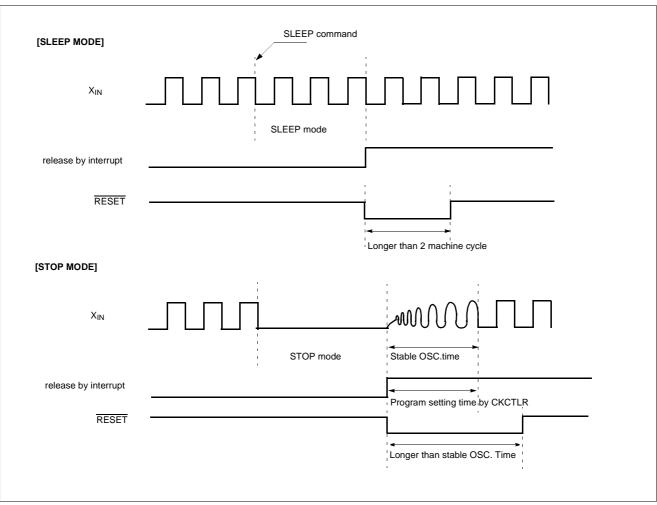

Oscillation circuit is designed to be used either with a ceramic resonator or crystal oscillator. Figure 10-2 shows circuit diagrams using a crystal (or ceramic) oscillator. As shown in the diagram, oscillation circuits can be constructed by connecting a oscillator between Xout and Xin. Clock from oscillation circuit makes CPU clock via clock pulse generator, and then enters prescaler to make peripheral hardware clock. Alternately, the oscillator may be driven from an external source as Figure 10-3. In the STOP mode, oscillation stop, Xout state goes to "Low", Xin state goes to "LOW", and built-in feed back resistor is disabled.

Figure 10-2 External Crystal(Ceramic) oscillator circuit

Figure 10-3 External clock input circuit

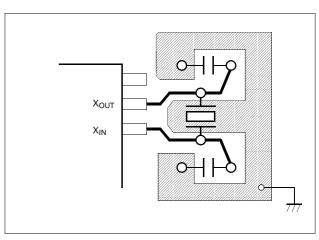

Oscillation circuit is designed to be used either with a ceramic resonator or crystal oscillator. Since each crystal and ceramic resonator have their own characteristics, the user should consult the crystal manufacturer for appropriate values of external components. In addition, see Figure 10-4 for the layout of the crystal.

**Note:** Minimize the wiring length. Do not allow the wiring to intersect with other signal conductors. Do not allow the wiring to come near changing high current. Set the potential of the grounding position of the oscillator capacitor to that of Vss. Do not ground it to any ground pattern where high current is present. Do not fetch signals from the oscillator.

Figure 10-4 Recommend Layout of Oscillator PCB circuit

| Frequency | Resonator Maker | Part Name       | Load Capacitor | Operating Voltage(V) |

|-----------|-----------------|-----------------|----------------|----------------------|

|           | CQ              | ZTA2.00M        | Cin=Cout=33pF  | 2.0~4.0              |

| 2.00MHz   | MURATA          | CSTCC2M00G56-R0 | Cin=Cout=open  | 2.0~4.0              |

|           | MURATA          | CSTCC2.00MG0H6  | Cin=Cout=open  | 2.0~4.0              |

|           | CQ              | ZTA4.00M        | Cin=Cout=33pF  | 2.0~4.0              |

|           | MURATA          | CSTS0400MG03    | Cin=Cout=open  | 2.0~4.0              |

| 4.00MHz   | MURATA          | CSTLS4M00G53-B0 | Cin=Cout=open  | 2.0~4.0              |

|           | MURATA          | CSTCR4M00G53-R0 | Cin=Cout=open  | 2.0~4.0              |

|           | TDK             | FCR4.0MC5       | Cin=Cout=open  | 2.0~4.0              |

Table 10-1 recommendation resonator

# **11. BASIC INTERVAL TIMER**

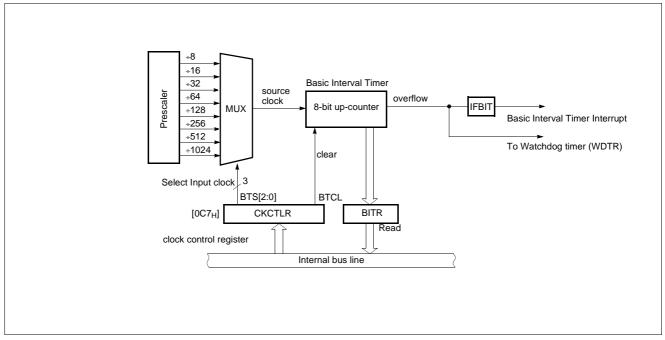

The HMS81020ET/HMS81032ET has one 8-bit Basic Interval Timer that is free-run and can not stop. Block diagram is shown in Figure 11-1.

The Basic Interval Timer generates the time base for Standby release time, watchdog timer counting, and etc. It also provides a Basic interval timer interrupt (IFBIT). As the count overflow from  $FF_H$  to  $00_H$ , this overflow causes the interrupt to be generated.

-8bit binary up-counter

-Use the bit output of prescaler as input to secure the oscillation stabilization time after power-on

-Secures the oscillation stabilization time in standby mode (stop mode) release

-Contents of BIT can be read

-Provides the clock for watch dog timer

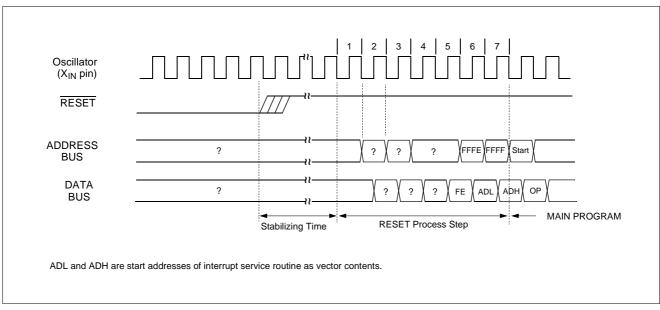

The Basic Interval Timer is controlled by the clock control register (CKCTLR) shown in Figure 11-2. If bit3(BTCL) of CKCTLR is set to "1", BIT is cleared, and then, after one machine cycle, BTCL becomes "0", and BIT starts counting. BTCL is set to ``0`` in reset state.

The input clock of BIT can be selected from the prescaler within a range of 2us to 256us by clock input selection bits (BTS2~BTS0). (at  $f_{XIN} = 4$ MHz). In reset state, or power on reset, BTS2="1", BTS1= "1", BTS0= "1" to secure the longest oscillation stabilization time. BIT can generate the wide range of basic interval time interrupt request (IFBIT) by selecting prescaler output.

By reading of the Basic Interval Timer Register (BITR), we can read counter value of BIT Because BIT can be cleared or read, the spending time up to maximum 65.5ms can be available. BIT is read-only register. If BIT register is written, then CKCTLR register with same address is written.

Figure 11-1 Block diagram of Basic Interval Timer

## Figure 11-2 CKCTLR AND BITR

| BTS[2:0] | CPU Source clock | BIT Input clock@4MHz(us) | Standby release time(ms) |

|----------|------------------|--------------------------|--------------------------|

| 000      | ÷8               | 2                        | 0.512                    |

| 001      | ÷16              | 4                        | 1.024                    |

| 010      | ÷32              | 8                        | 2.048                    |

| 011      | ÷64              | 16                       | 4.096                    |

| 100      | ÷128             | 32                       | 8.192                    |

| 101      | ÷256             | 64                       | 16.384                   |

| 110      | ÷512             | 128                      | 32.768                   |

| 111      | ÷1024            | 256                      | 65.536                   |

Table 11-1 Standby release time according to BTS

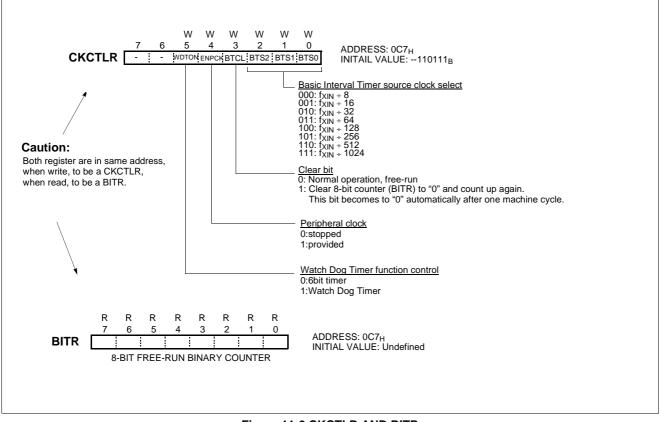

# **12. WATCH DOG TIMER**

Watch Dog Timer (WDT) consists of 6-bit binary counter, 6-bit comparator, and Watch Dog Timer Register (WDTR).Watch Dog Timer can be used 6-bit general Timer or specific Watch dog timer by setting bit5 (WDTON) of Clock Control Register (CKCTLR).By assigning bit6(WDTCL) of WDTR, 6-bit counter can be cleared.

WDT Interrupt (IFWDT) interval is determined by the interrupt IFBIT interval of Basic Interval Timer and the value of WDT Register.

-Interval of IFWDT = (IFBIT interval)  $\times$  (WDTR value)

As IFBIT (Basic Interval Timer Interrupt Request) is used for input clock of WDT, Input clock cycle is possible from 512 us to 65,536 us by BTS. (at  $f_{XIN} = 4$ MHz)

\*At Hardware reset time, WDT starts automatically. Therefore the user must select the CKCTLR and WDTR before WDT overflow.

-Reset WDTR value =  $0F_h=15$

-Interval of WDT =  $65,536 \times 15 = 983,040$  us

(about 1second)

Figure 12-1 Block diagram of Watch Dog Timer

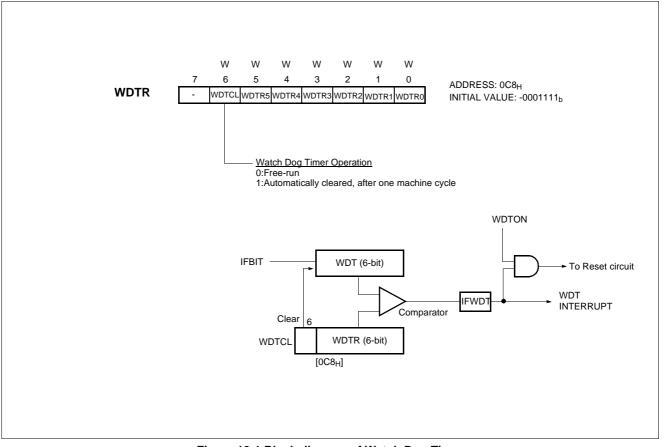

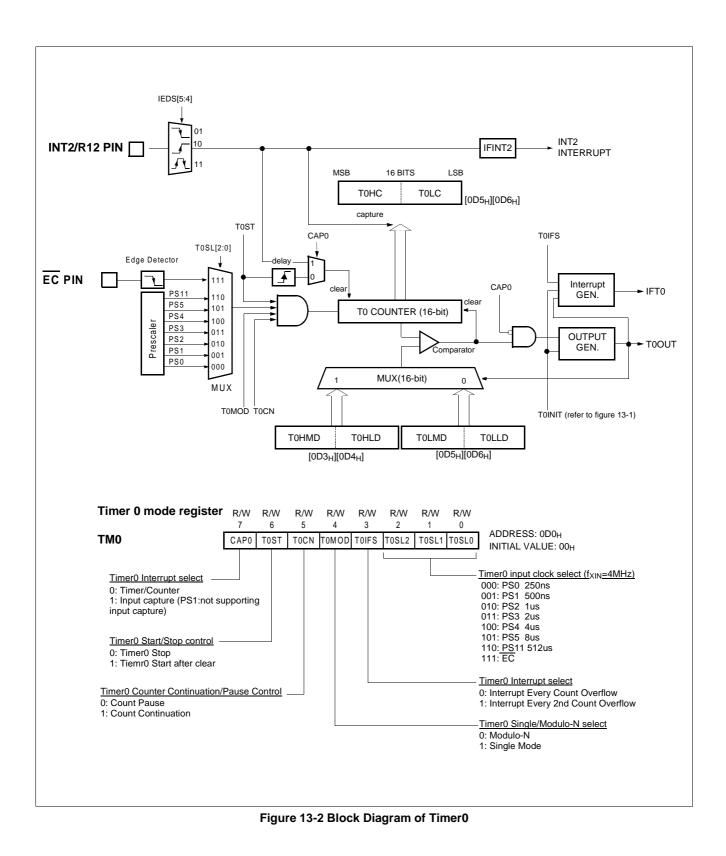

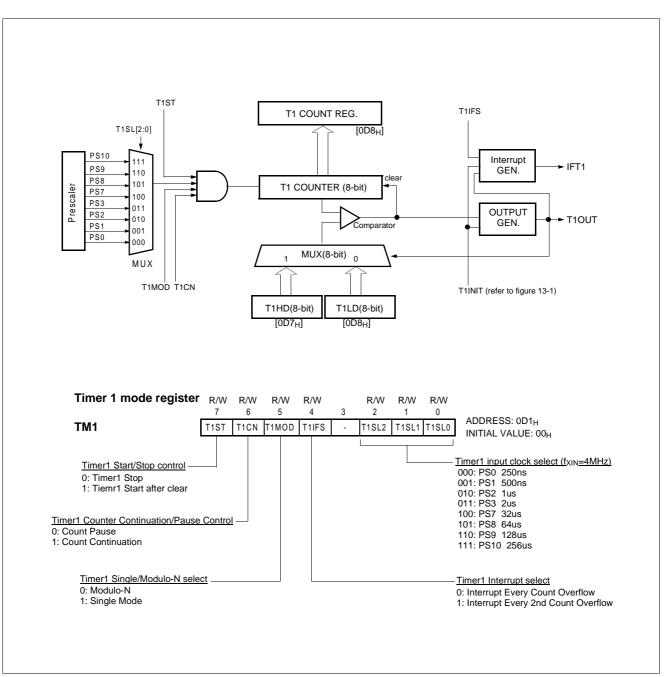

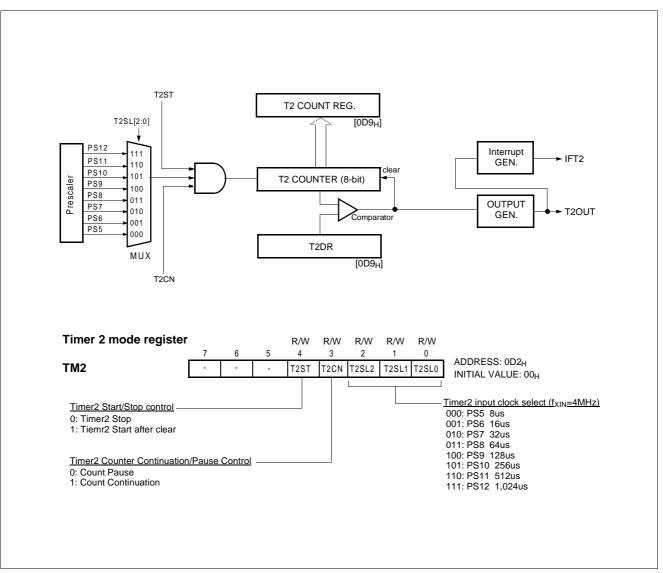

# 13. Timer0, Timer1, Timer2

## (1) Timer Operation Mode

Timer consists of 16bit binary counter Timer0 (T0), 8bit binary Timer1 (T1), Timer2 (T2), Timer Data Register, Timer Mode Register (TM01, TM0, TM1, TM2) and control circuit. Timer Data Register Consists of Timer0 High-MSB Data Register (T0HMD), Timer0 High-LSB Data Register (T0HLD), Timer0 Low-MSB Data Register (T0LMD), Timer0 Low-LSB Data Register (T0LLD), Timer1 High Data Register (T1HD), Timer1 Low Data Register (T1LD), Timer2 Data Register (T2DR). Any of the PS0 ~ PS5, PS11 and external event input  $\overline{\text{EC}}$  can be selected as clock source for T0. Any of the PS0 ~ PS3, PS7 ~ PS10 can be selected as clock T1. Any of the PS5 ~ PS12 can be selected as clock source for T2.

\* Relevant Port Mode Register (PMR1: 00C9h) value should be assigned for event counter.

| Timer0 | <ul> <li>16-bit Interval Timer</li> <li>16-bit Event Counter</li> <li>16-bit Input Capture</li> <li>16-bit rectangular-wave output</li> </ul> | <ul> <li>Single/Modulo-N Mode</li> <li>Timer Output Initial Value Setting</li> <li>Timer0~Timer1 combination Logic Output</li> <li>One Interrupt Generating Every 2nd</li> </ul> |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Timer1 | <ul> <li>8-bit Interval Timer</li> <li>8-bit rectangular-wave output</li> </ul>                                                               | Counter Overflow                                                                                                                                                                 |  |

| Timer2 | - 8-bit Interval Timer<br>- 8-bit rectangular-wave output<br>- Modulo-N Mode                                                                  |                                                                                                                                                                                  |  |

#### **Table 13-1 Timer Operation**

| 16bit Timer 0 (f <sub>XIN</sub> =4MHz) |              | 8bit Timer   | 8bit Timer 1 (f <sub>XIN</sub> =4MHz) |               | 8bit Timer 2 (f <sub>XIN</sub> =4MHz) |  |

|----------------------------------------|--------------|--------------|---------------------------------------|---------------|---------------------------------------|--|

| Resolution                             | MAX. Count   | Resolution   | MAX. Count                            | Resolution    | MAX. Count                            |  |

| PS0 (0.25us)                           | 16,384us     | PS0 (0.25us) | 64us                                  | PS5 (8us)     | 2,048us                               |  |

| PS1 (0.5us)                            | 32,768us     | PS1 (0.5us)  | 128us                                 | PS6 (16us)    | 4,096us                               |  |

| PS2 (1us)                              | 65,536us     | PS2 (1us)    | 256us                                 | PS7 (32us)    | 8,192us                               |  |

| PS3 (2us)                              | 131,072us    | PS3 (2us)    | 512us                                 | PS8 (64us)    | 16,384us                              |  |

| PS4 (4us)                              | 262,144us    | PS7 (32us)   | 8,192us                               | PS9 (128us)   | 32,768us                              |  |

| PS5 (8us)                              | 524,288us    | PS8 (64us)   | 16,384us                              | PS10 (256us)  | 65,536us                              |  |

| PS11 (512us)                           | 33,554,432us | PS9 (128us)  | 32,768us                              | PS11 (512us)  | 131,072us                             |  |

| EC                                     | -            | PS10 (256us) | 65,536us                              | PS12 (1024us) | 262,144us                             |  |

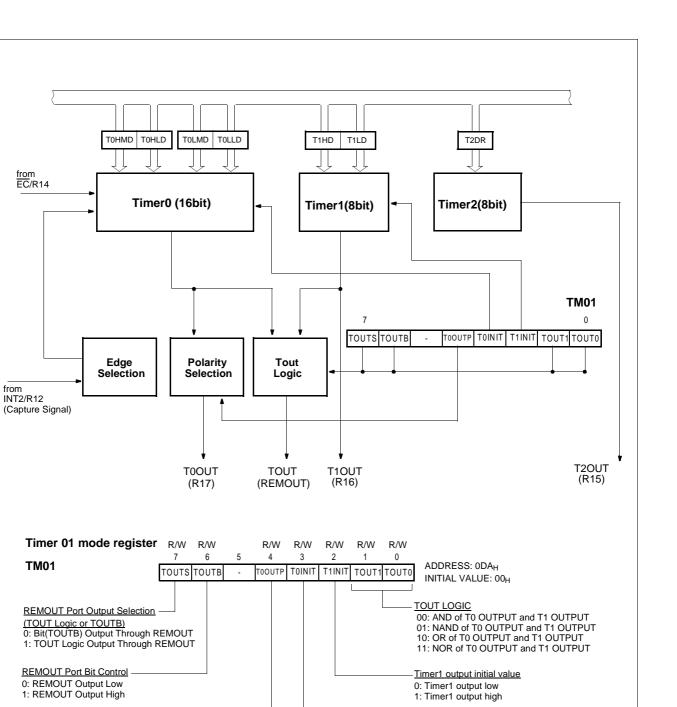

Table 13-2 Function of Timer & Counter

TOOUT Polarity Selection

0: T0OUT Polarity Equal to TOUT Logic input signal

1: T0OUT Polarity Reverse to TOUT Logic input signal

Figure 13-1 Block Diagram of Timer/Counter

Timer0 output initial value 0: Timer0 output low

1: Timer0 output high

hynix

# идиіх

Figure 13-3 Block Diagram of Timer1

идиіх

# идиіх

Figure 13-4 Block Diagram of Timer2

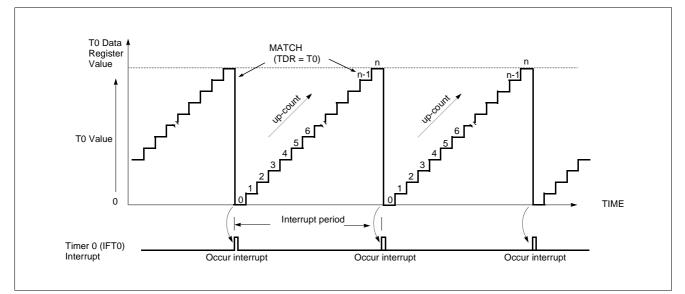

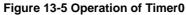

# 2) Timer0, Timer1

TIMER0 and TIMER1 have an up-counter. When value of the up-counter reaches the content of Timer Data Register

(TDR), the up-counter is cleared to "00h", and interrupt (IFT0, IFT1) is occurred at the next clock.

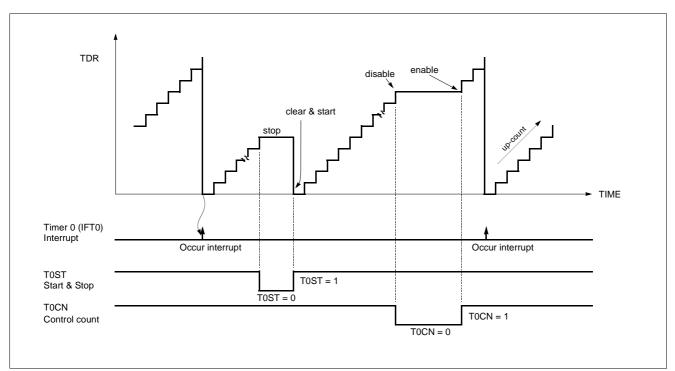

For Timer0, the internal clock (PS) and the external clock  $\overline{(EC)}$  can be selected as counter clock. But Timer1 and Timer2 use only internal clock. As internal clock is chosen, Timer0 can be used as internal-timer which period is determined by Timer Data Register (TDR). Chosen as external clock, Timer0 executes as event-counter. The counter execution of Timer0 and Timer1 is controlled by T0CN, T0ST, CAP0, T1CN, T1ST, of Timer Mode Register TM0 and TM1. T0CN, T1CN are used to stop and start Timer0 and Timer1 without clearing the counter. T0ST, T1ST is

used to clear the counter. For clearing and starting the counter, TOST or T1ST should be temporarily set to "0" and then set to "1". TOCN, T1CN, TOST and T1ST should be set "1", when Timer counting-up. Controlling of CAPO enables Timer0 as input capture. By programming of CAP0 to "1", the period of signal from INT2 can be measured and then, event counter value for INT2 can be read. During counting-up, value of counter can be read. Timer execution is stopped by the reset signal (RESET="L")

Figure 13-6 Start/Stop Operation of Timer0

Figure 13-7 Input capture operation of Timer0

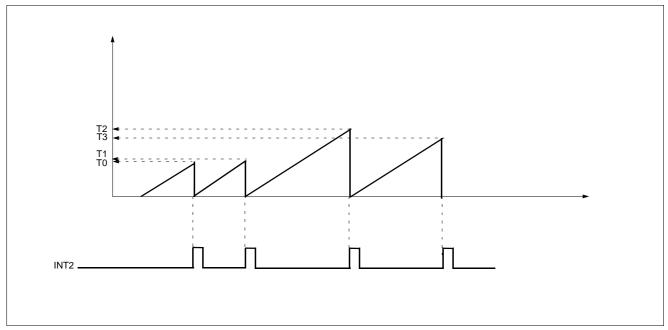

#### 3) Single/Modulo-N Mode

Timer0 (Timer1) can select initial output level of Timer Output port by T0INIT, T1INIT of TM01. If initial level is "L", Low-Data Register value of Timer Data Register is transferred to comparator and T0OUT (T1OUT) is to be "Low". If initial level is "High", High -Data Register is transferred and to be "High". Single Mode can be set by Mode Select bit (T0MOD, T1MOD) of Timer Mode Register (TM0, TM1) to "1". When used as Single Mode, Timer counts up and compares with value of Data Register. If the result is same, Time Out interrupt occurs and level of Timer Output port toggle, then counter stops as reset state. When used as Modulo-N Mode, T0MOD (T1MOD) should be set "0". Counter counts up until the value of Data Register and occurs Time-out interrupt. The level of Timer Output port toggle and repeats process of counting the value which is selected in Data Register. During Modulo-N Mode, If interrupt select bit (T0IFS, T1IFS) of Mode Register is "0", Interrupt occurs on every time-out. If it is "1", Interrupt occurs every second time-out.Timer output is toggled whenever time-out happen.

Figure 13-8 Operation Diagram for Single/Modulo-N Mode

## (4) Timer 2

Timer2 operates as an up-counter. The contents of T2DR are compared with the contents of up-counter. If a match is found, Timer2 interrupt (IFT2) is generated and the up-counter is cleared to "00h". Therefore, Timer2 executes as a interval timer. Interrupt period is determined by the count source clock for the Timer2 and contents of T2DR.

When T2ST is set to "1", count value of Timer 2 is cleared and starts counting-up. For clearing and starting the Timer2, T2ST have to set to "1" after set to "0". In order to write a value directly into the T2DR, T2ST should be set to "0". Counted value of Timer2 can be read at any time.

# **14. INTERRUPTS**

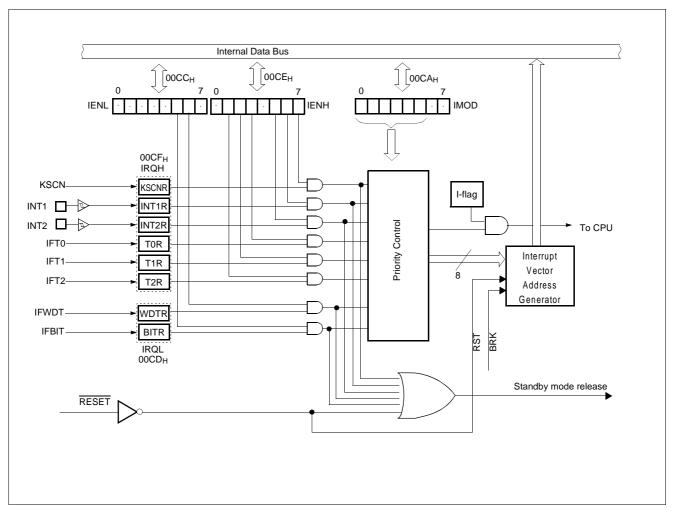

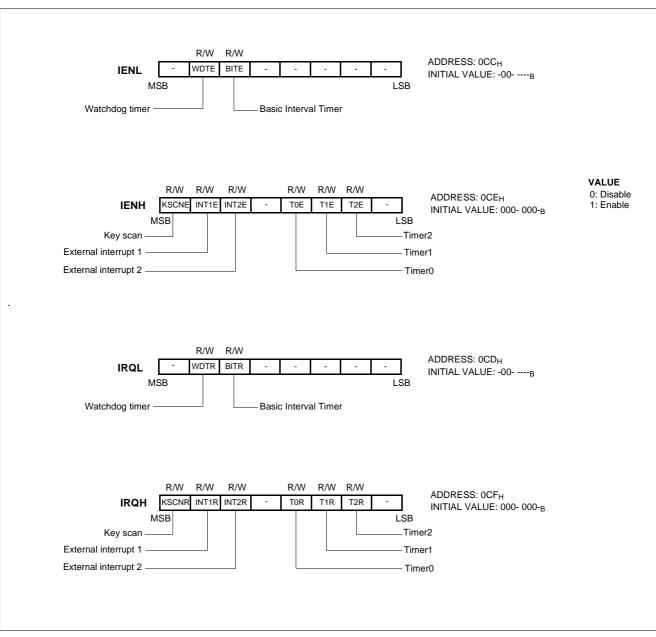

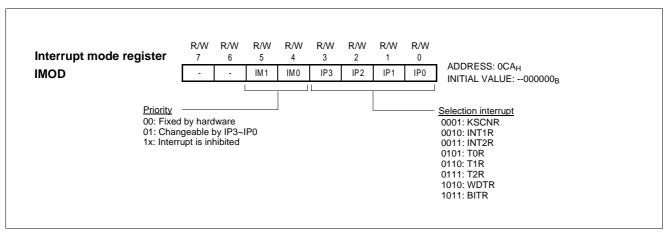

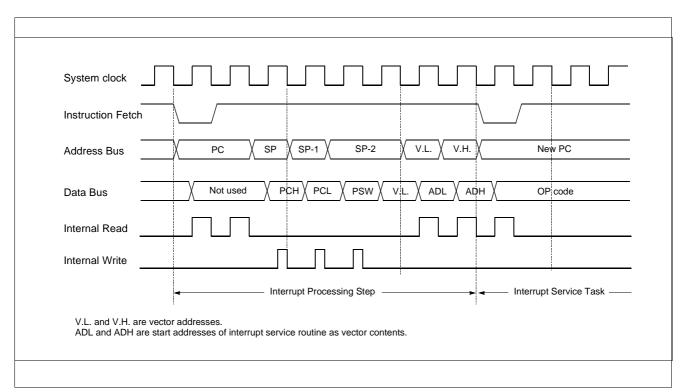

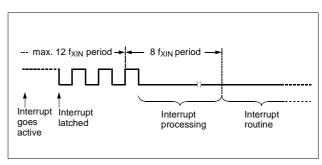

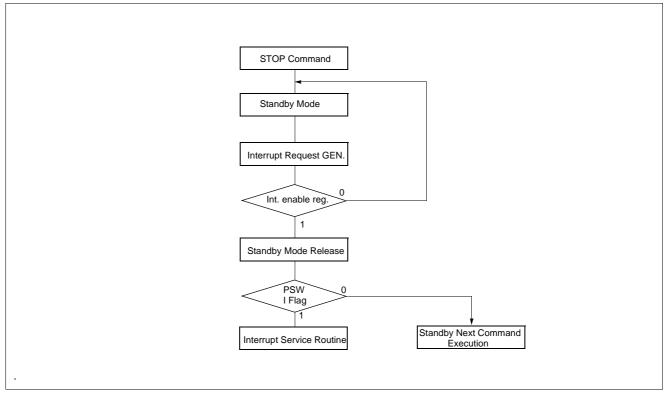

The HMS81020ET/HMS81032ET interrupt circuits consist of Interrupt Mode Register (MOD), Interrupt enable register (IENH, IENL), Interrupt request flags of IRQH, IRQL, Priority circuit and Master enable flag ("I" flag of PSW). 8 interrupt sources are provided. The configuration of interrupt circuit is shown in Figure 14-1.

The HMS81020ET/HMS81032ET contains 8 interrupt sources; 3 externals and 5 internals. Nested interrupt services with priority control is also possible. Software interrupt is non-maskable interrupt, the others are all maskable interrupts.

- 8 interrupt source (2Ext, 3Timer, BIT, WDT and Key Scan)

- 8 interrupt vector

- Nested interrupt control is possible

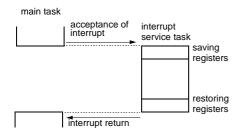

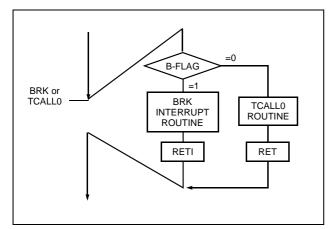

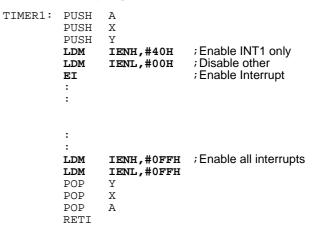

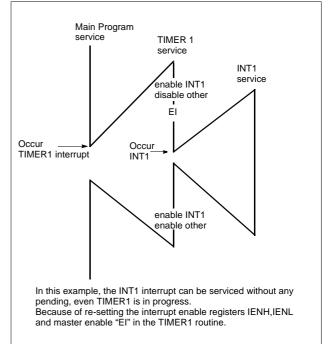

- Programmable interrupt mode (Hardware and software interrupt accept mode)