# **USER'S MANUAL**

# S3C2416 16/32-Bit RISC Microprocessor

July 2009

**REV 1.40**

Confidential Proprietary of Samsung Electronics Co., Ltd Copyright © 2009 Samsung Electronics, Inc. All Rights Reserved

# **Important Notice**

The information in this publication has been carefully checked and is believed to be entirely accurate at the time of publication. Samsung assumes no responsibility, however, for possible errors or omissions, or for any consequences resulting from the use of the information contained herein.

Samsung reserves the right to make changes in its products or product specifications with the intent to improve function or design at any time and without notice and is not required to update this documentation to reflect such changes.

This publication does not convey to a purchaser of semiconductor devices described herein any license under the patent rights of Samsung or others.

Samsung makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Samsung assume any liability arising out of the application or use of any product or circuit and specifically disclaims any and all liability, including without limitation any consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts.

Samsung products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, for other applications intended to support or sustain life, or for any other application in which the failure of the Samsung product could create a situation where personal injury or death may occur.

Should the Buyer purchase or use a Samsung product for any such unintended or unauthorized application, the Buyer shall indemnify and hold Samsung and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, expenses, and reasonable attorney fees arising out of, either directly or indirectly, any claim of personal injury or death that may be associated with such unintended or unauthorized use, even if such claim alleges that Samsung was negligent regarding the design or manufacture of said product.

S3C2416 16/32-Bit RISC Microprocessor User's Manual, Revision 1.40 Publication Number: 21.10-S3-C2416- 082008

Copyright © 2009 Samsung Electronics Co.,Ltd.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior written consent of Samsung Electronics.

Samsung Electronics' microcontroller business has been awarded full ISO-14001 certification (BSI Certificate No. FM24653). All semiconductor products are designed and manufactured in accordance with the highest quality standards and objectives.

Samsung Electronics Co., Ltd. San #24 Nongseo-Dong, Giheung-Gu Yongin-City, Gyeonggi-Do, Korea C.P.O. Box #37, Suwon 446-711

TEL: (82)-(31)-209-4593 FAX: (82)-(31)-209-5324

Home Page: http://www.samsungsemi.com Printed in the Republic of Korea E-Mail: mobilesol.cs@samsung.com

# **NOTIFICATION OF REVISIONS**

| ORIGINATOR:      | Samsung Electronics, LSI Development Group, Gi-Heung, South Korea |

|------------------|-------------------------------------------------------------------|

| PRODUCT NAME:    | S3C2416 RISC Microprocessor                                       |

| DOCUMENT NAME:   | S3C2416 User's Manual, Revision 1.40                              |

| DOCUMENT NUMBER: | 21.10-S3-C2416-082008                                             |

| EFFECTIVE DATE:  | JULY, 2009                                                        |

| DIRECTIONS:      | Revision 1.40                                                     |

# **REVISION HISTORY**

| <b>Revision No</b> | Description of Change                                                               | Refer to | Author(s)    | Date             |

|--------------------|-------------------------------------------------------------------------------------|----------|--------------|------------------|

| 1.00               | Initial release                                                                     | -        | AP app part. | August 27, 2008  |

| 1.10               | Overview, System controller, DMA controller, I/O ports, LCD controller are updated. | -        | AP app part. | October 06, 2008 |

| 1.20               | Overview, 2D, I/O port are updated.                                                 | -        | AP app part. | January 5, 2009  |

| 1.30               | LCD Controller, SMC, HSSPI, Electrical data are updated                             | -        | AP app part. | March 16, 2009   |

| 1.40               | HSMMC, DRAMC, DMAC, USB Device,<br>Electrical Data are updated                      | -        | AP app part. | July 31, 2009    |

# **REVISION DESCRIPTIONS FOR REVISION 1.40**

| Chapter             |       | Subjects (Major changes comparing with last version)                |  |

|---------------------|-------|---------------------------------------------------------------------|--|

| Chapter Name        | Page  | Subjects (major changes comparing with last version)                |  |

| 6. DRAMC            | 6-8   | CASBW0/CASBW1 descriptions are modified                             |  |

| 8. DMA CONTROLLER   | 8-8   | Note is added                                                       |  |

| 16. USB 2.0 Device  | 16-30 | Note is added                                                       |  |

| 20. HSMMC           | 20-36 | HOSTCTL0/1[2] is changed to OUTEDGEINV                              |  |

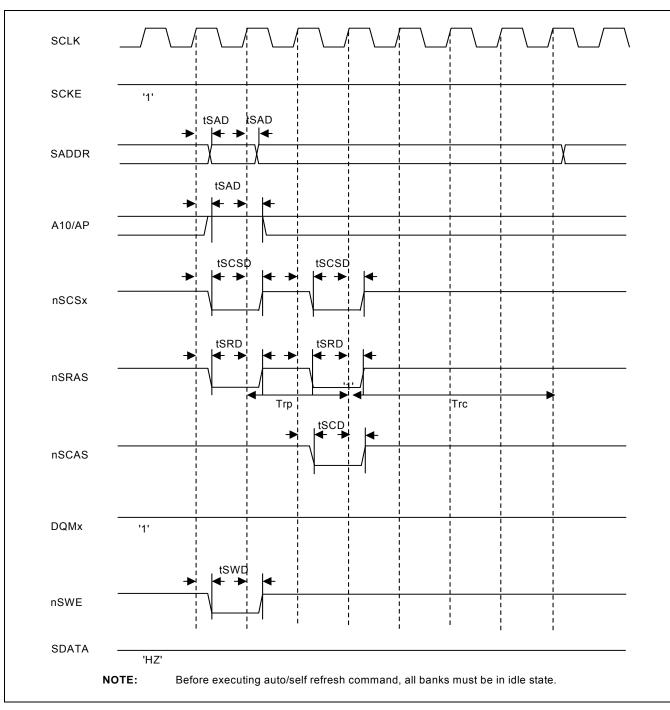

| 26. Electrical data | 26-23 | SMC Timing Constants are modified                                   |  |

| 26. Electrical data | 26-2  | Recommended operating conditions (400 or 266MHz) Table is modified. |  |

# **Table of Contents**

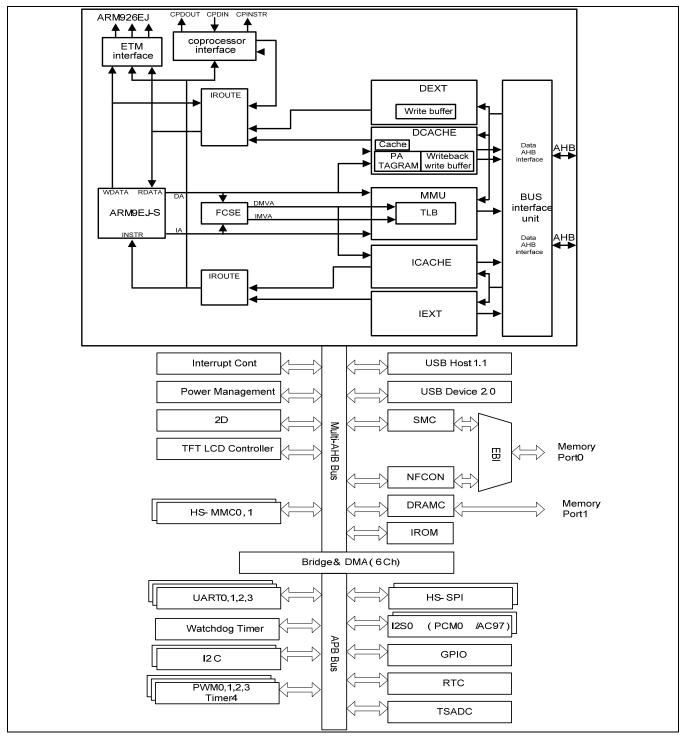

# Chapter 1 Product Overview

| 1 Introduction                                               | 1-1 |

|--------------------------------------------------------------|-----|

| 2 Features                                                   | 1-2 |

| 3 Block Diagram                                              | 1-5 |

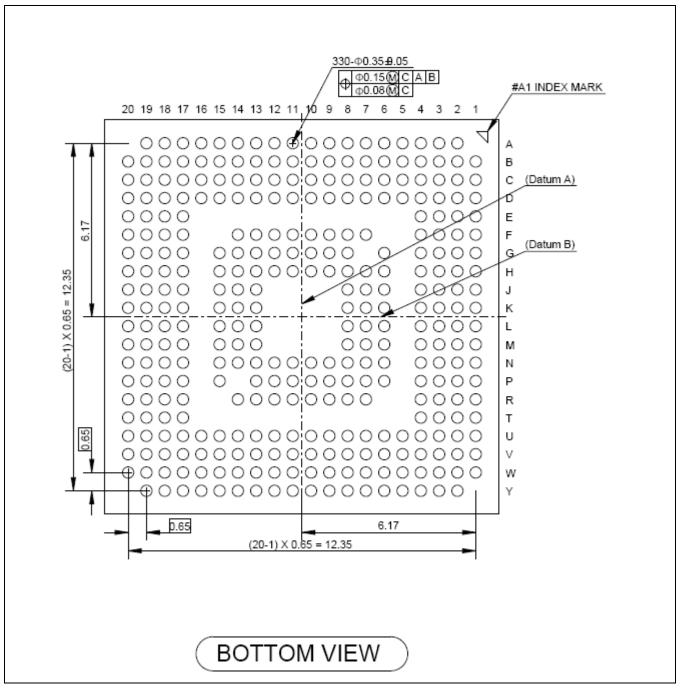

| 4 Pin Assignments                                            | 1-6 |

| 4.1 Signal Descriptions                                      |     |

| 4.2 S3C2416 Operation Mode Description                       |     |

| 4.3 S3C2416 Memory MAP and Base Address of Special Registers |     |

|                                                              |     |

# Chapter 2 System Controller

| 1 Overview                                                                              | 2-1  |

|-----------------------------------------------------------------------------------------|------|

| 2 Feature                                                                               | 2-1  |

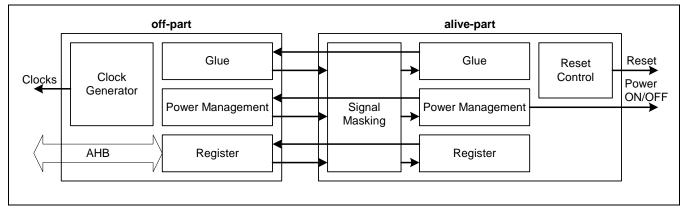

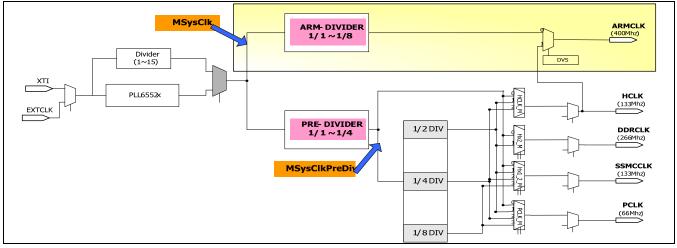

| 3 Block Diagram                                                                         | 2-2  |

| 4 Functional Descriptions                                                               | 2-3  |

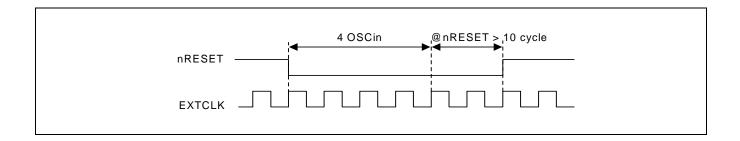

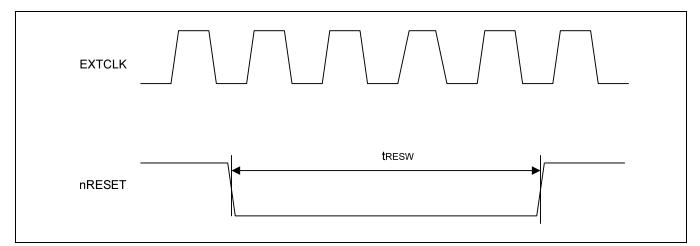

| 4.1 Reset Management and Types                                                          | 2-3  |

| 4.2 Hardware Reset                                                                      | 2-3  |

| 4.3 Watchdog Reset                                                                      | 2-4  |

| 4.4 Software Reset                                                                      | 2-5  |

| 4.5 Wakeup Reset                                                                        | 2-5  |

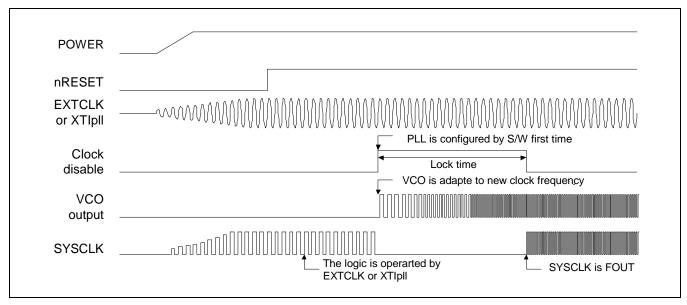

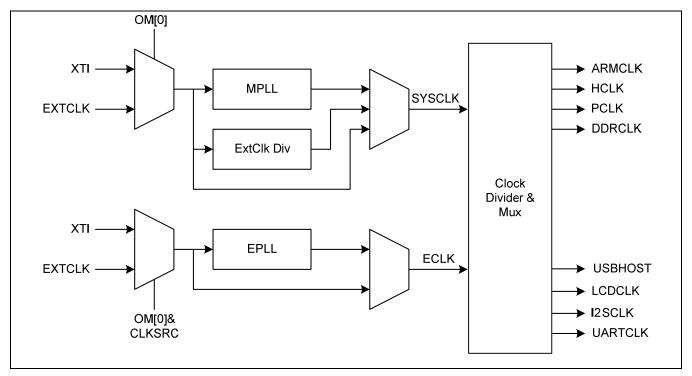

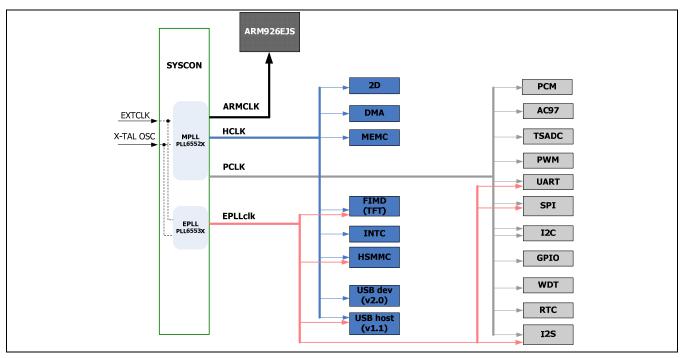

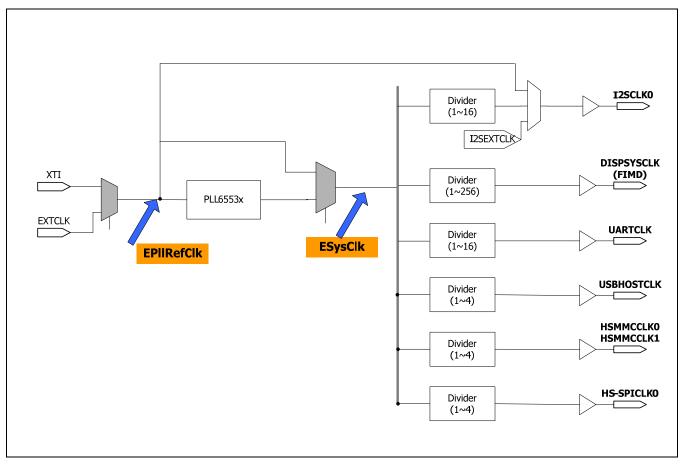

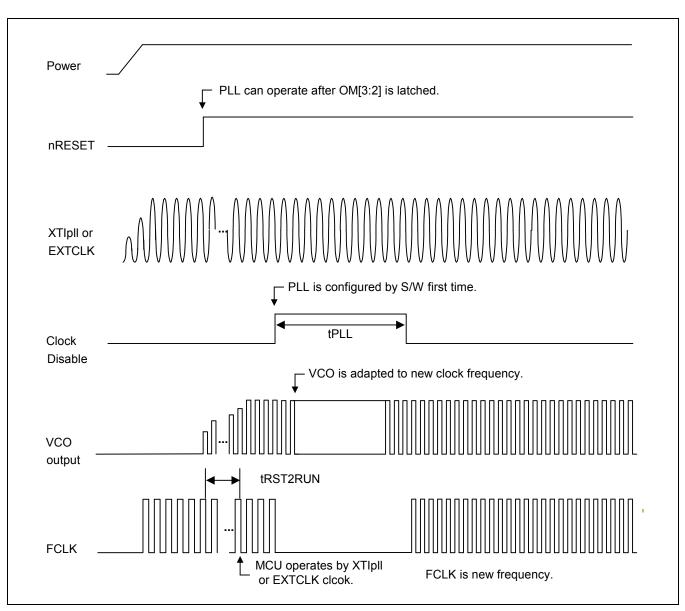

| 5 Clock Management                                                                      | 2-6  |

| 5.1 Clock Generation Overview                                                           |      |

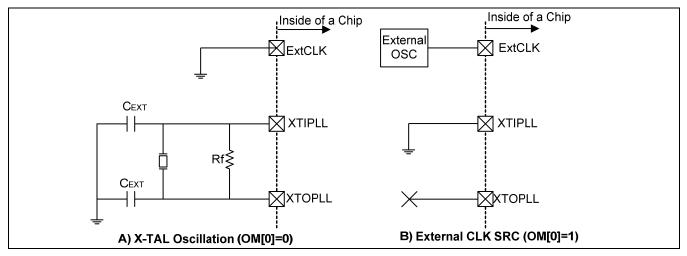

| 5.2 Clock Source Selection                                                              | 2-6  |

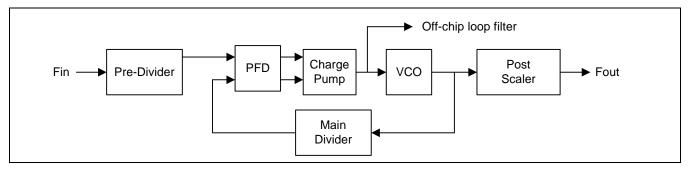

| 5.3 PLL (Phase-Locked-Loop)                                                             |      |

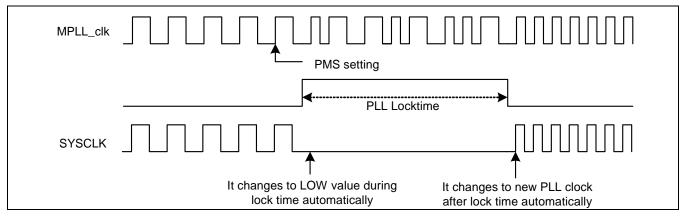

| 5.4 Change PLL Settings In Normal Operation                                             | 2-8  |

| 5.5 System Clock Control                                                                |      |

| 5.6 ARM & BUS Clock Divide Ratio                                                        |      |

| 5.7 Examples for configuring clock regiter to produce specific frequency of AMBA clocks | 2-11 |

| 5.8 ESYSCLK Control                                                                     | 2-12 |

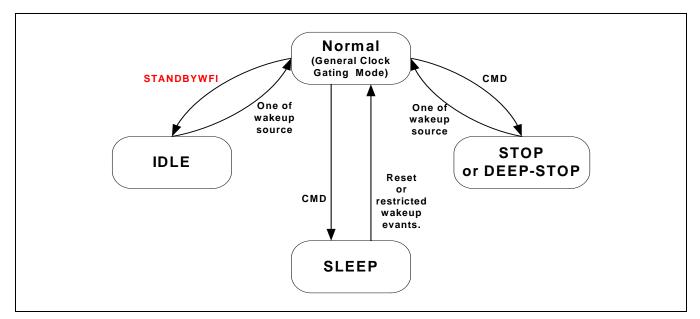

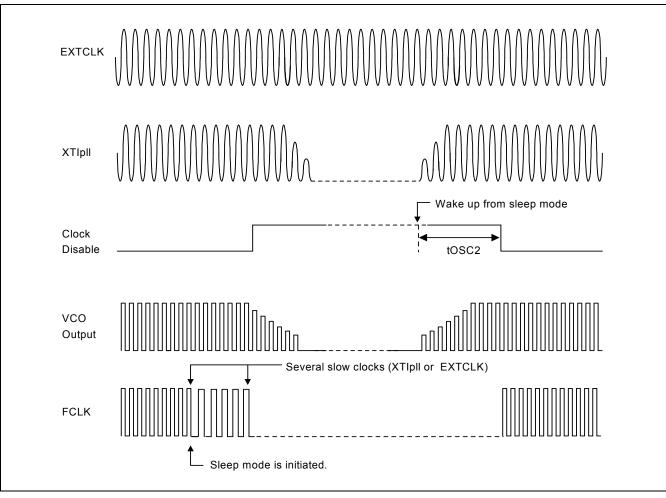

| 6 Power Management                                                                      |      |

| 6.1 Power Mode State Diagram                                                            |      |

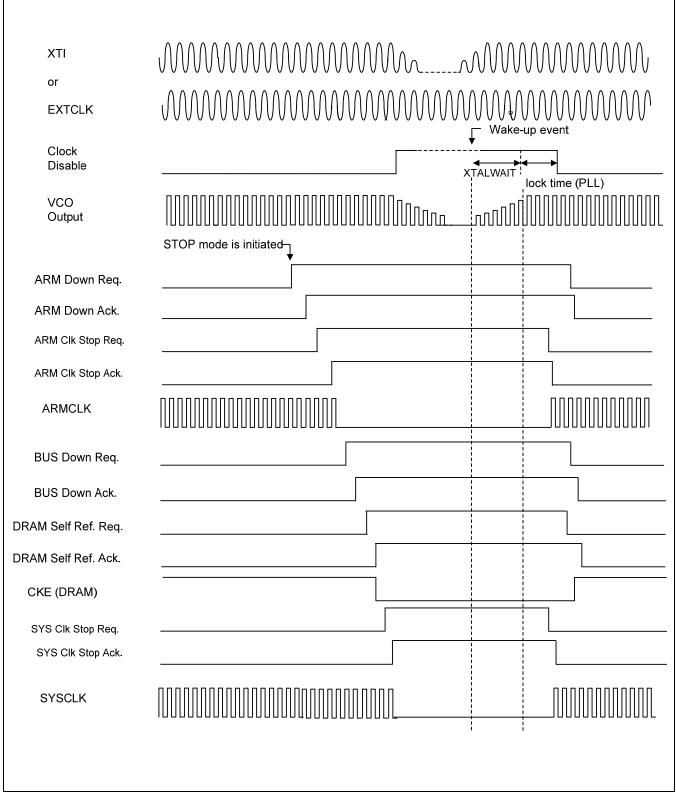

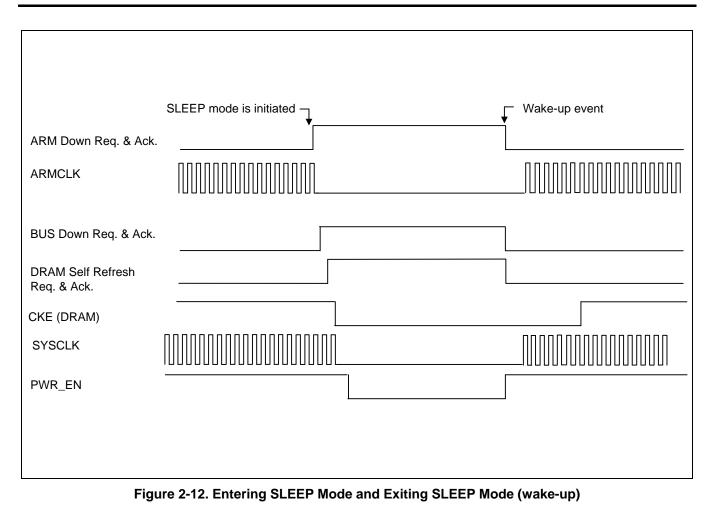

| 6.2 Power Saving Modes                                                                  |      |

| 6.3 Wake-Up Event                                                                       |      |

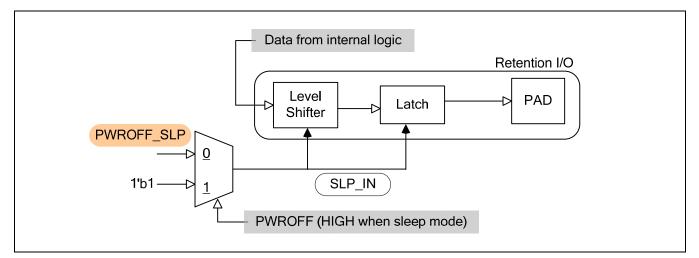

| 6.4 Output Port State and STOP and SLEEP Mode                                           |      |

| 6.5 Power Saving Mode Entering/Exiting Condition                                        |      |

| 7 Register Descriptions                                                                 |      |

| 7.1 Address Map                                                                         | 2-21 |

|                                                                                         |      |

### Chapter 2 System Controller (Continued)

| 8 Individual Register Descriptions                                             | 2-22 |

|--------------------------------------------------------------------------------|------|

| 8.1 Clock Source Control Registers                                             |      |

| (LOCKCON0, LOCKCON1, OSCSET, MPLLCON, and EPLLCON)                             | 2-22 |

| 8.2 Clock Control Register (CLKSRC, CLKDIV, HCLKCON, PCLKCON, and SCLKCON)     | 2-25 |

| 8.3 Power Management Registers (PWRMODE and PWRCFG)                            | 2-31 |

| 8.4 Reset Control Registers (SWRST and RSTCON)                                 | 2-33 |

| 8.5 Control of retention PAD(I/O) when normal mode and wake-up from sleep mode | 2-34 |

| 8.6 System Controller Status Registers (WKUPSTAT and RSTSTAT)                  | 2-35 |

| 8.7 Bus Configuration Register (BUSPRI0, BUSPRI1, and BUSMISC)                 | 2-36 |

| 8.8 Information Register 0,1,2,3                                               | 2-37 |

| 8.9 USB PHY Control register (PHYCTRL)                                         | 2-38 |

| 8.10 USB PHY Power Control Register (PHYPWR)                                   | 2-39 |

| 8.11 USB Reset Control Register (URSTCON)                                      |      |

| 8.12 USB Clock Control Register (UCLKCON)                                      | 2-40 |

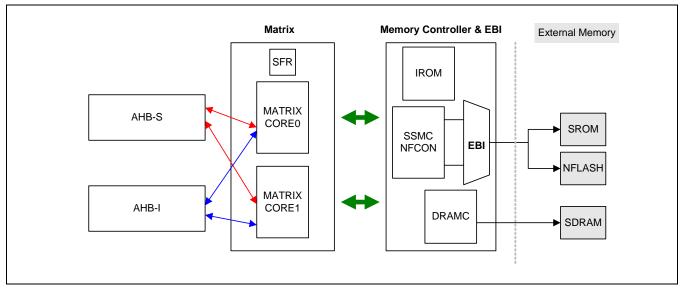

### Chapter 3 Bus Matrix & EBI

| 1 Overview                                       | 3-1 |

|--------------------------------------------------|-----|

| 2 Special Function Registers                     | 3-2 |

| 2.1 Matrix Core 0 Priority Register (Bpriority0) |     |

| 2.2 Matrix Core 1 Priority Register (Bpriority1) |     |

| 2.3 EBI Control Register (EBICON)                |     |

|                                                  |     |

### Chapter 4 Bus Priorities

| Overview             | 4-1 |

|----------------------|-----|

| 1.1 Bus Priority MAP | 4-1 |

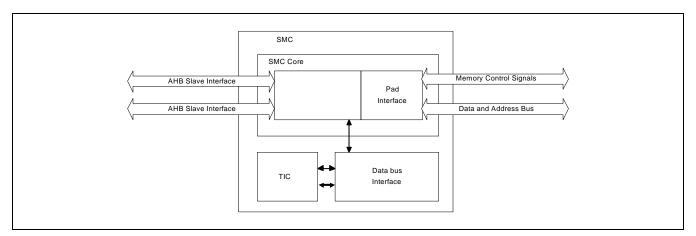

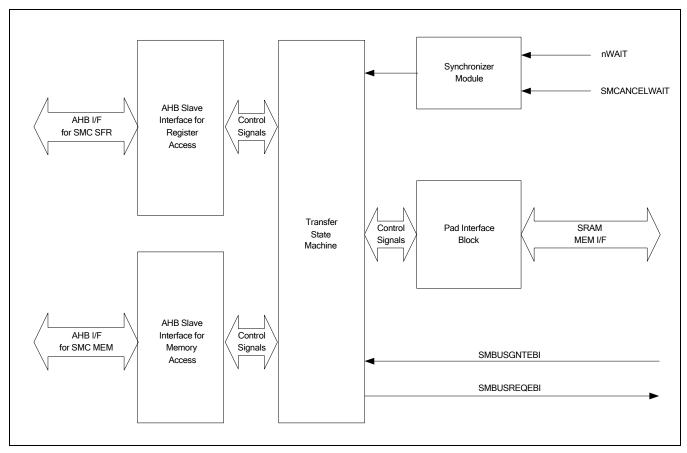

| Chapter 5 | <b>Static Memory</b> | Controller | (SMC) |

|-----------|----------------------|------------|-------|

|-----------|----------------------|------------|-------|

| 1 Overview                                                   | 5-1  |

|--------------------------------------------------------------|------|

| 2 Feature                                                    | 5-2  |

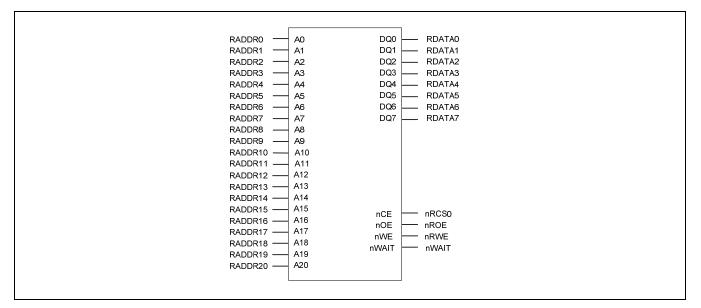

| 3 Block Diagram                                              | 5-3  |

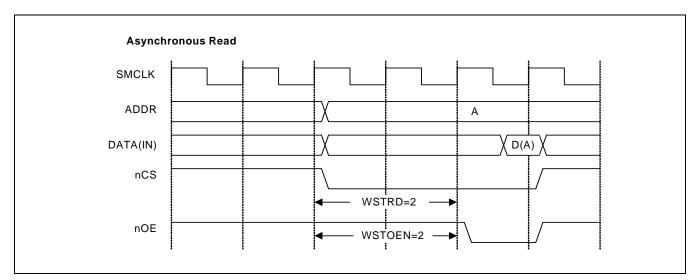

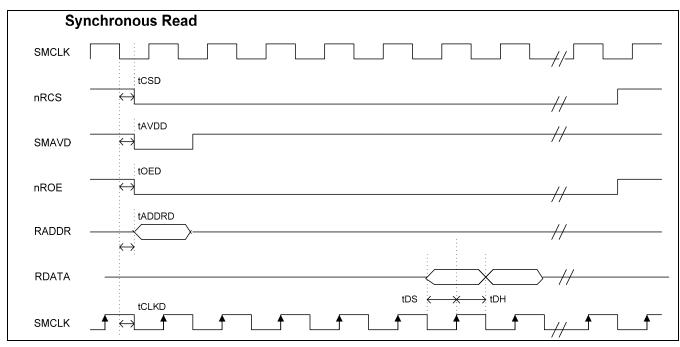

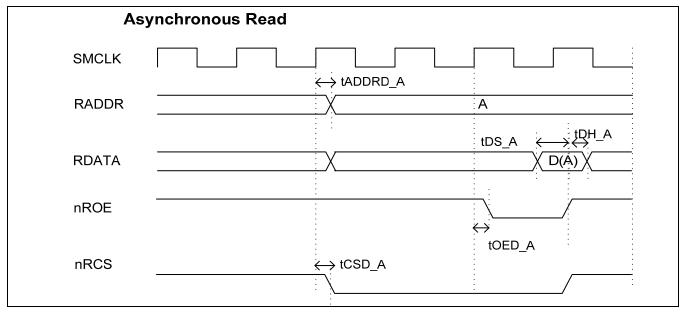

| 3.1 Asynchronous Read                                        | 5-4  |

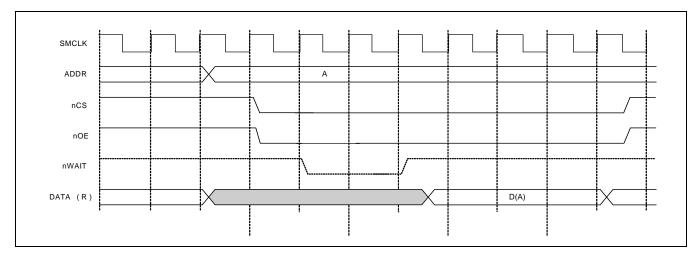

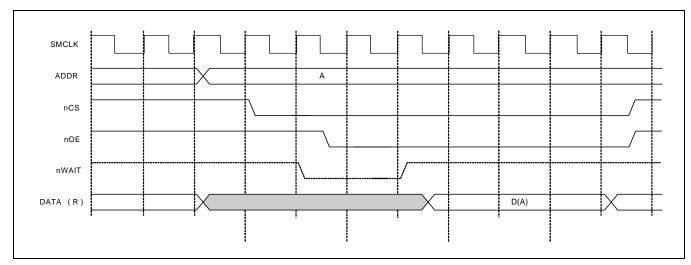

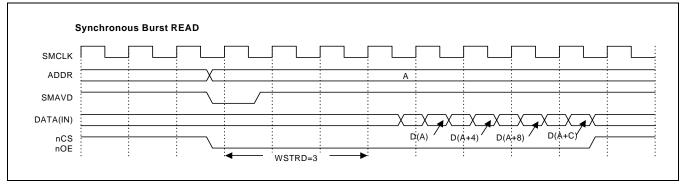

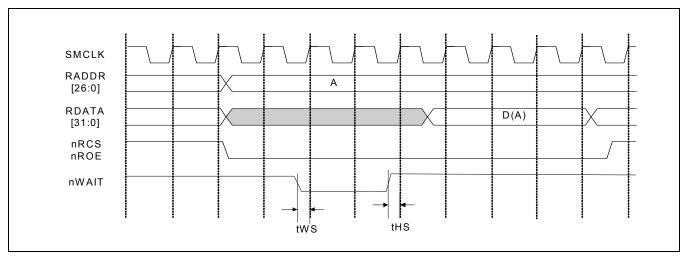

| 3.2 Synchronous Read/Synchronous Burst Read                  | 5-6  |

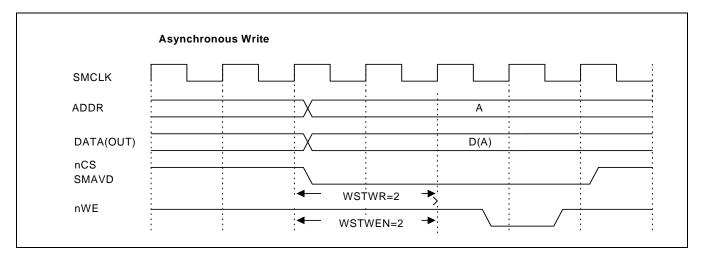

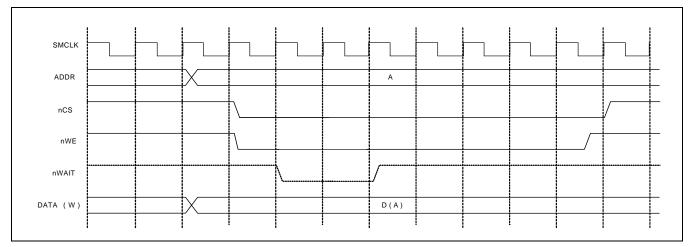

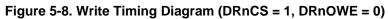

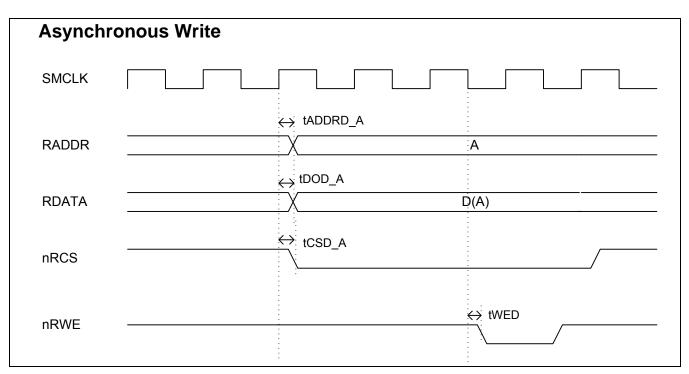

| 3.3 Asynchronous Write                                       | 5-7  |

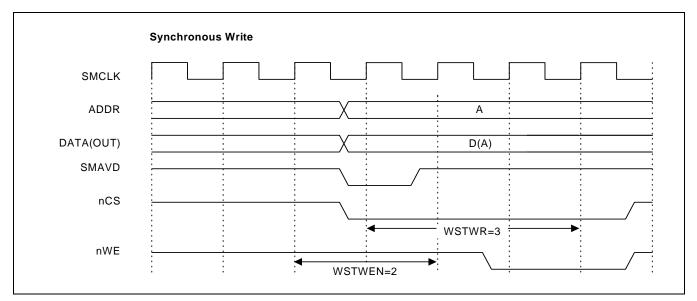

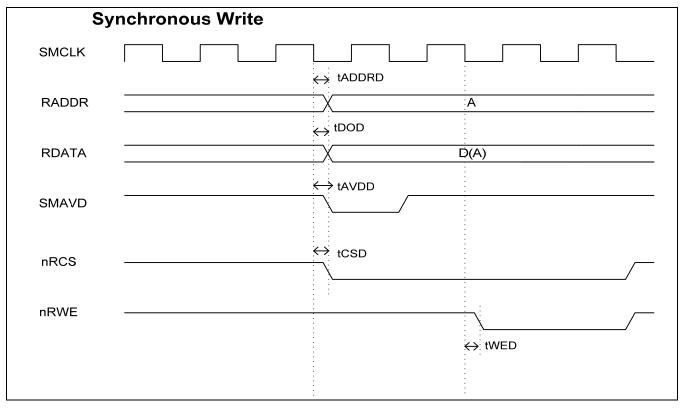

| 3.4 Synchronous Write/ Synchronous Burst Write               |      |

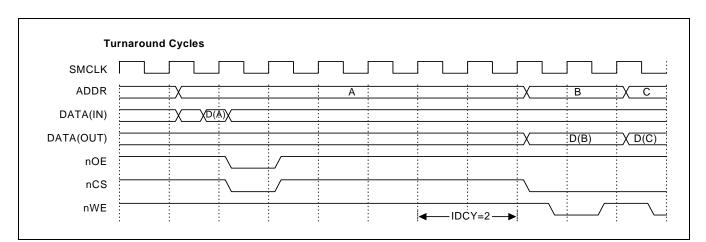

| 3.5 Bus Turnaround                                           |      |

| 4 Special Registers                                          | 5-13 |

| 4.1 Bank Idle Cycle Control Registers 0-5                    |      |

| 4.2 Bank Read Wait State Control Registers 0-5               |      |

| 4.3 Bank Write Wait State Control Registers 0-5              | 5-14 |

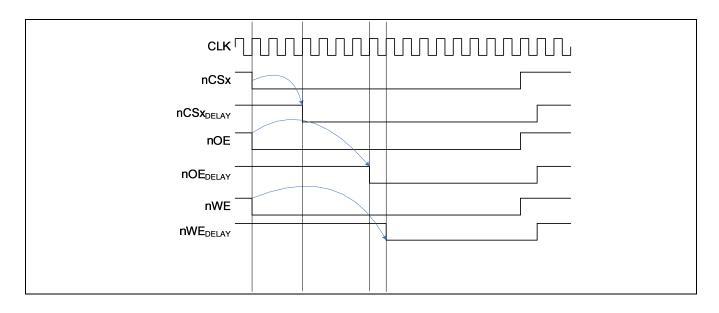

| 4.4 Bank Output Enable Assertion Delay Control Registers 0-5 | 5-14 |

| 4.5 Bank Write Enable Assertion Delay Control Registers 0-5  |      |

| 4.6 Bank Control Registers 0-5                               | 5-16 |

| 4.7 Bank Onenand Type Selection Register                     |      |

| 4.8 SMC Status Register                                      |      |

| 4.9 SMC Control Register                                     | 5-19 |

|                                                              |      |

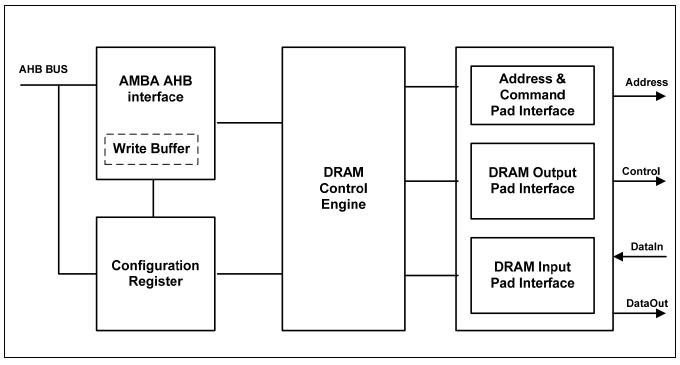

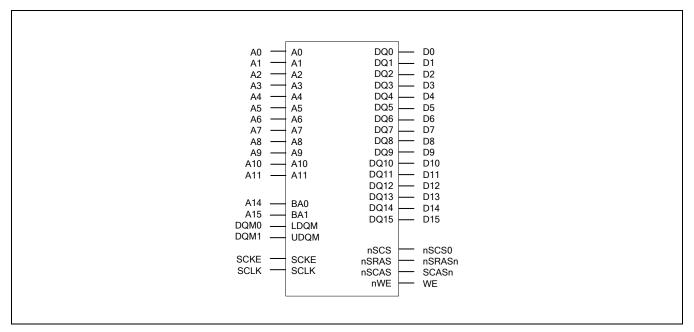

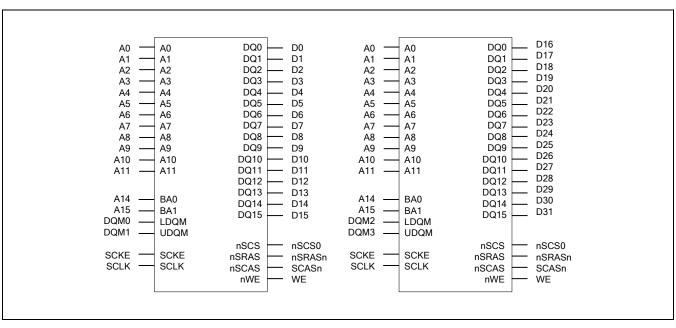

# Chapter 6 Mobile DRAM Controller

| 1 Overview                                                   | .6-1  |

|--------------------------------------------------------------|-------|

| 2 Block Diagram                                              | .6-2  |

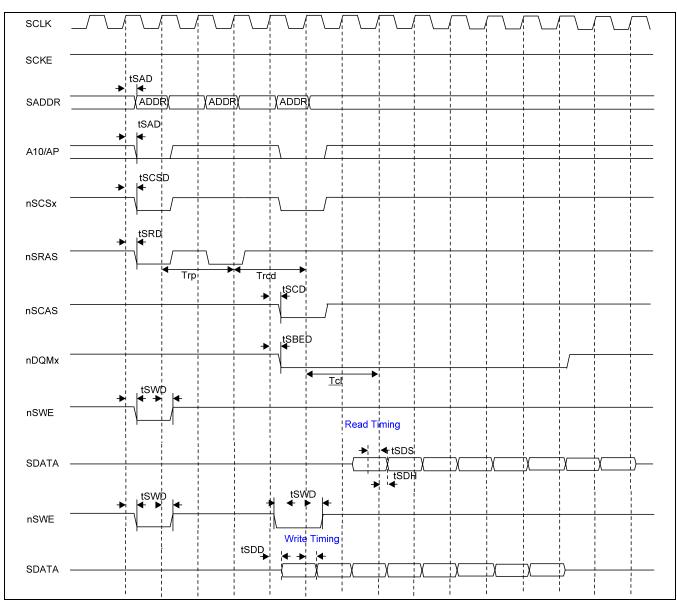

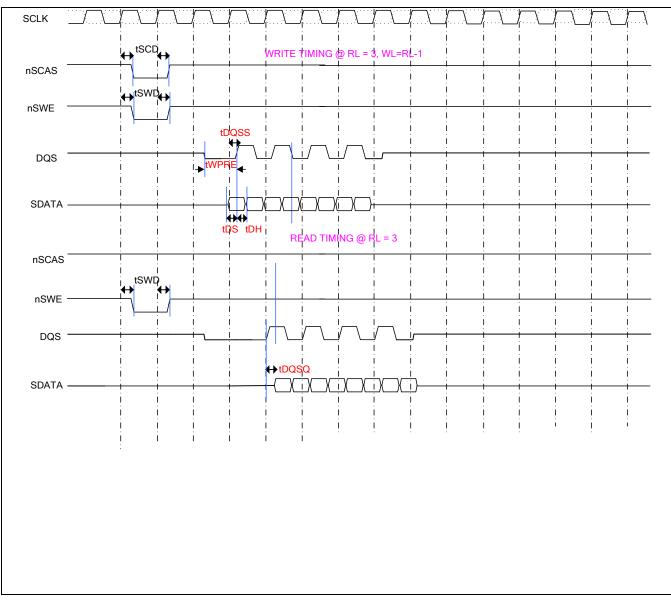

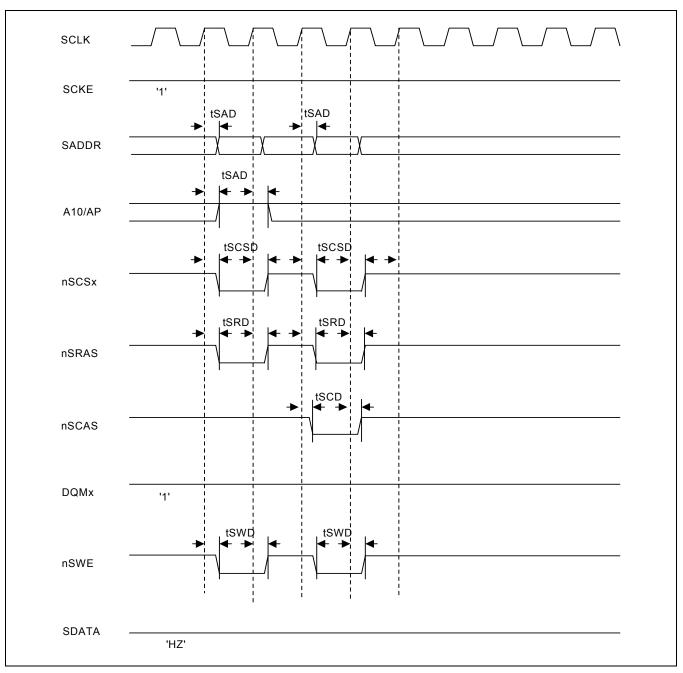

| 3 Mobile DRAM Initialization Sequence                        |       |

| 3.1 Mobile DRAM(SDRAM or mobile DDR) Initialization Sequence | . 6-3 |

| 3.2 DDR2 Initialization Sequence                             |       |

| 3.3 Mobile DRAM Configuration Register                       | . 6-8 |

| 3.4 Mobile DRAM Control Register                             | . 6-9 |

| 3.5 Mobile DRAM Timming Control Register                     | .6-10 |

| 3.6 Mobile DRAM (Extended ) Mode RegiSter Set Register       | .6-11 |

| 3.7 Mobile DRAM Refresh Control Register                     |       |

| 3.8 Mobile DRAM Write Buffer Time out Register               |       |

| •                                                            |       |

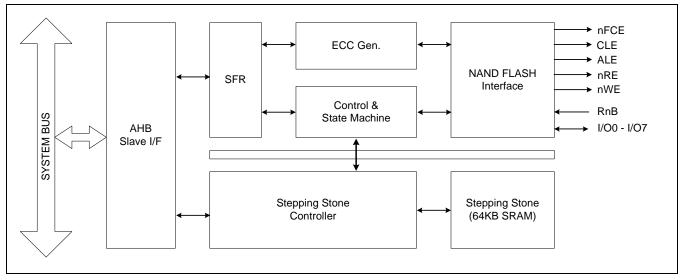

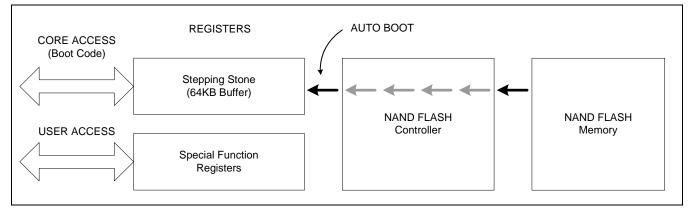

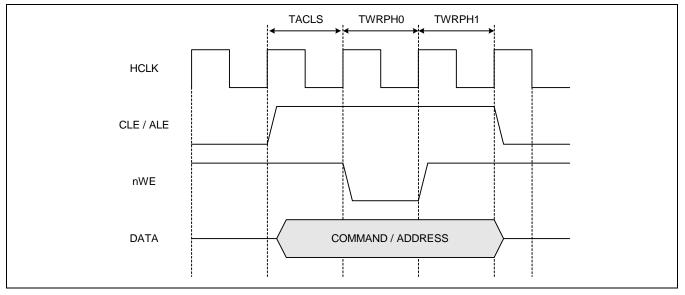

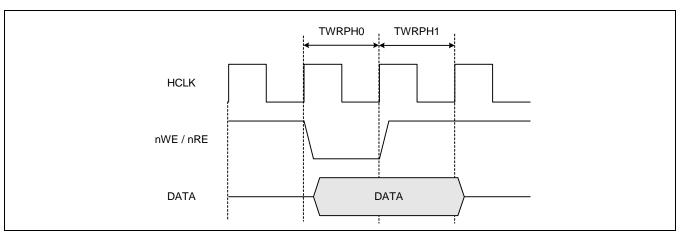

# Chapter 7 NAND Flash Controller

| 1 Overview                                           | 7-1  |

|------------------------------------------------------|------|

| 2 Features                                           | 7-1  |

| 3 Block Diagram                                      | 7-2  |

| 4 Boot Loader Function                               | 7-2  |

| 5 GPC5/6/7 Pin Configuration Table in IROM Boot Mode | 7-3  |

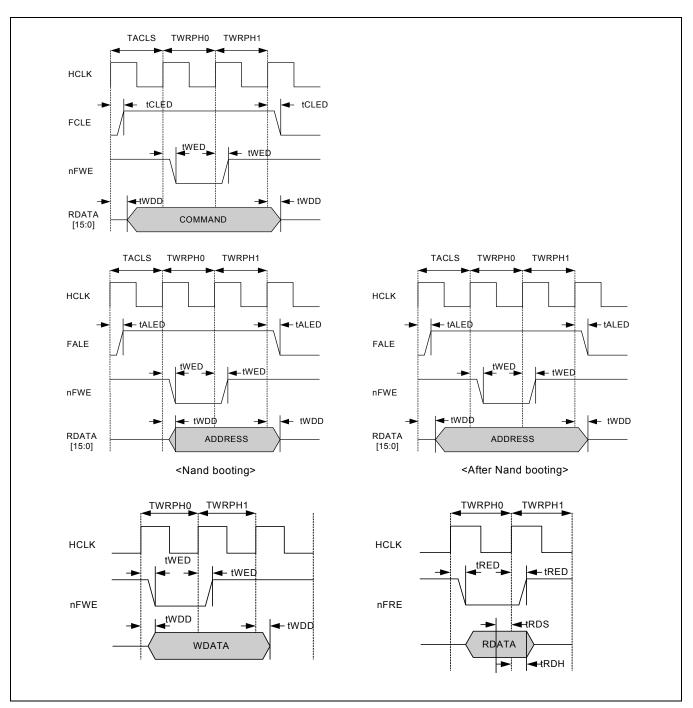

| 6 NAND Flash Memory Timing                           | 7-3  |

| 7 NAND Flash Access                                  | 7-4  |

| 8 Data Register Configuration                        | 7-5  |

| 9 Steppingstone (8KB in 64KB SRAM)                   | 7-5  |

| 10 1bit / 4bit / 8bit ECC (Error Correction Code)    | 7-5  |

| 10.1 ECC Module Features                             |      |

| 10.2 1-bit ECC Programming Encoding and Decoding     | 7-7  |

| 10.3 4-bit ECC Programming Guide (ENCODING)          |      |

| 10.4 4-bit ECC Programming Guide (DECODING)          |      |

| 10.5 8-bit ECC Programming Guide (ENCODING)          |      |

| 10.6 8-bit ECC Programming Guide (DECODING)          | 7-9  |

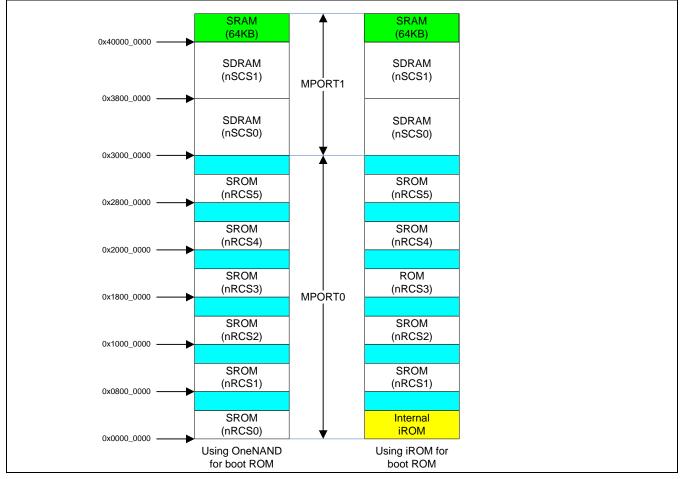

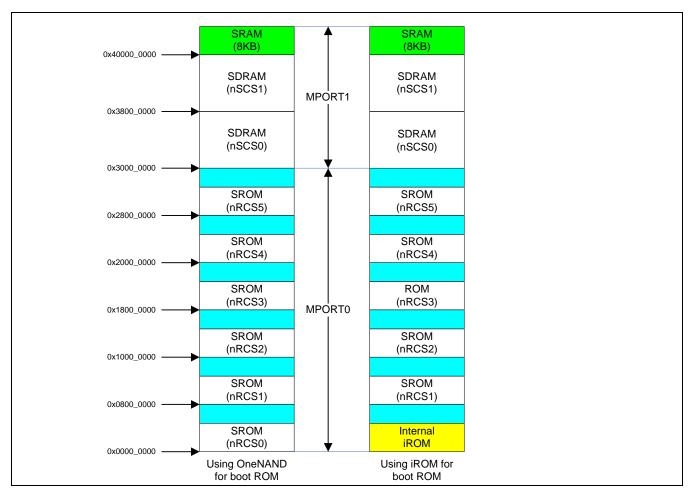

| 11 Memory Mapping(NAND boot and Other boot)          | 7-10 |

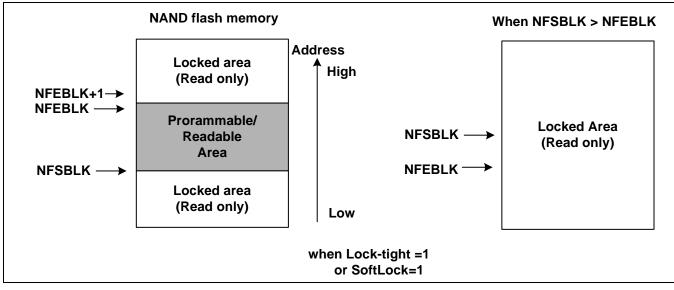

| 12 NAND Flash Memory Configuration                   | 7-11 |

| 13 NAND Flash Controller Special Registers           |      |

| 13.1 NAND Flash Controller Register Map              |      |

| 13.2 Nand Flash Configuration Register               |      |

| 13.3 Control Register                                |      |

| 13.4 Command Register                                |      |

| 13.5 Address Register                                |      |

| 13.6 Data Register                                   |      |

| 13.7 Main Data area ECC Register                     |      |

| 13.8 Spare area ECC Register                         |      |

| 13.9 Progrmmable Block Address Register              |      |

| 13.10 NFCON Status Register                          |      |

| 13.11 ECC0/1 Error Status Register                   |      |

| 13.12 Main Data Area ECC0 Status Register            |      |

| 13.13 Spare Area ECC Status Register                 |      |

| 13.14 4-bit ECC Error Patten Register                |      |

| 13.15 ECC 0/1/2 for 8bit ECC Status Register         |      |

| 13.16 8bit ECC Main Data ECC 0/1/2/3 Status Register |      |

| 13.17 8bit ECC Error Pattern Register                | 7-28 |

|                                                      |      |

# Chapter 8 DMA Controller

| 1 Overview                                            | 8-1  |

|-------------------------------------------------------|------|

| 2 DMA Request Sources                                 | 8-2  |

| 3 DMA Operation                                       | 8-3  |

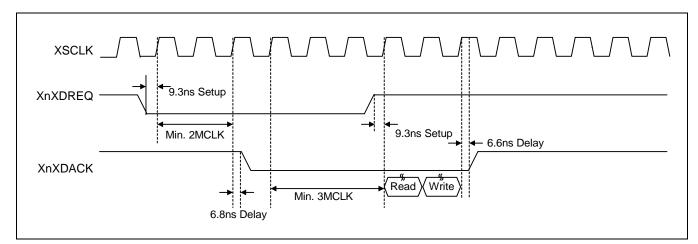

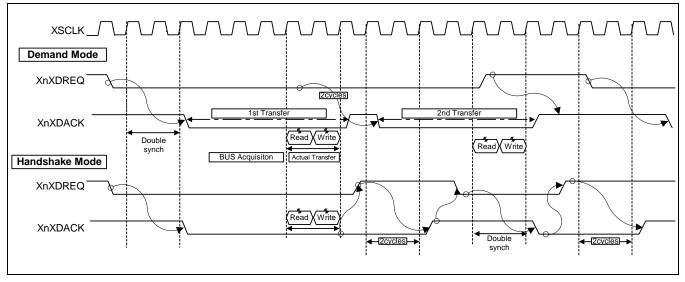

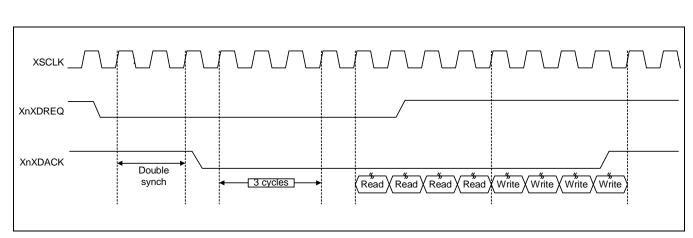

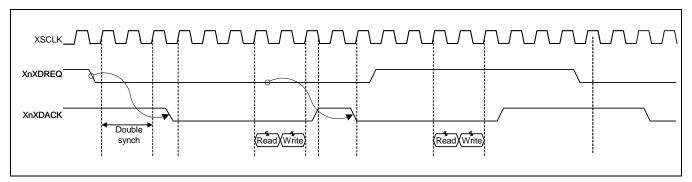

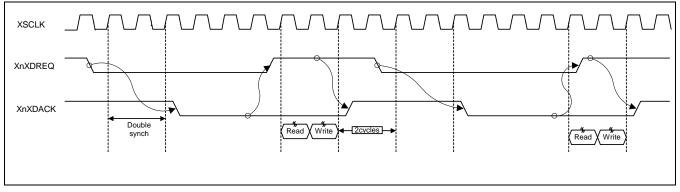

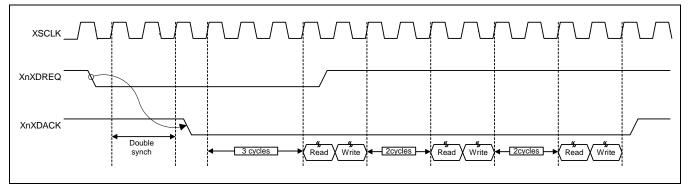

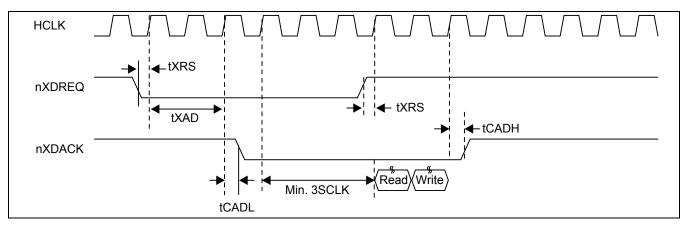

| 3.1 External DMA Dreq/Dack Protocol                   | 8-4  |

| 3.2 Examples of Possible Cases                        | 8-7  |

| 4 DMA Special Registers                               | 8-8  |

| 4.1 DMA Initial Source Register (DISRC)               |      |

| 4.2 DMA Initial Source Control Register (DISRCC)      | 8-9  |

| 4.3 DMA Initial Destination Register (DIDST)          | 8-10 |

| 4.4 DMA Initial Destination Control Register (DIDSTC) |      |

| 4.5 DMA Control Register (DCON)                       | 8-12 |

| 4.6 DMA Status Register (DSTAT)                       |      |

| 4.7 DMA Current Source Register (DCSRC)               | 8-15 |

| 4.8 Current Destination Register (DCDST)              | 8-15 |

| 4.9 DMA Mask Trigger Register (DMASKTRIG)             | 8-16 |

| 4.10 DMA Requeset Selection Register (DMAREQSEL)      | 8-17 |

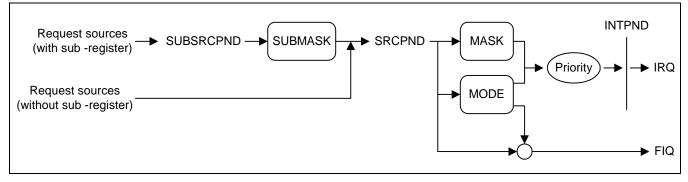

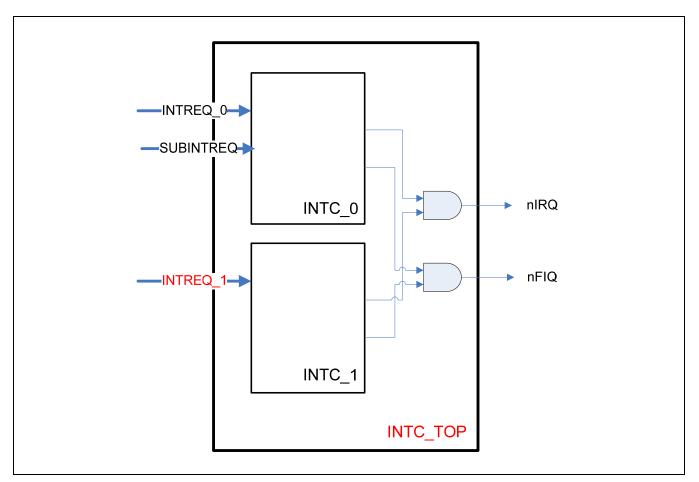

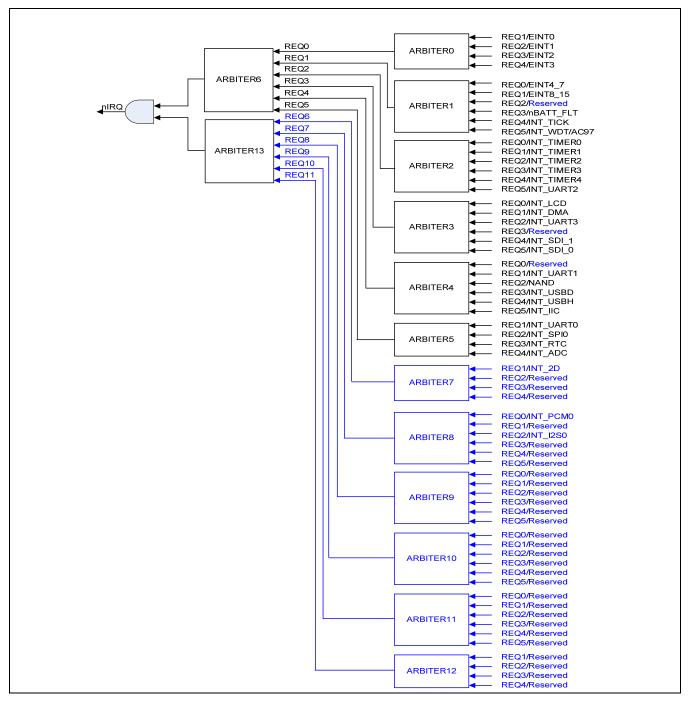

### Chapter 9 Interrupt Controller

| 1 Overview                                     | 9-1  |

|------------------------------------------------|------|

| 1.1 Interrupt Controller Operation             | 9-3  |

| 1.2 Interrupt Sources                          | 9-4  |

| 1.3 Interrupt Priority Generating Block        | 9-6  |

| 1.4 Interrupt Priority                         | 9-7  |

| 2 Interrupt Controller Special Registers       | 9-8  |

| 2.1 Source Pending (SRCPND) Register           | 9-10 |

| 2.2 Interrupt Mode (INTMOD) Register           | 9-12 |

| 2.3 Interrupt Mask (INTMSK) Register           | 9-14 |

| 2.4 Interrupt Pending (INTPND) Register        | 9-16 |

| 2.5 Interrupt Offset (INTOFFSET) Register      | 9-18 |

| 2.6 Sub Source Pending (SUBSRCPND) Register    | 9-20 |

| 2.7 Interrupt Sub Mask (INTSUBMSK) Register    | 9-22 |

| 2.8 Priority Mode Register (priority_MODE)     | 9-24 |

| 2.9 Priority Update Register (priority_UPDATE) |      |

|                                                |      |

# Chapter 10 I/O Ports

| 1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 Overview                                                     |       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------|

| 2.1Port Configuration Register (GPACON-GPMCON)10-92.2Port Data Register (GPADAT-GPMDAT)10-92.3Port Pull-Up/Down Register (GPBUDP-GPMUDP)10-92.4Miscellaneous Control Register10-92.5External Interrupt Control Register10-93I/O Port Control Register10-93I/O Port Control Register10-103.1PORT A Control Registers (GPACON, GPADAT)10-103.2PORT B Control Registers (GPCCON, GPCDAT, GPEUDP, GPBSEL)10-123.3PORT C Control Registers (GPCCON, GPCDAT, GPCUDP)10-143.4PORT D Control Registers (GPCCON, GPCDAT, GPCUDP)10-163.5PORT E Control Registers (GPCCON, GPEDAT, GPEUDP, GPESEL)10-183.6PORT F Control Registers (GPCCON, GPCDAT, GPFUDP)10-213.8PORT F Control Registers (GPCON, GPHDAT, GPFUDP)10-233.9PORT J Control Registers (GPCON, GPHDAT, GPHUDP)10-233.9PORT J Control Registers (GPCON, GPHDAT, GPHUDP)10-233.9PORT K Control Registers (GPKCON, GPKDAT, GPKUDP)10-273.11PORT L Control Registers (GPKCON, GPKDAT, GPKUDP)10-313.12PORT M Control Registers (GPKCON, GPKDAT, GPLUDP, GPLSEL)10-323.14DCLK Control Registers (GPKCON, GPMDAT, GPLUDP, GPLSEL)10-323.14DCLK Control Registers (DCLKCON)10-343.15EXTINTn (External Interrupt Control Register n)10-343.16EINTFLTn (External Interrupt Filter Register n)10-443.17 </td <td>2 Port Control Descriptions</td> <td></td>                                                                                                                                          | 2 Port Control Descriptions                                    |       |

| 2.2       Port Data Register (GPADAT-GPMDAT)       10-9         2.3       Port Pull-Up/Down Register (GPBUDP-GPMUDP)       10-9         2.4       Miscellaneous Control Register       10-9         2.4       Miscellaneous Control Register       10-9         2.5       External Interrupt Control Register       10-9         3       I/O Port Control Register       10-10         3.1       PORT A Control Registers (GPACON, GPADAT)       10-10         3.2       PORT B Control Registers (GPBCON, GPBDAT, GPBUDP, GPBSEL)       10-12         3.3       PORT C Control Registers (GPECON, GPCDAT, GPCUDP)       10-14         3.4       PORT D Control Registers (GPECON, GPEDAT, GPEUDP, GPESEL)       10-16         3.5       PORT E Control Registers (GPECON, GPEDAT, GPEUDP, GPESEL)       10-18         3.6       PORT F Control Registers (GPECON, GPEDAT, GPEUDP)       10-21         3.8       PORT H Control Registers (GPECON, GPHDAT, GPHUDP)       10-23         3.9       PORT J Control Registers (GPLCON, GPLDAT, GPLUDP)       10-23         3.9       PORT K Control Registers (GPLCON, GPLDAT, GPLUDP)       10-21         3.8       PORT J Control Registers (GPLCON, GPLDAT, GPLUDP)       10-225         3.10       PORT K Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)       10-227                                                                                                                     | 2.1 Port Configuration Register (GPACON-GPMCON)                |       |

| 2.3 Port Pull-Up/Down Register (GPBUDP-GPMUDP)10-92.4 Miscellaneous Control Register10-92.5 External Interrupt Control Register10-93 I/O Port Control Register10-103.1 PORT A Control Registers (GPACON, GPADAT)10-103.2 PORT B Control Registers (GPBCON, GPBDAT, GPBUDP, GPBSEL)10-123.3 PORT C Control Registers (GPCCON, GPCDAT, GPCUDP)10-143.4 PORT D Control Registers (GPCCON, GPCDAT, GPCUDP)10-143.5 PORT E Control Registers (GPCCON, GPEDAT, GPEUDP, GPESEL)10-183.6 PORT F Control Registers (GPCCON, GPEDAT, GPEUDP, GPESEL)10-203.7 PORT G Control Registers (GPGCON, GPDAT, GPGUDP)10-213.8 PORT H Control Registers (GPGCON, GPDAT, GPJUDP, GPJSEL)10-233.9 PORT J Control Registers (GPHCON, GPHDAT, GPJUDP, GPJSEL)10-233.9 PORT J Control Registers (GPHCON, GPLDAT, GPLUDP)10-233.10 PORT K Control Registers (GPHCON, GPLDAT, GPLUDP, GPLSEL)10-273.11 PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-293.12 PORT M Control Registers (GPMCON, GPMDAT, GPUDP, GPLSEL)10-323.14 DCLK Control Registers (GPMCON, GPMDAT, GPMUDP)10-313.13 Miscellaneous Control Register (MISCCR)10-353.14 DCLK Control Registers (DCLKCON)10-343.15 EXTINTn (External Interrupt Filter Register n)10-403.17 EINTMASK (External Interrupt Pending Register)10-423.19 OSCn (Drive Strength Control)10-443.20 DSCn (Drive Strength Control)10-443.21 PDDMCON (Power Down SRAM Control Register)10-49                           |                                                                |       |

| 2.4 Miscellaneous Control Register10-92.5 External Interrupt Control Register10-93 I/O Port Control Register10-103.1 PORT A Control Registers (GPACON, GPADAT)10-103.2 PORT B Control Registers (GPBCON, GPBDAT, GPBUDP, GPBSEL)10-123.3 PORT C Control Registers (GPCCON, GPCDAT, GPCUDP)10-143.4 PORT D Control Registers (GPCCON, GPDAT, GPDUDP)10-163.5 PORT E Control Registers (GPCCON, GPEDAT, GPEUDP, GPESEL)10-183.6 PORT F Control Registers (GPECON, GPGDAT, GPGUDP)10-203.7 PORT G Control Registers (GPGCON, GPGDAT, GPGUDP)10-213.8 PORT H Control Registers (GPLCON, GPHDAT, GPHUDP)10-233.9 PORT J Control Registers (GPLCON, GPHDAT, GPJUDP, GPJSEL)10-253.10 PORT K Control Registers (GPLCON, GPLDAT, GPLUDP, GPJSEL)10-253.10 PORT K Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-273.11 PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-233.12 PORT M Control Registers (GPLCON, GPMDAT, GPLUDP, GPLSEL)10-313.13 Miscellaneous Control Register (MISCR)10-343.15 EXTINTn (External Interrupt Control Register n)10-343.16 EINTFLTn (External Interrupt Mask Register)10-413.18 EINTPEND (External Interrupt Mask Register)10-423.19 OSCh (Drive Strength Control)10-443.20 DSCn (Drive Strength Control)10-443.21 PDDMCON (Power Down SRAM Control Register)10-443.22 PDSMCON (Power Down SRAM Control Register)10-49                                                                               |                                                                |       |

| 2.5 External Interrupt Control Register10-93 I/O Port Control Register.10-103.1 PORT A Control Registers (GPACON, GPADAT).10-103.2 PORT B Control Registers (GPBCON, GPBDAT, GPBUDP, GPBSEL).10-123.3 PORT C Control Registers (GPCCON, GPCDAT, GPCUDP)10-143.4 PORT D Control Registers (GPCCON, GPDAT, GPUDP)10-163.5 PORT E Control Registers (GPECON, GPEDAT, GPEUDP, GPESEL).10-183.6 PORT F Control Registers (GPCCON, GPEDAT, GPEUDP)10-203.7 PORT G Control Registers (GPCCON, GPEDAT, GPHUDP)10-213.8 PORT H Control Registers (GPHCON, GPHDAT, GPHUDP)10-233.9 PORT J Control Registers (GPLCON, GPHDAT, GPHUDP)10-233.9 PORT J Control Registers (GPLCON, GPLDAT, GPLUDP, GPJSEL)10-253.10 PORT K Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-263.11 PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-273.11 PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-233.12 PORT M Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-313.13 Miscellaneous Control Register (MISCCR)10-343.14 DCLK Control Registers (DCLKCON)10-343.15 EXTINTn (External Interrupt Control Register n)10-403.17 EINTMASK (External Interrupt Register n)10-413.18 EINTFLDN (External Interrupt Register)10-423.19 OSCn (Drive Strength Control)10-443.20 DSCn (Drive Strength Control)10-443.21 PDDMCON (Power Down SRAM Control Register)10-443.22 PDSMCON (Power Down SRAM Control Register)10-49 <td></td> <td></td> |                                                                |       |

| 3 I/O Port Control Register       10-10         3.1 PORT A Control Registers (GPACON, GPADAT).       10-10         3.2 PORT B Control Registers (GPBCON, GPBDAT, GPBUDP, GPBSEL).       10-12         3.3 PORT C Control Registers (GPCCON, GPCDAT, GPCUDP)       10-14         3.4 PORT D Control Registers (GPCCON, GPDAT, GPDUDP)       10-16         3.5 PORT E Control Registers (GPECON, GPEDAT, GPEUDP, GPESEL).       10-18         3.6 PORT F Control Registers (GPECON, GPEDAT, GPFUDP)       10-20         3.7 PORT G Control Registers (GPGCON, GPGDAT, GPGUDP).       10-21         3.8 PORT H Control Registers (GPGCON, GPGDAT, GPGUDP)       10-21         3.8 PORT J Control Registers (GPGCON, GPDAT, GPGUDP)       10-22         3.9 PORT J Control Registers (GPLCON, GPLDAT, GPHUDP)       10-23         3.9 PORT J Control Registers (GPLCON, GPLDAT, GPJUDP, GPLSEL)       10-25         3.10 PORT K Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)       10-27         3.11 PORT L Control Registers (GPLCON, GPMDAT, GPMUDP)       10-31         3.13 Miscellaneous Control Register (MISCCR)       10-32         3.14 DCLK Control Registers (DCLKCON)       10-34         3.15 EXTINTn (External Interrupt Filter Register n)       10-34         3.16 EINTFLTn (External Interrupt Mask Register)       10-44         3.19 GSTATUSn (General Status Registers)       10-44 <t< td=""><td></td><td></td></t<>  |                                                                |       |

| 3.1 PORT A Control Registers (GPACON, GPADAT).10-103.2 PORT B Control Registers (GPBCON, GPBDAT, GPBUDP, GPBSEL).10-123.3 PORT C Control Registers (GPCCON, GPCDAT, GPCUDP)10-143.4 PORT D Control Registers (GPDCON, GPDDAT, GPDUDP)10-163.5 PORT E Control Registers (GPECON, GPEDAT, GPEUDP, GPESEL).10-183.6 PORT F Control Registers (GPECON, GPEDAT, GPGUDP)10-203.7 PORT G Control Registers (GPGCON, GPGDAT, GPGUDP)10-213.8 PORT H Control Registers (GPGCON, GPGDAT, GPGUDP)10-233.9 PORT J Control Registers (GPJCON, GPJDAT, GPJUDP)10-233.9 PORT J Control Registers (GPJCON, GPLDAT, GPJUDP, GPJSEL)10-253.10 PORT K Control Registers (GPLCON, GPLDAT, GPLUDP, GPJSEL)10-273.11 PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-233.9 PORT J Control Registers (GPLCON, GPLDAT, GPMUDP)10-313.13 Miscellaneous Control Register (MISCCR)10-323.14 DCLK Control Registers (DCLKCON)10-343.15 EXTINTn (External Interrupt Control Register n)10-353.16 EINTFLTn (External Interrupt Filter Register n)10-413.18 EINTFEND (External Interrupt Pending Register)10-413.19 OSCn (Drive Strength Control)10-443.20 DSCn (Drive Strength Control)10-443.22 PDSMCON (Power Down SDRAM Control Register)10-443.22 PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                           |                                                                |       |

| 3.2PORT B Control Registers (GPBCON, GPBDAT, GPBUDP, GPBSEL)10-123.3PORT C Control Registers (GPCCON, GPCDAT, GPCUDP)10-143.4PORT D Control Registers (GPDCON, GPDDAT, GPDUDP)10-163.5PORT E Control Registers (GPECON, GPEDAT, GPEUDP, GPESEL)10-183.6PORT F Control Registers (GPFCON, GPFDAT, GPFUDP)10-203.7PORT G Control Registers (GPGCON, GPGDAT, GPGUDP)10-213.8PORT H Control Registers (GPHCON, GPHDAT, GPHUDP)10-233.9PORT J Control Registers (GPLCON, GPHDAT, GPHUDP)10-253.10PORT K Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-253.11PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-293.12PORT M Control Registers (GPMCON, GPMDAT, GPMUDP)10-313.13Miscellaneous Control Registers (GPMCON, GPMDAT, GPMUDP)10-323.14DCLK Control Registers (DCLKCON)10-343.15EXTINTn (External Interrupt Control Register n)10-343.16EINTFLTn (External Interrupt Kask Register)10-413.18INTPEND (External Interrupt Pending Register)10-413.19GSTATUSn (General Status Registers)10-443.20DSCn (Drive Strength Control)10-443.21PDDMCON (Power Down SDRAM Control Register)10-483.22PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                   |                                                                |       |

| 3.3PORT C Control Registers (GPCCON, GPCDAT, GPCUDP)10-143.4PORT D Control Registers (GPDCON, GPDDAT, GPDUDP)10-163.5PORT E Control Registers (GPECON, GPEDAT, GPEUDP, GPESEL)10-183.6PORT F Control Registers (GPFCON, GPFDAT, GPFUDP)10-203.7PORT G Control Registers (GPGCON, GPGDAT, GPGUDP)10-213.8PORT H Control Registers (GPHCON, GPHDAT, GPHUDP)10-233.9PORT J Control Registers (GPLCON, GPJDAT, GPJUDP, GPJSEL)10-233.10PORT K Control Registers (GPLCON, GPLDAT, GPLUDP, GPJSEL)10-273.11PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-293.12PORT M Control Registers (GPMCON, GPLDAT, GPLUDP, GPLSEL)10-293.14DCLK Control Registers (DCLKCON)10-343.15EXTINTn (External Interrupt Control Register n)10-343.16EINTFLTn (External Interrupt Filter Register n)10-413.18BINTPEND (External Interrupt Mask Register)10-423.19OSCA (Drive Strength Control)10-443.20DSCn (Drive Strength Control)10-443.22PDSMCON (Power Down SDRAM Control Register)10-44                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                |       |

| 3.5PORT E Control Registers (GPECON, GPEDAT, GPEUDP, GPESEL)10-183.6PORT F Control Registers (GPFCON, GPFDAT, GPFUDP)10-203.7PORT G Control Registers (GPGCON, GPGDAT, GPGUDP)10-213.8PORT H Control Registers (GPHCON, GPHDAT, GPHUDP)10-233.9PORT J Control Registers (GPJCON, GPJDAT, GPJUDP, GPJSEL)10-253.10PORT K Control Registers (GPKCON, GPKDAT, GPKUDP)10-273.11PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-293.12PORT M Control Registers (GPMCON, GPMDAT, GPMUDP)10-313.13Miscellaneous Control Register (MISCCR)10-323.14DCLK Control Registers (DCLKCON)10-343.15EXTINTn (External Interrupt Control Register n)10-353.16EINTFLTn (External Interrupt Filter Register n)10-413.18EINTPEND (External Interrupt Pending Register)10-443.20DSCn (Drive Strength Control)10-443.21PDMCON (Power Down SDRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                |       |

| 3.5PORT E Control Registers (GPECON, GPEDAT, GPEUDP, GPESEL)10-183.6PORT F Control Registers (GPFCON, GPFDAT, GPFUDP)10-203.7PORT G Control Registers (GPGCON, GPGDAT, GPGUDP)10-213.8PORT H Control Registers (GPHCON, GPHDAT, GPHUDP)10-233.9PORT J Control Registers (GPJCON, GPJDAT, GPJUDP, GPJSEL)10-253.10PORT K Control Registers (GPKCON, GPKDAT, GPKUDP)10-273.11PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-293.12PORT M Control Registers (GPMCON, GPMDAT, GPMUDP)10-313.13Miscellaneous Control Register (MISCCR)10-323.14DCLK Control Registers (DCLKCON)10-343.15EXTINTn (External Interrupt Control Register n)10-353.16EINTFLTn (External Interrupt Filter Register n)10-413.18EINTPEND (External Interrupt Pending Register)10-443.20DSCn (Drive Strength Control)10-443.21PDMCON (Power Down SDRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.4 PORT D Control Registers (GPDCON, GPDDAT, GPDUDP)          | 10-16 |

| 3.6PORT F Control Registers (GPFCON, GPFDAT, GPFUDP)10-203.7PORT G Control Registers (GPGCON, GPGDAT, GPGUDP)10-213.8PORT H Control Registers (GPHCON, GPHDAT, GPHUDP)10-233.9PORT J Control Registers (GPJCON, GPJDAT, GPJUDP, GPJSEL)10-253.10PORT K Control Registers (GPKCON, GPKDAT, GPKUDP)10-273.11PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-293.12PORT M Control Registers (GPMCON, GPMDAT, GPMUDP)10-313.13Miscellaneous Control Register (MISCCR)10-323.14DCLK Control Registers (DCLKCON)10-343.15EXTINTn (External Interrupt Control Register n)10-353.16EINTFLTn (External Interrupt Filter Register n)10-413.17BINTPEND (External Interrupt Pending Register)10-413.18SINTPEND (External Interrupt Pending Register)10-423.20DSCn (Drive Strength Control)10-443.21PDDMCON (Power Down SDRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                |       |

| 3.8 PORT H Control Registers (GPHCON, GPHDAT, GPHUDP)10-233.9 PORT J Control Registers (GPJCON, GPJDAT, GPJUDP, GPJSEL)10-253.10 PORT K Control Registers (GPKCON, GPKDAT, GPKUDP)10-273.11 PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-293.12 PORT M Control Registers (GPMCON, GPMDAT, GPMUDP)10-313.13 Miscellaneous Control Register (MISCCR)10-323.14 DCLK Control Registers (DCLKCON)10-343.15 EXTINTn (External Interrupt Control Register n)10-353.16 EINTFLTn (External Interrupt Filter Register n)10-413.18 EINTPEND (External Interrupt Mask Register)10-413.19 GSTATUSn (General Status Registers)10-433.20 DSCn (Drive Strength Control)10-443.21 PDDMCON (Power Down SDRAM Control Register)10-483.22 PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.6 PORT F Control Registers (GPFCON, GPFDAT, GPFUDP)          | 10-20 |

| 3.8 PORT H Control Registers (GPHCON, GPHDAT, GPHUDP)10-233.9 PORT J Control Registers (GPJCON, GPJDAT, GPJUDP, GPJSEL)10-253.10 PORT K Control Registers (GPKCON, GPKDAT, GPKUDP)10-273.11 PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-293.12 PORT M Control Registers (GPMCON, GPMDAT, GPMUDP)10-313.13 Miscellaneous Control Register (MISCCR)10-323.14 DCLK Control Registers (DCLKCON)10-343.15 EXTINTn (External Interrupt Control Register n)10-353.16 EINTFLTn (External Interrupt Filter Register n)10-413.18 EINTPEND (External Interrupt Mask Register)10-413.19 GSTATUSn (General Status Registers)10-433.20 DSCn (Drive Strength Control)10-443.21 PDDMCON (Power Down SDRAM Control Register)10-483.22 PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.7 PORT G Control Registers (GPGCON, GPGDAT, GPGUDP)          | 10-21 |

| 3.10PORT K Control Registers (GPKCON, GPKDAT, GPKUDP)10-273.11PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)10-293.12PORT M Control Registers (GPMCON, GPMDAT, GPMUDP)10-313.13Miscellaneous Control Register (MISCCR)10-323.14DCLK Control Registers (DCLKCON)10-343.15EXTINTn (External Interrupt Control Register n)10-353.16EINTFLTn (External Interrupt Filter Register n)10-403.17EINTMASK (External Interrupt Mask Register)10-413.18EINTPEND (External Interrupt Pending Register)10-423.19GSTATUSn (General Status Registers)10-433.20DSCn (Drive Strength Control)10-443.21PDDMCON (Power Down SDRAM Control Register)10-483.22PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.8 PORT H Control Registers (GPHCON, GPHDAT, GPHUDP)          | 10-23 |

| 3.11PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                |       |

| 3.12PORT M Control Registers (GPMCON, GPMDAT, GPMUDP)10-313.13Miscellaneous Control Register (MISCCR)10-323.14DCLK Control Registers (DCLKCON)10-343.15EXTINTn (External Interrupt Control Register n)10-353.16EINTFLTn (External Interrupt Filter Register n)10-403.17EINTMASK (External Interrupt Mask Register)10-413.18EINTPEND (External Interrupt Pending Register)10-413.19GSTATUSn (General Status Registers)10-433.20DSCn (Drive Strength Control)10-443.21PDDMCON (Power Down SDRAM Control Register)10-483.22PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.10 PORT K Control Registers (GPKCON, GPKDAT, GPKUDP)         | 10-27 |

| 3.13 Miscellaneous Control Register (MISCCR)10-323.14 DCLK Control Registers (DCLKCON)10-343.15 EXTINTn (External Interrupt Control Register n)10-353.16 EINTFLTn (External Interrupt Filter Register n)10-403.17 EINTMASK (External Interrupt Mask Register)10-413.18 EINTPEND (External Interrupt Pending Register)10-423.19 GSTATUSn (General Status Registers)10-433.20 DSCn (Drive Strength Control)10-443.21 PDDMCON (Power Down SDRAM Control Register)10-483.22 PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.11 PORT L Control Registers (GPLCON, GPLDAT, GPLUDP, GPLSEL) | 10-29 |

| 3.13 Miscellaneous Control Register (MISCCR)10-323.14 DCLK Control Registers (DCLKCON)10-343.15 EXTINTn (External Interrupt Control Register n)10-353.16 EINTFLTn (External Interrupt Filter Register n)10-403.17 EINTMASK (External Interrupt Mask Register)10-413.18 EINTPEND (External Interrupt Pending Register)10-423.19 GSTATUSn (General Status Registers)10-433.20 DSCn (Drive Strength Control)10-443.21 PDDMCON (Power Down SDRAM Control Register)10-483.22 PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.12 PORT M Control Registers (GPMCON, GPMDAT, GPMUDP)         | 10-31 |

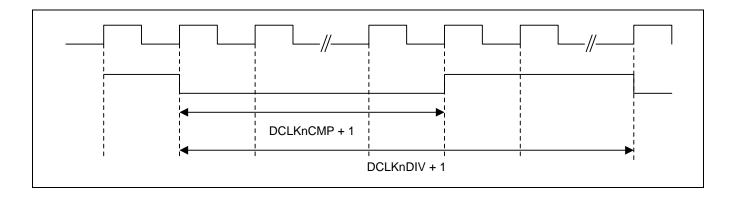

| 3.15 EXTINTn (External Interrupt Control Register n)10-353.16 EINTFLTn (External Interrupt Filter Register n)10-403.17 EINTMASK (External Interrupt Mask Register)10-413.18 EINTPEND (External Interrupt Pending Register)10-423.19 GSTATUSn (General Status Registers)10-433.20 DSCn (Drive Strength Control)10-443.21 PDDMCON (Power Down SDRAM Control Register)10-483.22 PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.13 Miscellaneous Control Register (MISCCR)                   | 10-32 |

| 3.16 EINTFLTn (External Interrupt Filter Register n).10-403.17 EINTMASK (External Interrupt Mask Register)10-413.18 EINTPEND (External Interrupt Pending Register)10-423.19 GSTATUSn (General Status Registers)10-433.20 DSCn (Drive Strength Control)10-443.21 PDDMCON (Power Down SDRAM Control Register)10-483.22 PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                |       |

| 3.17 EINTMASK (External Interrupt Mask Register)10-413.18 EINTPEND (External Interrupt Pending Register)10-423.19 GSTATUSn (General Status Registers)10-433.20 DSCn (Drive Strength Control)10-443.21 PDDMCON (Power Down SDRAM Control Register)10-483.22 PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.15 EXTINTn (External Interrupt Control Register n)           | 10-35 |

| 3.18 EINTPEND (External Interrupt Pending Register)10-423.19 GSTATUSn (General Status Registers)10-433.20 DSCn (Drive Strength Control)10-443.21 PDDMCON (Power Down SDRAM Control Register)10-483.22 PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.16 EINTFLTn (External Interrupt Filter Register n)           | 10-40 |

| 3.19 GSTATUSn (General Status Registers)10-433.20 DSCn (Drive Strength Control)10-443.21 PDDMCON (Power Down SDRAM Control Register)10-483.22 PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                |       |

| 3.20 DSCn (Drive Strength Control)10-443.21 PDDMCON (Power Down SDRAM Control Register)10-483.22 PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                |       |

| 3.21 PDDMCON (Power Down SDRAM Control Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                |       |

| 3.22 PDSMCON (Power Down SRAM Control Register)10-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                |       |

| 4 CPIO Alive & Sleep Part 10-51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4 GPIO Alive & Sleep Part                                      | 10-51 |

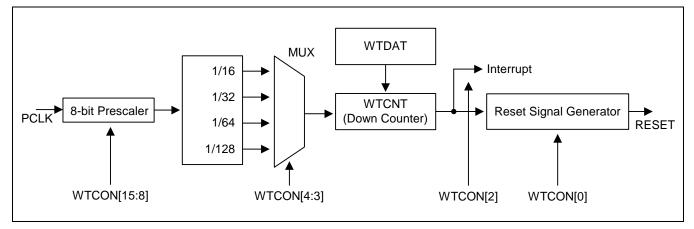

# Chapter 11 WatchDog Timer

| 1 Overview                                  | 11-1 |

|---------------------------------------------|------|

| 1.1 Features                                | 11-1 |

| 2 Watchdog Timer Operation                  |      |

| 2.1 Block Diagram                           |      |

| 2.2 WTDAT & WTCNT                           |      |

| 2.3 Consideration of Debugging Environment  |      |

| 3 Watchdog Timer Special Registers          |      |

| 3.1 Watchdog Timer Control (WTCON) Register |      |

| 3.2 Watchdog Timer Data (WTDAT) Register    |      |

| 3.3 Watchdog Timer Count (WTCNT) Register   | 11-5 |

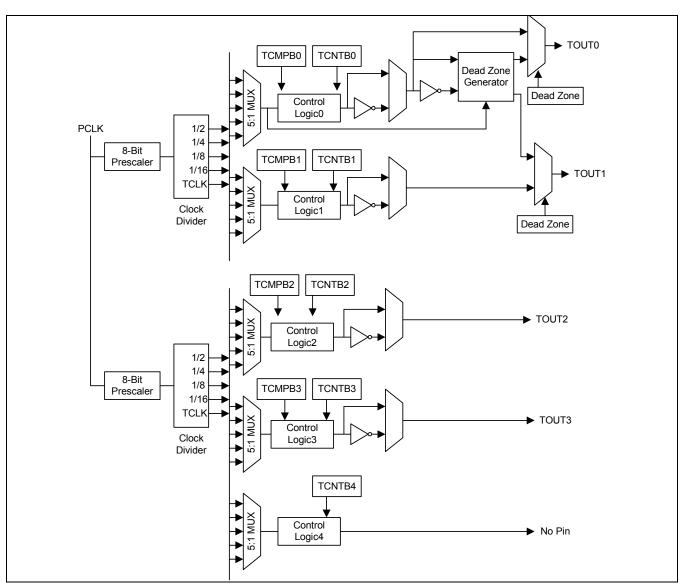

### Chapter 12 PWM Timer

| 1 Overview                                                                   |       |

|------------------------------------------------------------------------------|-------|

| 1.1 Feature                                                                  |       |

| 2 PWM Timer Operation                                                        |       |

| 2.1 Prescaler & Divider                                                      |       |

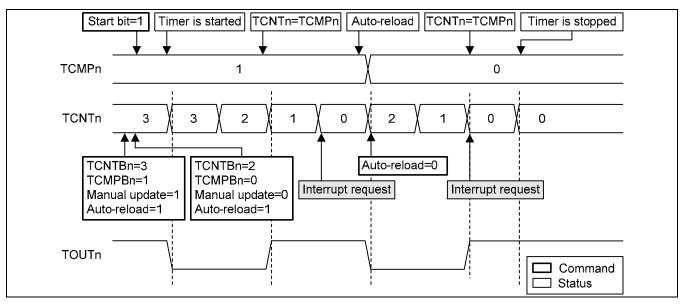

| 2.2 Basic Timer Operation                                                    |       |

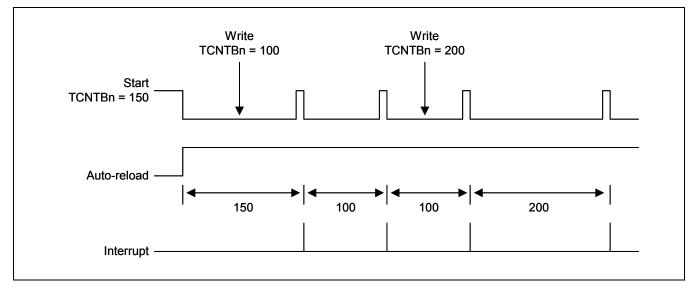

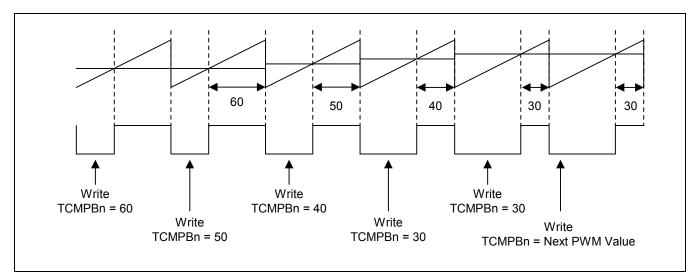

| 2.3 Auto Reload & Double Buffering                                           |       |

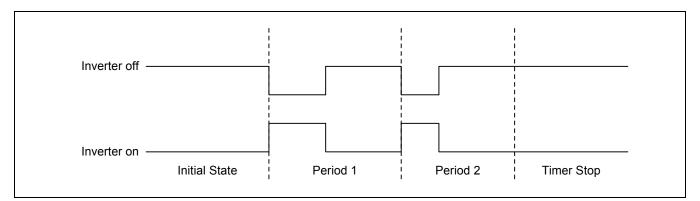

| 2.4 Timer Initialization Using Manual Update Bit and Inverter Bit            |       |

| 2.5 Timer Operation                                                          |       |

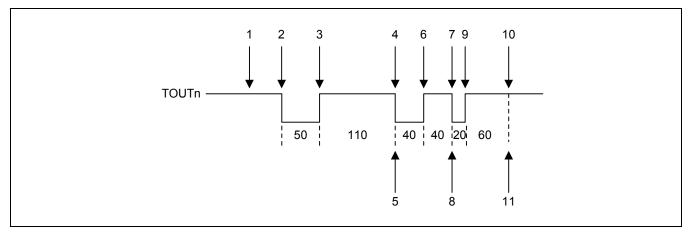

| 2.6 Pulse Width Modulation (PWM)                                             |       |

| 2.7 Output Level Control                                                     |       |

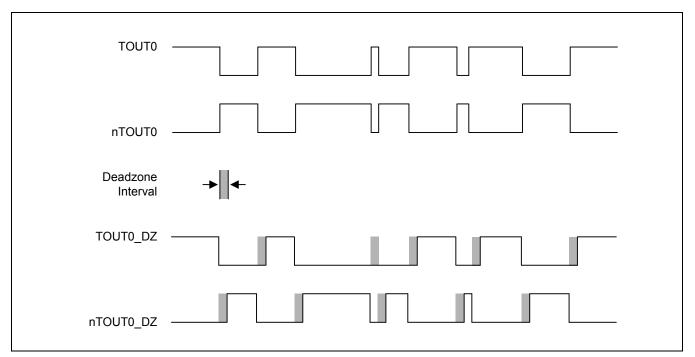

| 2.8 DEAD Zone Generator                                                      | 12-10 |

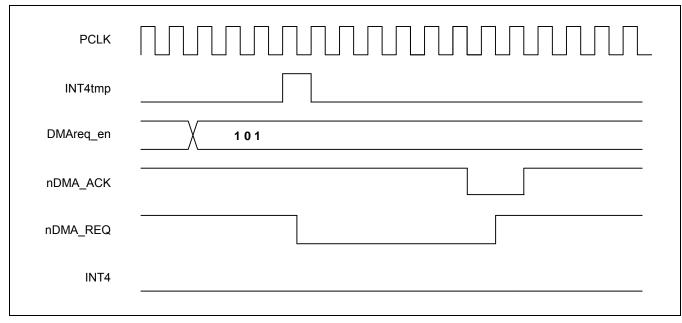

| 2.9 DMA Request Mode                                                         | 12-11 |

| 3 PWM Timer Control Registers                                                |       |

| 3.1 Timer Configuration Register0 (TCFG0)                                    | 12-12 |

| 3.2 Timer Configuration Register1 (TCFG1)                                    | 12-13 |

| 3.3 Timer Control (TCON) Register                                            | 12-14 |

| 3.4 Timer 0 Count Buffer Register & Compare Buffer Register (TCNTB0/TCMPB0)  |       |

| 3.5 Timer 0 Count Observation Register (TCNTO0)                              | 12-16 |

| 3.6 Timer 1 Count Buffer Register & Compare Buffer Register (TCNTB1/TCMPB1)  | 12-17 |

| 3.7 Timer 1 Count Observation Register (TCNTO1)                              | 12-17 |

| 3.8 Timer 2 Count Buffer Register & Compare Buffer Register (TCNTB2/TCMPB2)  | 12-18 |

| 3.9 Timer 2 Count Observation Register (TCNTO2)                              |       |

| 3.10 Timer 3 Count Buffer Register & Compare Buffer Register (TCNTB3/TCMPB3) | 12-19 |

| 3.11 Timer 3 Count Observation Register (TCNTO3)                             | 12-19 |

| 3.12 Timer 4 Count Buffer Register (TCNTB4)                                  |       |

| 3.13 Timer 4 Count Observation Register (TCNTO4)                             | 12-20 |

|                                                                              |       |

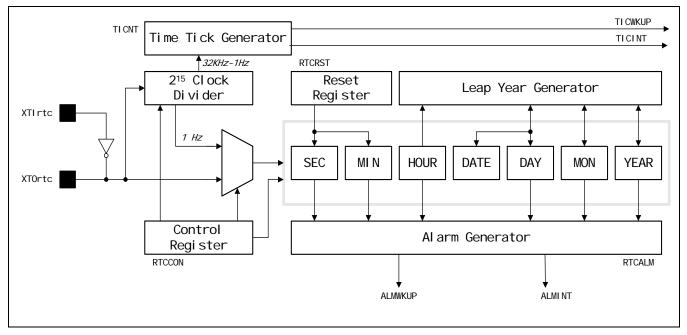

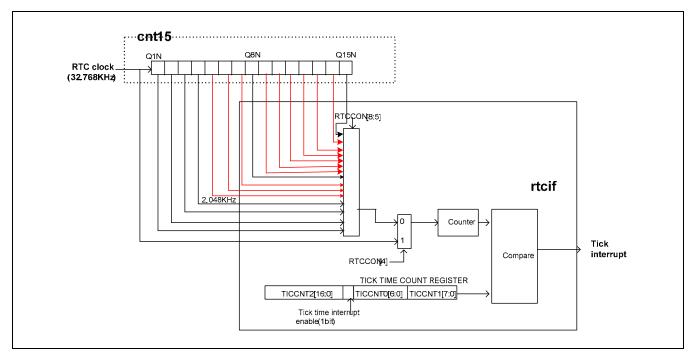

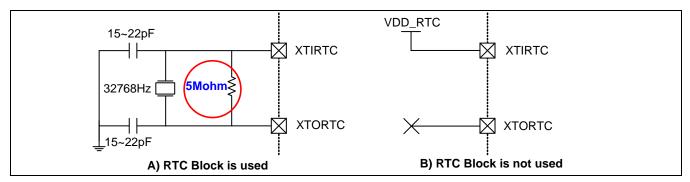

### Chapter 13 Real Time Clock (RTC)

| 1 Overview                                |  |

|-------------------------------------------|--|

| 1.1 Features                              |  |

| 1.2 Real Time Clock Operation Description |  |

| 1.3 External Interface                    |  |

| 1.4 Register Description                  |  |

| 1.5 Individual Register Descriptions      |  |

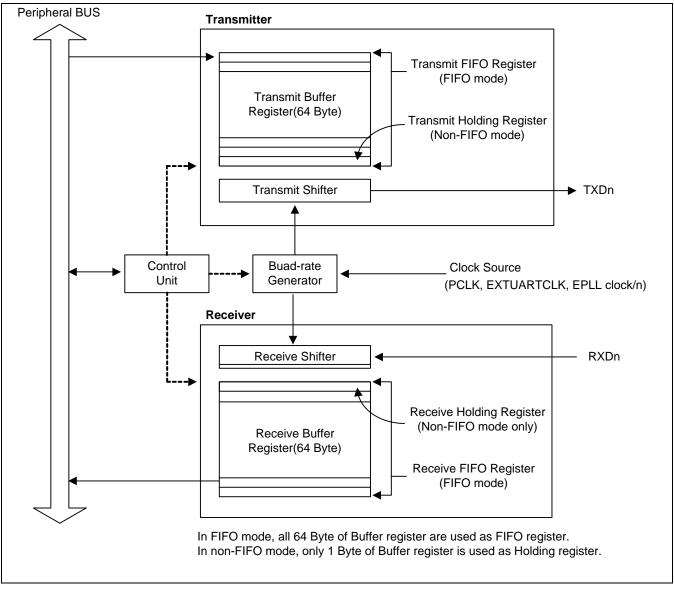

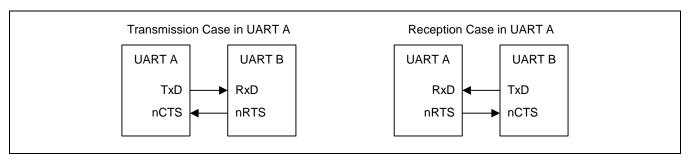

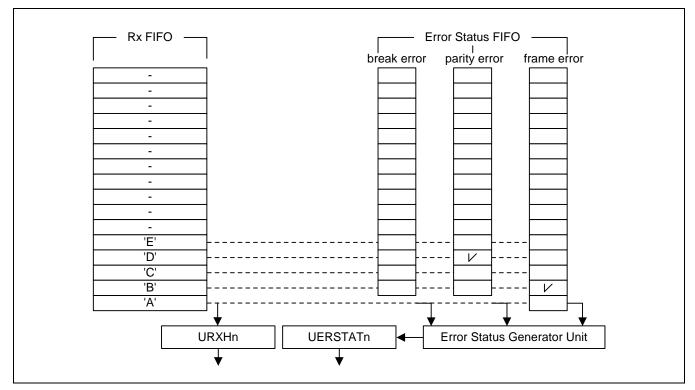

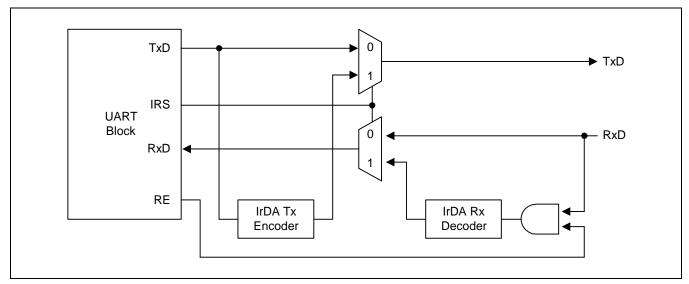

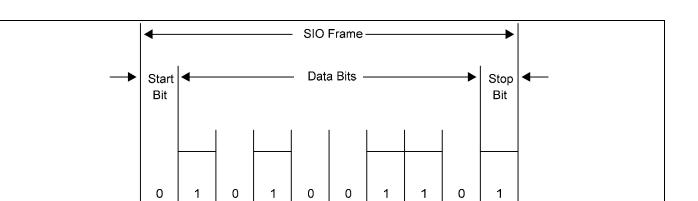

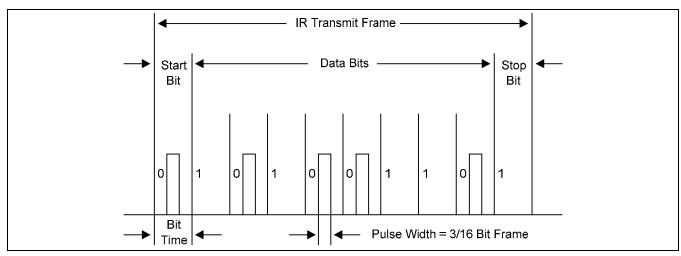

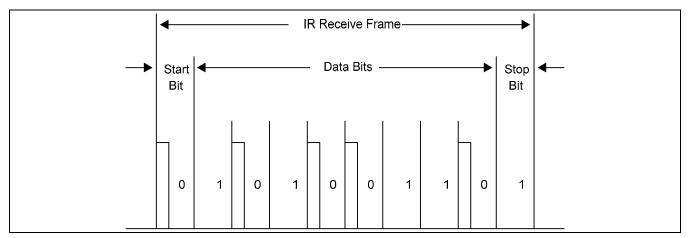

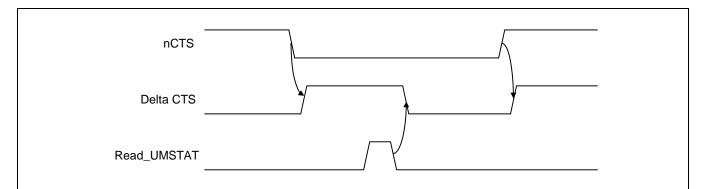

# Chapter 14 UART

| 1 Overview                                                           | 14-1  |

|----------------------------------------------------------------------|-------|

| 1.1 Features                                                         | 14-1  |

| 2 Block Diagram                                                      | 14-2  |

| 2.1 UART Operation                                                   | 14-3  |

| 3 UART Special Registers                                             | 14-12 |

| 3.1 UART Line Control Register                                       | 14-12 |

| 3.2 UART Control Register                                            | 14-13 |

| 3.3 UART FIFO Control Register                                       | 14-15 |

| 3.4 UART Modem Control Register                                      | 14-16 |

| 3.5 UART Tx/Rx Status Register                                       | 14-17 |

| 3.6 UART Error Status Register                                       | 14-18 |

| 3.7 UART FIFO Status Register                                        | 14-19 |

| 3.8 UART Modem Status Register                                       | 14-20 |

| 3.9 UART Transmit BUffer register (Holding Register & FIFO Register) | 14-21 |

| 3.10 UART Receive BUffer Register (Holding Register & FIFO Register) | 14-21 |

| 3.11 UART Baud RATE Divisor Register                                 | 14-22 |

| 3.12 UART Dividing Slot Register                                     | 14-23 |

|                                                                      |       |

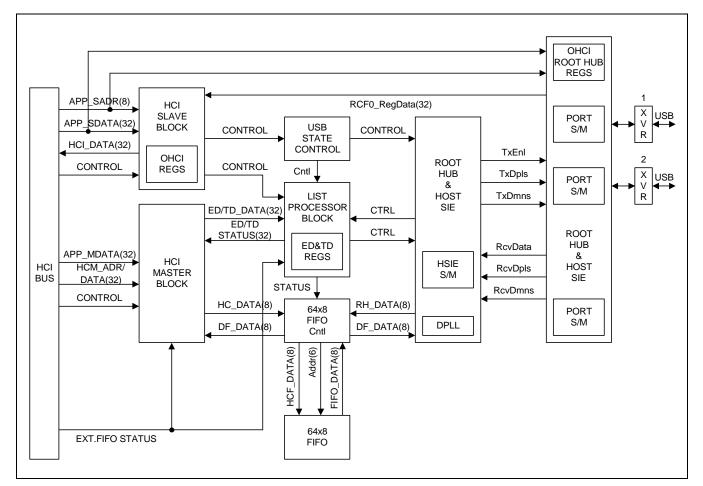

### Chapter 15 USB Host Controller

| 1 Overview                                | 14-1 |

|-------------------------------------------|------|

| 1.1 USB Host Controller Special Registers | 14-2 |

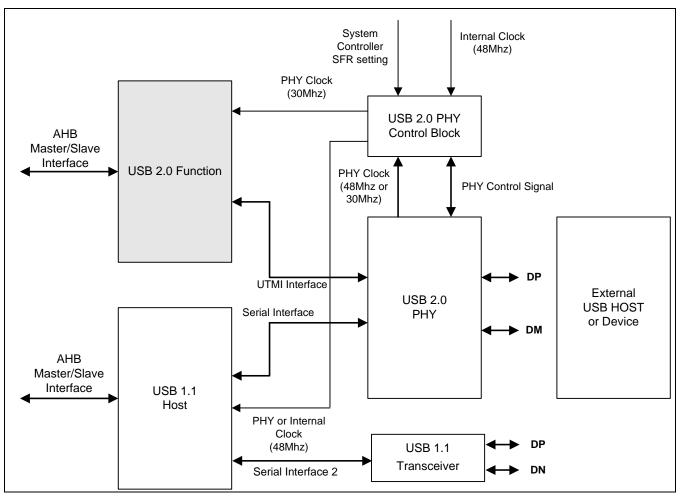

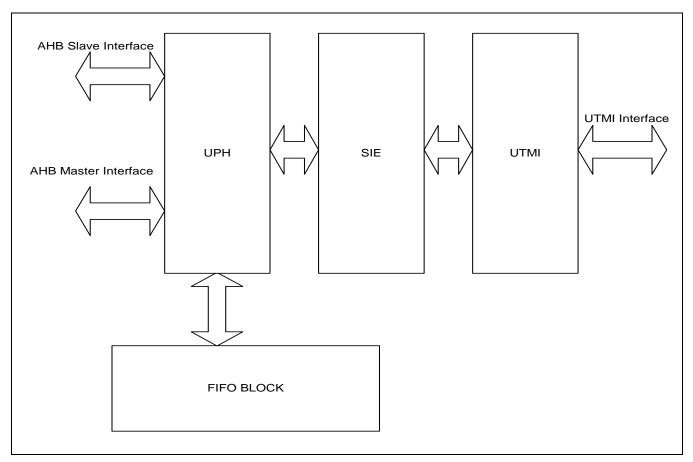

# Chapter 16 USB 2.0 Function

| 1 Overview                                                 | 6-1  |

|------------------------------------------------------------|------|

| 1.1 Feature                                                | 6-1  |

| 2 Block Diagram1                                           |      |

| 3 To Activate USB Port1 for USB 2.0 Function10             | 6-3  |

| 4 SIE (Serial Interface Engine)10                          |      |

| 5 UPH (Universal Protocol Handler)10                       |      |

| 6 UTMI (USB 2.0 Transceiver Macrocell Interface)10         |      |

| 7 USB 2.0 Function Controller Special Registers1           | 6-5  |

| 8 Registers1                                               |      |

| 8.1 Index Register (IR)10                                  |      |

| 8.2 Endpoint Interrupt Register (EIR)1                     |      |

| 8.3 Endpoint Interrupt Enable Register (EIER)1             |      |

| 8.4 Function Address Register (FAR)10                      |      |

| 8.5 ENdpoint Direction Register (EDR)1                     |      |

| 8.6 Test Register (TR)10                                   |      |

| 8.7 System Status Register (SSR)10                         |      |

| 8.8 System Control Register (SCR)1                         |      |

| 8.9 EP0 Status Register (EP0SR)10                          |      |

| 8.10 EP0 Control Register (EP0CR)10                        |      |

| 8.11 Endpoint# Buffer Register (EP#BR)10                   |      |

| 8.12 Endpoint Status Register (ESR)1                       |      |

| 8.13 Endpoint Control Register (ECR)10                     |      |

| 8.14 Byte read Count Register (BRCR)10                     | 6-22 |

| 8.15 Byte Write Count Register (BWCR)10                    |      |

| 8.16 MAX Packet Register (MPR)10                           |      |

| 8.17 DMA Control Register (DCR)10                          |      |

| 8.18 DMA Transfer Counter Register (DTCR)                  |      |

| 8.19 DMA FIFO Counter Register (DFCR)                      |      |

| 8.20 DMA Total Transfer Counter Register 1/2 (DTTCR 1/2)10 |      |

| 8.21 DMA Interface Control Register (DICR)10               |      |

| 8.22 Memory Base Address Register (MBAR)10                 |      |

| 8.23 Memory Current Address Register (MCAR)                |      |

| 8.24 Burst FIFO Control Register(FCON)                     |      |

| 8.25 Burst FIFO Status Register(FSTAT)10                   |      |

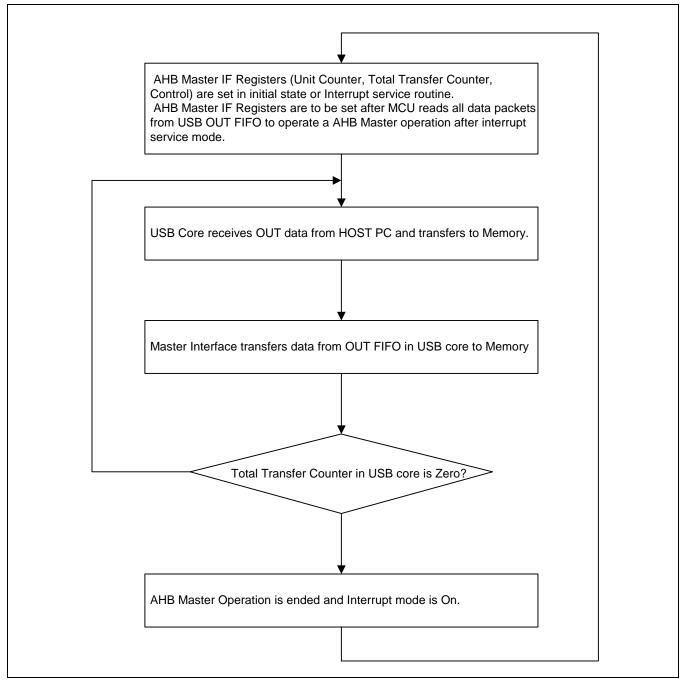

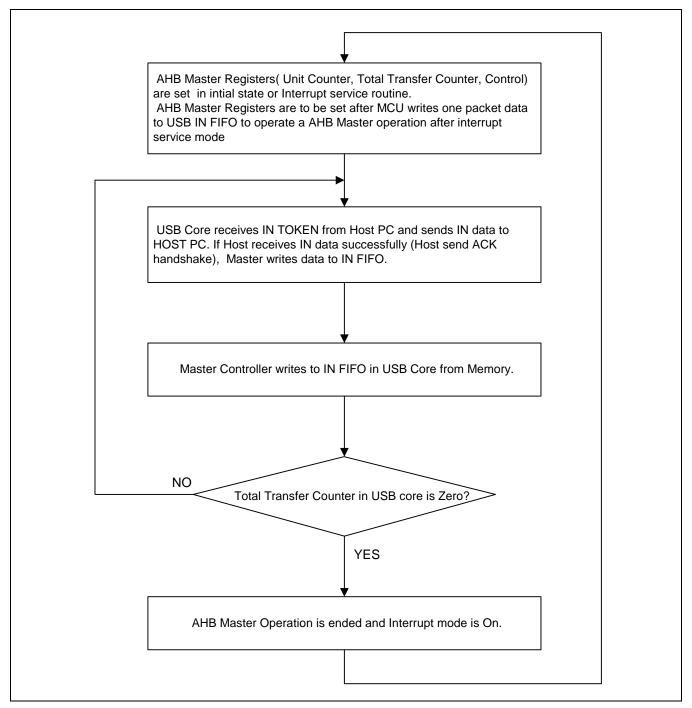

| 8.26 AHB Master(DMA) Operation Flow Chart10                | 6-32 |

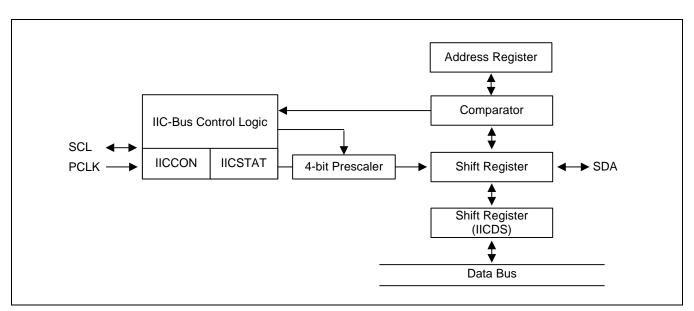

# Chapter 17 IIC-Bus Interface

| 1 Overview                                                            |                    |

|-----------------------------------------------------------------------|--------------------|

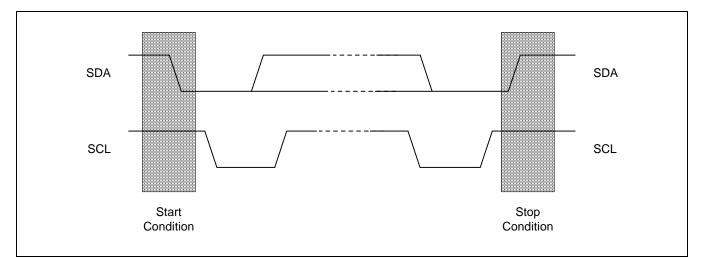

| 1.1 IIC-Bus Interface                                                 |                    |

| 1.2 Start And Stop Conditions                                         |                    |

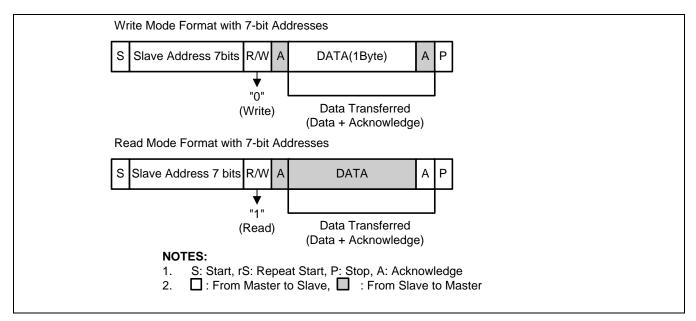

| 1.3 Data Transfer Format                                              |                    |

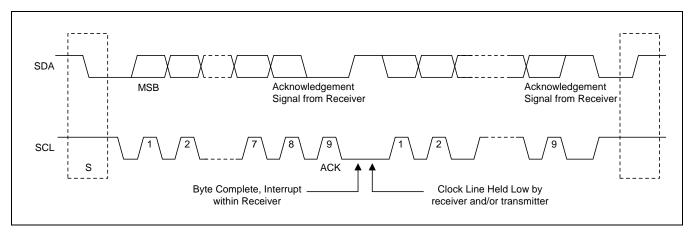

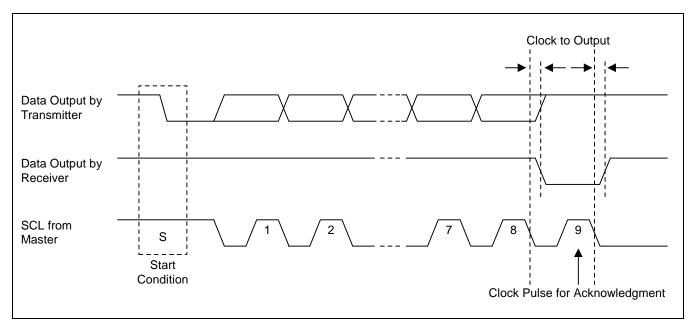

| 1.4 ACK Signal Transmission                                           |                    |

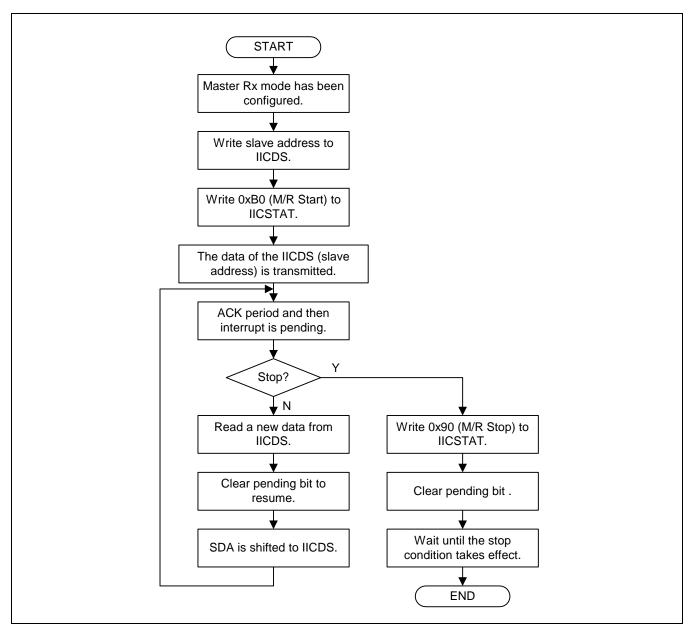

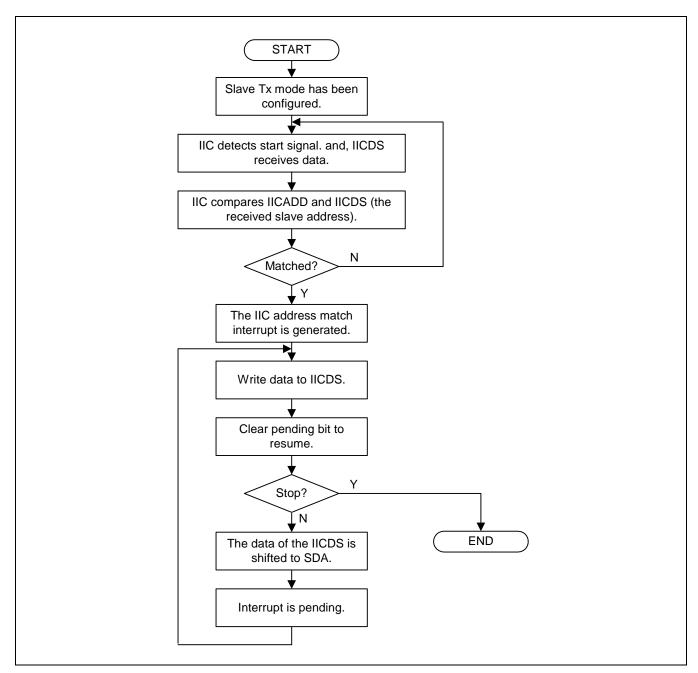

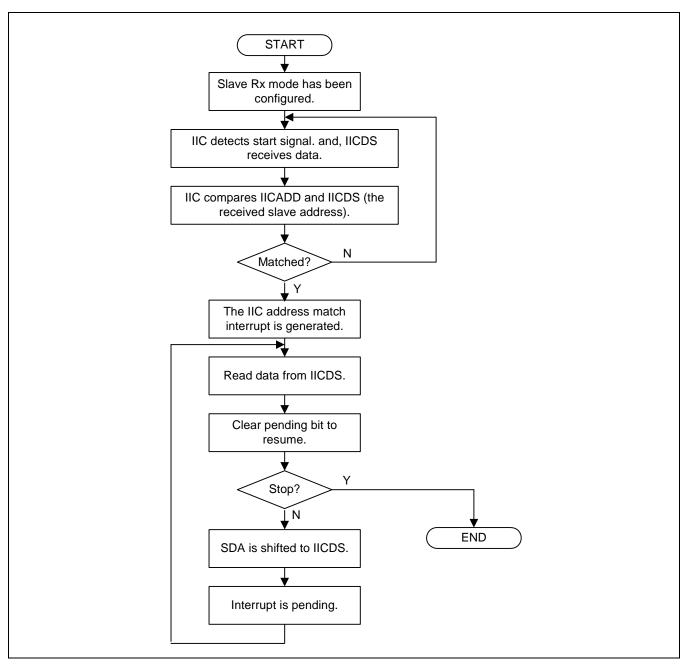

| 1.5 Read-Write Operation                                              |                    |

| 1.6 Bus Arbitration Procedures                                        |                    |

| 1.7 Abort Conditions                                                  |                    |

| 1.8 Configuring IIC-Bus                                               |                    |

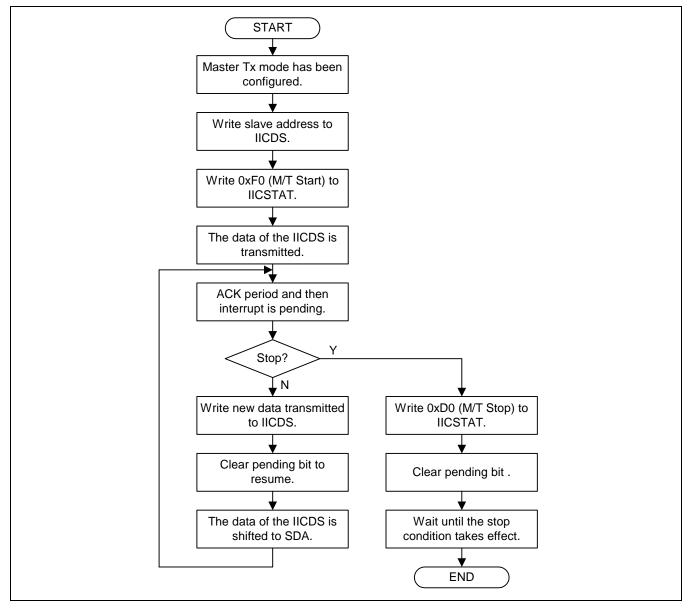

| 1.9 Flowcharts of Operations in Each Mode                             |                    |

| 2 IIC-Bus Interface Special Registers                                 |                    |

| 2.1 Multi-Master IIC-Bus Control (IICCON) Register                    |                    |

| 2.2 Multi-Master IIC-Bus Control/Status (IICSTAT) Register            |                    |

| 2.3 Multi-Master IIC-Bus Address (IICADD) Register                    |                    |

| 2.4 Multi-Master IIC-Bus Transmit/Receive Data Shift (IICDS) Register | <sup>.</sup> 17-13 |

| 2.5 Multi-Master IIC-Bus Line Control(IICLC) Register                 |                    |

# Chapter 18 2D

| 1 Introduction                  | 18-1  |

|---------------------------------|-------|

| 1.1 Features                    | 18-1  |

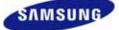

| 2 Color Format Conversion       | 18-2  |

| 3 Command FIFO                  | 18-3  |

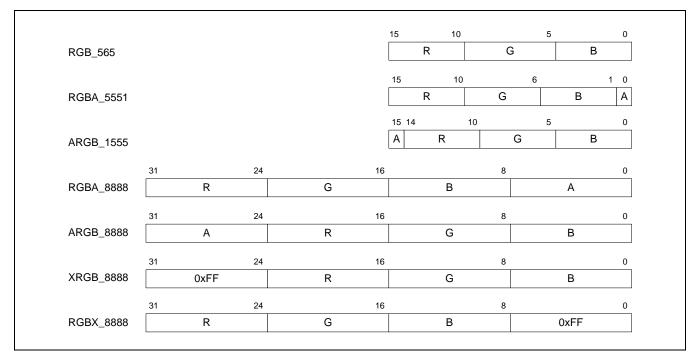

| 4 Rendering Pipeline            | 18-4  |

| 4.1 Primitive Drawing           | 18-4  |

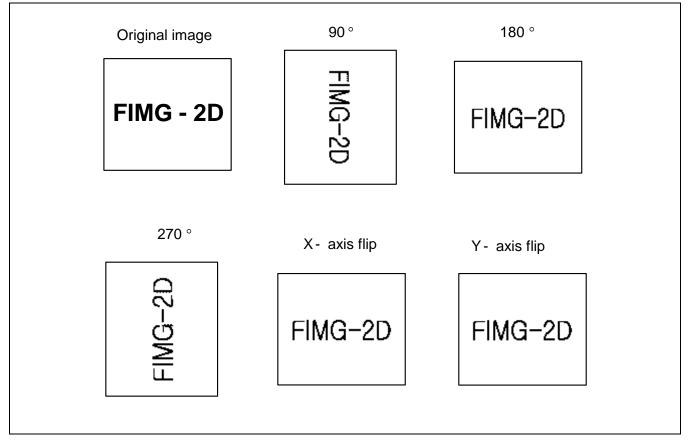

| 4.2 Rotation                    | 18-9  |

| 4.3 Clipping                    | 18-11 |

| 4.4 Stencil Test                | 18-11 |

| 4.5 Raster Operation            | 18-11 |

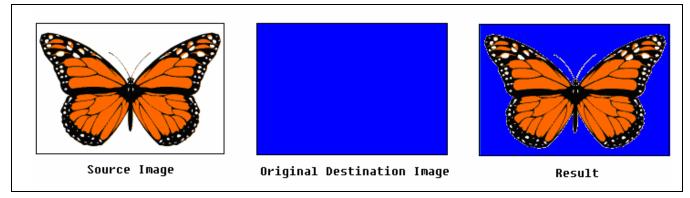

| 4.6 Alpha Blending              | 18-13 |

| 5 Register Descriptions         | 18-14 |

| 5.1 General Registers           | 18-16 |

| 5.2 Command Registers           | 18-19 |

| 5.3 Parameter Setting Registers | 18-21 |

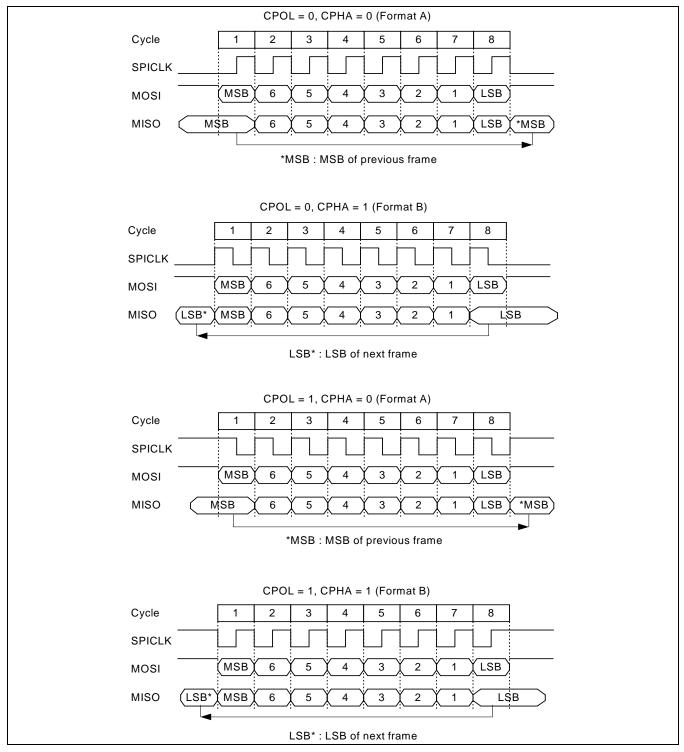

# Chapter 19 HS\_SPI Controller

| 1 Overview                               |        |

|------------------------------------------|--------|

| 2 Features                               |        |

| 3 Signal Descriptions                    |        |

| 4 Operation                              |        |

| 4.1 Operation Mode                       |        |

| 4.2 FIFO Access                          |        |

| 4.3 Trailing Bytes in the Rx FIFO        |        |

| 4.4 Packet Number Control                |        |

| 4.5 NCS Control                          |        |

| 4.6 HS_SPI Transfer Format               |        |

| 5 External Loading Capacitance           |        |

| 6 Special Function Register Descriptions |        |

|                                          | er19-5 |

|                                          |        |

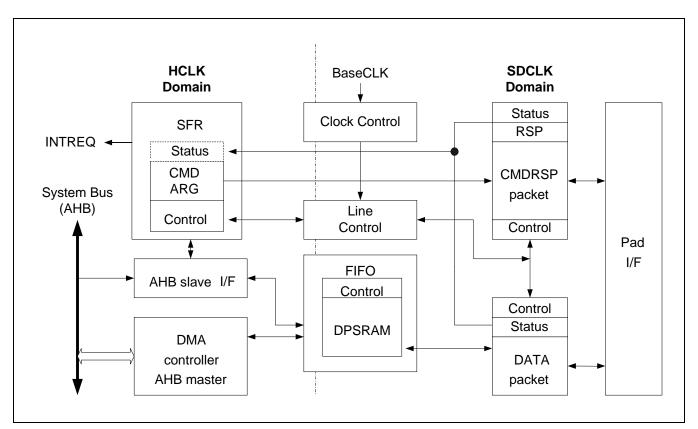

### Chapter 20 SD/MMC Host Controller

| 1 Overview                                                 | 20-1  |

|------------------------------------------------------------|-------|

| 2 Features                                                 | 20-1  |

| 3 Block Diagram                                            | 20-2  |

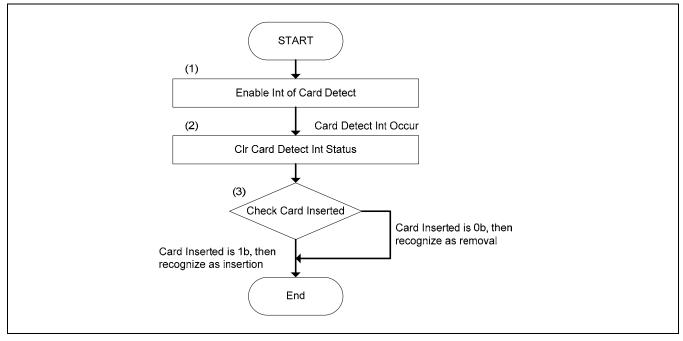

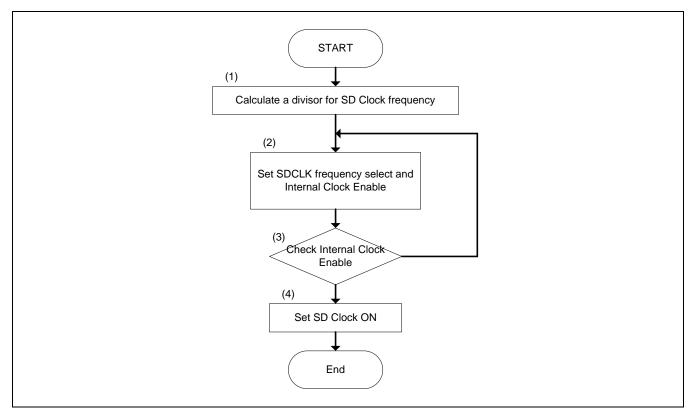

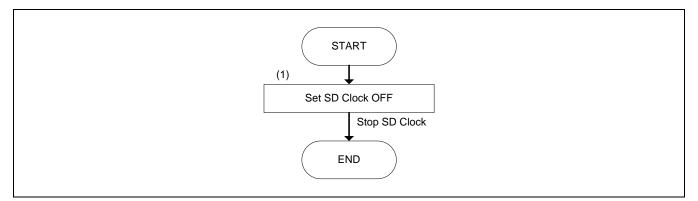

| 4 Sequence                                                 | 20-3  |

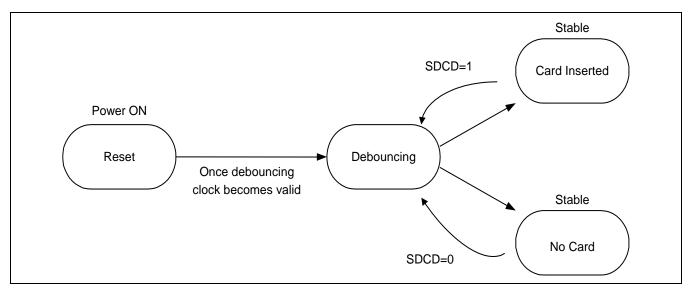

| 4.1 SD Card Detection Sequence                             | 20-3  |

| 4.2 SD Clock Supply Sequence                               | 20-4  |

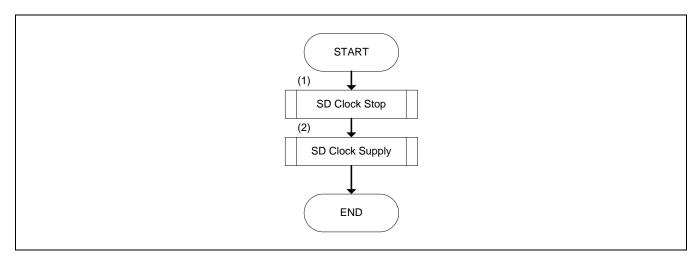

| 4.3 SD Clock Stop Sequence                                 |       |

| 4.4 SD Clock Frequency Change Sequence                     | 20-5  |

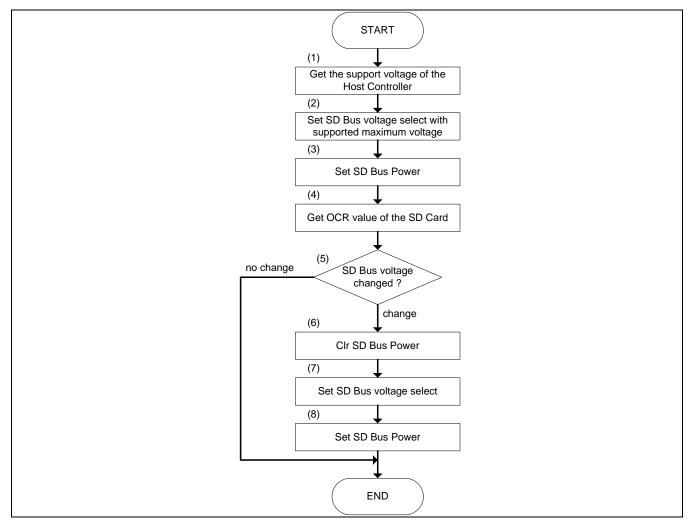

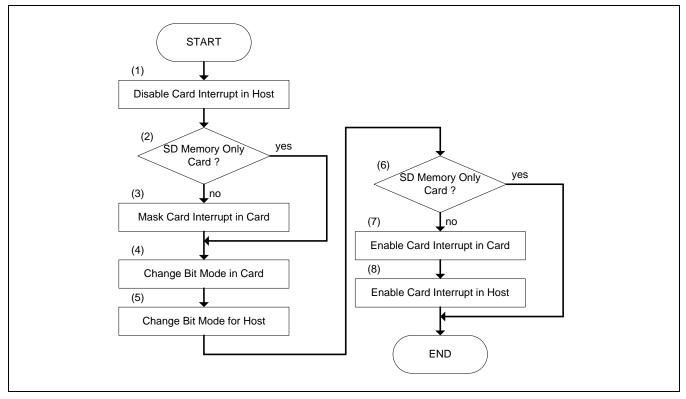

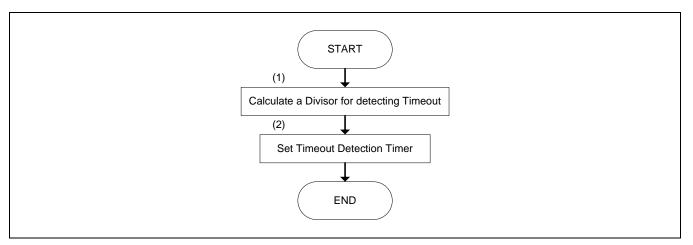

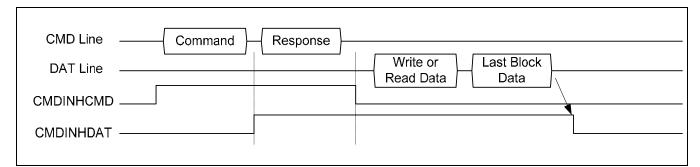

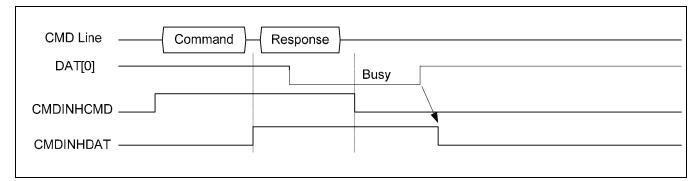

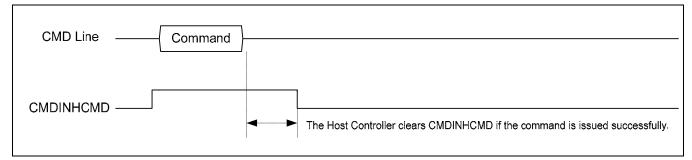

| 4.5 SD Bus Power Control Sequence                          | 20-6  |