# AUTOMATIC GAIN CONTROL (AGC) USING THE DIAMOND TRANSISTOR OPA660

By Christian Henn, Burr-Brown International GmbH

Multiplication of analog signals has long been one of the most important nonlinear functions of analog circuit technology. Many signal sources, however, such as CCD sensors, pin diodes, or antennas, deliver weak, oscillating, and simultaneously wide-band signals. But now a new multiplication method is available. Used as a wide-bandwidth Automatic Gain Control (AGC) application circuit, the integrated circuit OPA660 varies its own gain to change the signal amplitude and keep the output signal constant over a wide input voltage range. The OPA660 thus makes it possible to control and amplify signals with no additional multiplier. Important parameters include the differential gain (DG), the thermally induced pulse distortion, and the signal-to-noise ratio (S/N).

An analog multiplier delivers an output signal (voltage or current) that is proportional to the product of two or more inputs. The application circuit presented here is concerned primarily with two inputs. In the simplest case, each of the two inputs can function with both polarities. In this case, the input voltage swing covers all four quadrants; that is, there are four polarity combinations. In contrast to a four quadrant multiplier, a two quadrant multiplier allows only one input to be connected to a signal of any polarity. The second input can only process unipolar signals.

Multipliers are nonlinear and thus can not be implemented as simply and exactly as linear components. In developing the circuit, various design methods were used depending upon the accuracy, bandwidth, and justifiable complexity. Multipliers do have several disadvantages, including linearity errors, temperature dependence, less than ideal crosstalk, and limited bandwidth, but the multiplication function presented here functions directly and has variable transconductance, enabling it to achieve the largest possible bandwidth.

### AGC WITH THE DIAMOND TRANSISTOR

The voltage-controlled current source of the OPA660 from Burr-Brown has acquired various nicknames according to its applications:

Operational Transconductance Amplifier (OTA) Current Conveyor Diamond Transistor Ideal Transistor Macrotransistor

Applications for the OPA660 are usually amplifier circuits. But although the OPA660's connection pin,  $I_{O}$ , adjusts functions primarily as a power supply switch or

quiescent current programmer, it can also be used for multiplicative applications.

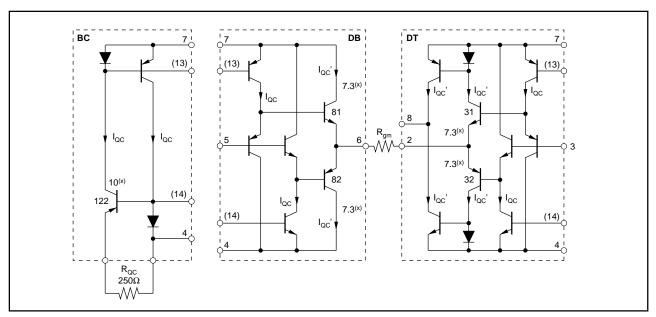

Figure 1 illustrates the dependance of the transconductance (gm =  $d(I_{OUT})/d(V_{IN})$ ) upon the resistance,  $R_{QC}$ . The following equation can be derived from the idealized OPA660 model circuits shown in Figure 2.

$$I_{QC} = \frac{V_{T}}{R_{QC}} \ell n (n)$$

When the temperature voltage  $(V_T)$  is 25.86mV, the quiescent current resistance  $(R_{QC})$  is 250 $\Omega$ , and the scale factor (n) of the transistor  $R_{122}$  is 10, the cross current  $I_{QC}$  can be calculated as follows:

$$I_{QC} = \frac{25.86 \text{mV}}{250\Omega} \ln(10) = 238 \mu \text{A}$$

The quiescent current of the subsequent transistor stages can be calculated with a scale factor (a) of 7.3 for transistors 31, 32, 81, and 82 to

$$I_{OC}' = a \cdot I_{OC} = 7.3 \cdot 238 \mu A = 1.74 mA$$

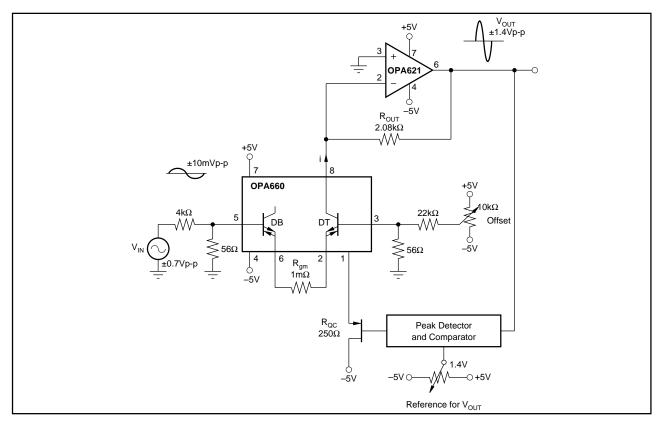

FIGURE 1. Schematic Diagram of the Multiplication Function.

FIGURE 2. Idealized Model Circuit.

Now it is easy to determine the transconductance using the following equation:

$$gm = \frac{I_{QC}}{V_{T}} = \frac{a \cdot ln(n)}{R_{QC}} = 67mA/V$$

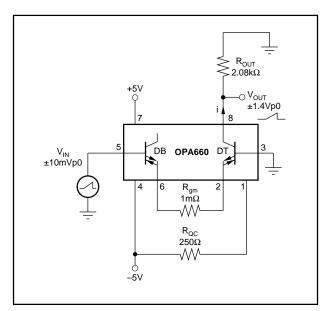

The circuit diagram of the actual multiplier circuit as illustrated in Figure 3 makes it easier to determine the multiplication constant, M. The signal current at Pin 8 produces the following output voltage at the resistor  $R_{\text{OUT}}$ :

$$V_{\text{OUT}} = i \bullet R_{\text{OUT}} = V_{\text{IN}} \bullet \text{gm} \bullet R_{\text{OUT}} = V_{\text{IN}} \bullet \frac{M}{R_{\text{OC}}}$$

When the resistor ( $R_{OUT}$ ) has  $2.08k\Omega$  and the input voltage is  $\pm 10mV$ , the output voltage reaches the following value:

$$\begin{aligned} V_{OUT} &= \frac{-\mathbf{a} \cdot \ln(\mathbf{n}) \cdot R_{OUT}}{R_{QC}} \\ &= \pm 10 \text{mV} \frac{7.3 \cdot \ln(10) \cdot 2.08 \text{k}\Omega}{250\Omega} = \pm 1.4 \text{V} \end{aligned}$$

The multiplication constant M can be derived directly from the equation as follows:

$$M = a \cdot ln(n) \cdot R_{OUT} = 7.3 \cdot ln(10) \cdot 2.08k\Omega = 35k\Omega$$

The gain G can be calculated using the equation:

$$G = \frac{d(V_{OUT})}{d(V_{DI})} = \frac{M}{R_{OC}} = \frac{35k\Omega}{250\Omega} = 140$$

# DETERMINING THE DIFFERENTIAL GAIN (DG)

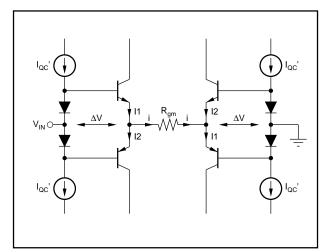

Figure 4 shows the circuit part important for the multiplication. When  $V_{\text{IN}}=0$ , i=0, and  $I_1=I_2=I_{\text{QC}}$ , i increases with rising  $V_{\text{IN}}$ , resulting in variation of the currents  $I_1$  and  $I_2$ . The increase in both currents also changes the transconductance

gm, since it is dependent upon the modulation. This change results in turn in signal distortion. The following equations derive the relation between the signal amplitude and distortion.

$$i = I_1 - I_2 = I_{QC'} \left[ Exp \left( + \frac{\Delta V}{V_T} \right) - Exp \left( - \frac{\Delta V}{V_T} \right) \right]$$

$$i = -I_{oc}' [Exp (-\phi) - Exp (+\phi)] = -2I_{oc}' \cdot sinh (\phi)$$

$$\phi = \frac{\Delta V}{V_{\scriptscriptstyle T}} = \frac{V_{\scriptscriptstyle IN} - R_{\scriptscriptstyle gm} \bullet i}{2V_{\scriptscriptstyle T}} = \frac{V_{\scriptscriptstyle IN} + 2I_{\scriptscriptstyle QC}' R_{\scriptscriptstyle gm} \bullet \sin\! h \, (\phi)}{2V_{\scriptscriptstyle T}}$$

$$V_{IN} = 2V_{T} \cdot \varphi - 2I_{OC}' R_{gm} \cdot \sin h (\varphi)$$

$$\frac{\mathrm{d(i)}}{\mathrm{d}(\varphi)} = -2\mathrm{I}_{\mathrm{QC}}' \bullet \cosh(\varphi)$$

$$\frac{d(V_{IN})}{d(\phi)} = -2V_T - 2I_{QC}' R_{gm} \cdot \cosh(\phi)$$

$$cosh (\varphi) = \sqrt{\sin h^2 (\varphi) + 1} = \sqrt{\left(\frac{i/I_{QC}}{2}\right)^2 + 1}$$

$$gm = \frac{d(i)}{d(V_{IN})} = \frac{d(i)/d(\phi)}{d(V_{IN})/d(\phi)} = \frac{1}{R_{gm} - \frac{V_T}{I_{OC}' \cos h (\phi)}}$$

$$= \frac{1}{R_{gm} + \frac{V_{T}}{I_{QC}' \sqrt{\left(\frac{i/I_{QC}'}{2}\right)^{2} + 1}}}$$

$$I_{QC'} = \frac{a \cdot ln(n) \cdot V_{T}}{R_{QC}}$$

$$gm_{_{0}}=\left.\frac{1}{R_{_{om}}\!+V_{_{T}}\!/I_{_{OC}}\!'}\right|\,i=0$$

$$DG = \frac{gm_{MAX}}{gm_0} - 1 = \frac{R_{gm} + V_T/I_{QC}'}{R_{gm} + \frac{V_T/I_{QC}'}{\sqrt{\left(\frac{i_{MAX}/I_{QC}'}{2}\right)^2 + 1}}}$$

FIGURE 3. Multiplier Circuit.

FIGURE 4. Multiplier Section.

The following applies for low modulation:

$$i_{\text{MAX}} \approx \frac{V_{\text{INMAX}}}{R_{\text{gm}} + V_{\text{T}}/I_{\text{QC}}}$$

In the extreme case in which  $R_{\rm gm} = 0$ , the following results: or for low modulation:

$$DG \approx \frac{R_{gm} + V_{T}/I_{QC}'}{R_{gm} + \sqrt{\left(\frac{V_{IN}/I_{QC}'}{2(R_{gm} + V_{T}/I_{QC}')}\right)^{2} + 1}}$$

$$\approx \frac{a \cdot \ln(n) \ R_{gm} / (R_{QC} + 1)}{a \ \ln(n) \ R_{gm} / R_{QC} + \frac{1}{\sqrt{\left[\frac{V_{IN} / V_{T}}{2 \ (a \cdot \ln(n) \ R_{gm} / (R_{QC} + 1)\right]^{2} + 1}}} - 1$$

$$DG_0 = \sqrt{\left(\frac{i_{MAX}/I_{QC}'}{2}\right) + 1} - 1$$

$$DG_0 \approx \sqrt{\left(\frac{V_{\text{INMAX}}}{2V_{\text{T}}}\right)^2 + 1} - 1$$

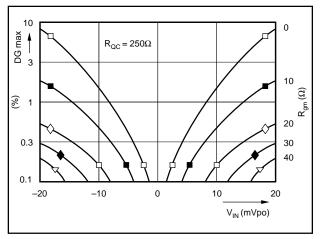

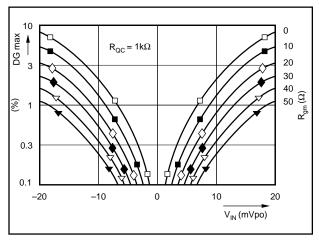

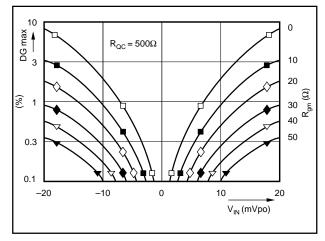

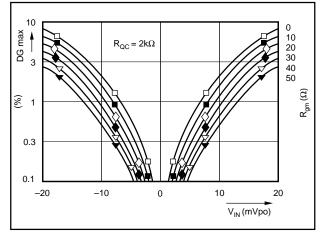

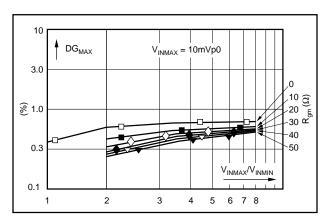

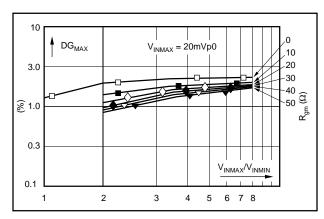

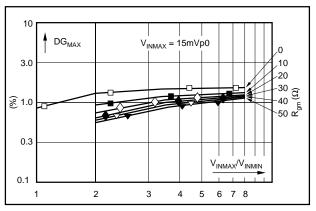

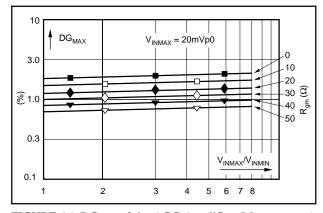

Figures 5 through 8 show an analysis of the equation DG = f ( $V_{IN}$ ;  $R_{gm}$ ;  $R_{QC}$ ), which determines the differential gain error dependent upon the input voltage. The figures include the open-loop gain resistance ( $R_{gm}$ ) and quiescent current resistance ( $R_{QC}$ ).

As is evident,  $R_{\rm gm}$  produces transfer linearization, but it also reduces the gain,  $G_{\rm Rem}$

$$G_{Rgm} = \frac{d(V_{OUT})}{d(V_{IN})} = \frac{R_{OUT}}{R_{gm} + V_{T}/I_{QC}}$$

$$= \frac{R_{OUT}}{R_{gm} + \frac{R_{QC}}{a \cdot \ln(n)}} \quad | \quad i = 0$$

As will be shown later, the gain reduction results in a poorer signal-to-noise ratio (S/N). Designers can determine the best performance compromise for DG and S/N by choosing appropriate values for  $V_{\rm INMAX}$  and  $R_{\rm gm}$ . However, the larger the control range —that is, the greater the variation of  $R_{\rm QC}$ —the poorer the quality of the compromise that can be attained.

FIGURE 5. Differential Gain Error ( $R_{OC} = 250\Omega$ ).

FIGURE 7. Differential Gain Error ( $R_{oc} = 1k\Omega$ ).

When  $R_{\rm gm}$  is inserted, the relation between the gain,  $G_{Rgm}$  and the control value,  $1/R_{\rm OC}$ , becomes disproportionate.

## **AUTOMATIC GAIN CONTROL (AGC)**

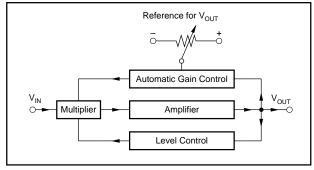

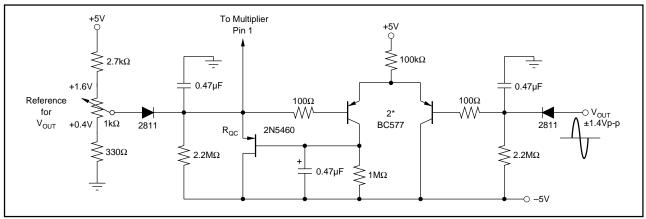

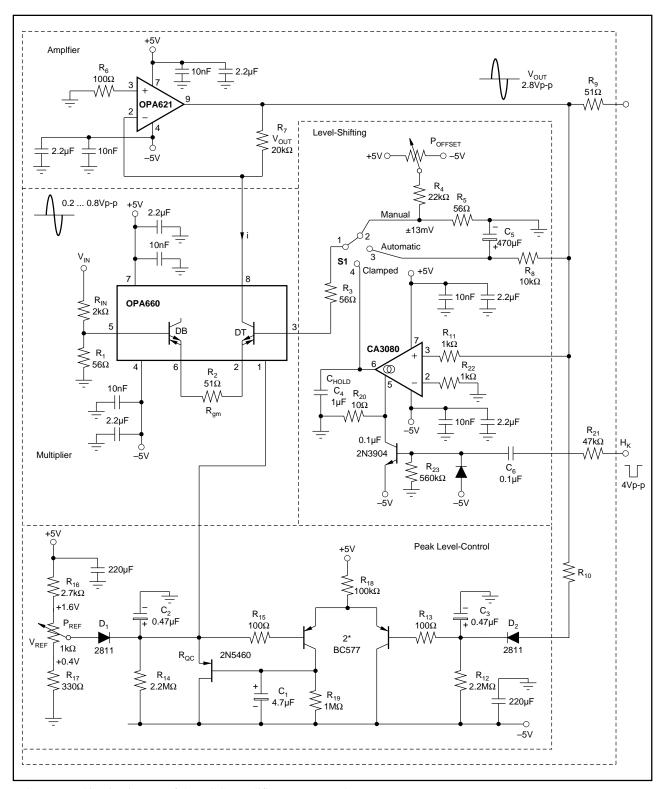

Circuit tolerances and insufficient temperature compensation result in undefined gains ( $G_{Rgm} = f(R_{QC})$ ) of about  $\pm 25\%$ . If  $R_{QC}$  is implemented by a FET, this undefined gain range increases even more. These problems can be avoided by using an AGC circuit as shown in Figure 9.

In the detailed circuit in Figure 10, the  $\pm 0.7V$  input signal  $(V_{IN})$ , which is assumed for now as a constant, is divided by the input divider  $(4k\Omega/56\Omega)$  to about  $\pm 10mV$ . The  $4k\Omega$  resistor in front of the circuit can, of course, be removed if the input amplitude is only in the mV range, as is the case in fiber optic transmission receivers. The amplifier (OPA621) placed after the circuit converts the output current i of the multiplier (OPA660) into voltage. The peak detector and comparator compare the  $\pm 1.4V$  output signal  $(V_{OUT})$  with the given reference value +1.4V and connect the control voltage to the FET. This control ensures that the peak value of  $V_{OUT}$  is identical to the adjustable reference DC voltage and is

FIGURE 6. Differential Gain Error ( $R_{OC} = 500\Omega$ ).

FIGURE 8. Differential Gain Error ( $R_{OC} = 2k\Omega$ ).

FIGURE 9. AGC Circuit (Schematic).

unaffected by circuit tolerances. It is also possible to control the output voltage against the black level or synchronization level by acquiring the output voltage for comparison only during the horizontal sync time. While the luminance signal changes over time, the sync level is always transmitted with constant amplitude. Such regulation enables the video signal to be transmitted at a constant amplitude despite changes in the luminance signal.

FIGURE 10. AGC Amplifier for Various Signals.

FIGURE 11. Peak Level.

Variations in the input signal amplitude cause the control system to produce constant output signal amplitudes corresponding to the reference value. Simultaneous changes in  $V_{\rm IN}$  and the reference value are also possible.

# DETERMINING THE MAXIMUM DIFFERENTIAL GAIN ( $\mathrm{DG}_{\mathrm{Max}}$ ) OF AGC AMPLIFIERS

The input voltage of AGC amplifiers varies from  $V_{\scriptscriptstyle INMIN}$  to  $V_{\scriptscriptstyle INMAX}.$  To maintain a constant output voltage ( $V_{\scriptscriptstyle OUT}$ ) over this range, the control voltage from the peak level control varies the resistance  $R_{\scriptscriptstyle QC}$  correspondingly from  $R_{\scriptscriptstyle QCMIN}$  to  $R_{\scriptscriptstyle QCMAX}.$  The largest signal distortions measured as

FIGURE 12. Clamp Circuit for TV Signals.

differential gain ( $DG_{MAX}$ ) happen at  $V_{INMAX}$  or  $R_{QCMAX}$ , thus during operation of the OPA660 with the smallest quiescent current  $I_Q$ . For the control range q of the AGC amplifier, the following conditions apply:

$$\begin{aligned} q &= \frac{V_{_{INMAX}}}{V_{_{INMIN}}} \\ R_{_{QCMAX}} &= q \bullet R_{_{QCMIN}} + a \bullet ln(n) \bullet R_{_{gm}} \bullet (q-1) \\ B &= a \bullet ln(n) \bullet R_{_{gm}}/R_{_{QCMAX}} \end{aligned}$$

From these equations, it is possible to derive the maximum distortion,  $DG_{MAX}$ , as a function of B and the maximum input voltage.

$$DG_{MAX} = \frac{B+1}{B+\frac{1}{\sqrt{\left(\frac{V_{INMAX}/V_{T}}{2(B+1)}\right)^{2}+1}}}$$

FIGURE 13.  $DG_{MAX}$  of the AGC Amplifier (Simulation)  $(V_{INMAX} = \pm 10 \text{mV}).$

FIGURE 15.  $DG_{MAX}$  of the AGC Amplifier (Simulation)  $(V_{INMAX} = \pm 20 mV).$

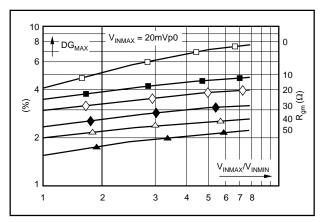

It should be kept in mind, however, that this equation is based upon the simplified model shown in Figure 2 and sometimes deviates from measurements and simulation results. The measurements, for example, also include distortion from the subsequent amplifier OPA621. Figures 13 to 15 give an overview of the achievable distortion. For maximum input voltages ( $V_{\rm INMAX}$ ) from ±10mV to ±20mV and open-loop resistances from 0 $\Omega$  to 50 $\Omega$ , the differential gain shown in simulations is a function of the ratio  $V_{\rm INMAX}/V_{\rm INMIN}$  and equals 9. Figure 16 presents measured achievable distortions in the AGC structure, as already shown in Figure 10.

#### THERMALLY INDUCED DISTORTION

As shown in Figure 2, the power consumption of transistors 31, 32, 81, and 82 varies according to the signal curve. This variation leads to temperature oscillation and finally to change in the transconductance gm.

At first glance, it looks as if the pulse distortion is caused by RC parts. The visible thermal time constant, however, is in the microsecond range and is negatively affected by unequal temperature distribution on the chip.

As Figure 17 shows,  $R_{\rm gm}$  can reduce this thermally induced pulse distortion.

FIGURE 14.  $DG_{MAX}$  of the AGC Amplifier (Simulation)  $(V_{INMAX} = \pm 15 \text{mV}).$

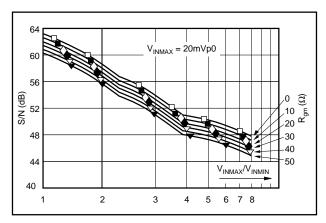

FIGURE 16.  $DG_{MAX}$  of the AGC Amplifier (Measurement)  $(V_{INMAX} = \pm 20mV)$ .

In contrast, periodic RF signals less than 1MHz are barely affected by the pulse distortion. The temperature change can no longer follow the signal change, resulting in more balanced temperature distribution on the chip.

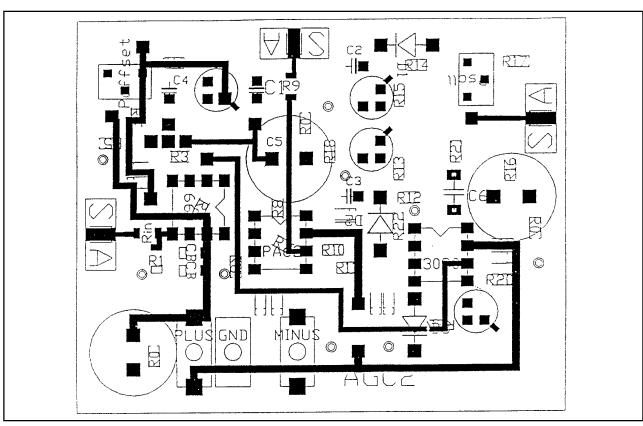

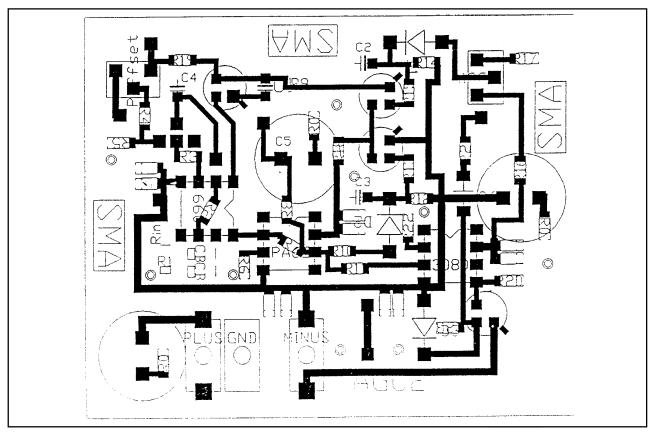

### **DEMO BOARD**

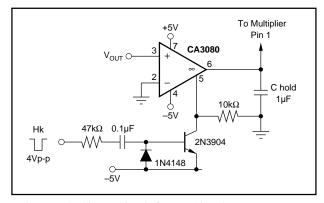

All available measurements were conducted using the completely dimensioned circuit shown in Figure 19. The demo board designed for this application contains four circuit blocks. As a differential amplifier with current output, the OPA660 allows users to control the transconductance by varying the total quiescent current. Functioning mainly as a multiplier, it also enables a shift in DC position of the output voltage by varying the noninverting OPA660 input. The OPA621 functions as a current-to-voltage converter and amplifies the signal. The switch, S1, in the shift block lets the user choose between manual, and automatic offset compensation, and clamped DC restoration. At active LOW, the clamp pulse triggers the OTA module CA3080, checks the output voltage (Volt) against the reference value for the black level voltage, and stores the correction voltage up to the next clamp pulse  $(H_K)$  in the capacitor  $C_{\text{HOLD}}$ . The fourth block is the already mentioned peak level control circuit. The discrete differential amplifier checks the peak value of the output voltage ( $V_{\text{OUT}}$ ) against the reference voltage set by P<sub>REF</sub>. The transistor 2N5460 changes the quiescent current according to the difference, thus varying the transconductance

For applications requiring frequencies of more than 80 MHz and a controlled output voltage ( $V_{OUT}$ ) of more than  $\pm 1 V$ , we recommend two-stage gain using two OPA621s. With the amplifiers OPA622 and OPA623, it will be possible to increase the bandwidth even more.

FIGURE 17. Effect of  $R_{\rm gm}$  on Thermal Pulse Distortion.

FIGURE 18. S/N of AGC Amplifiers.

FIGURE 19. Circuit Diagram of the AGC Amplifier Demo Board.

FIGURE 20. Layout of the AGC Amplifier Circuit Board — Back.

FIGURE 21. Layout of the AGC Amplifier Circuit Board — Front.

**PARTS LIST**

| NO. | DESIGNATION                                        | PART NAME/VALUE                  | NUMBER<br>OF PARTS |

|-----|----------------------------------------------------|----------------------------------|--------------------|

| 1   | IC,                                                | OPA621KP                         | 1                  |

| 2   | IC <sub>2</sub>                                    | CA3080                           | 1                  |

| 3   | IC <sub>3</sub>                                    | OPA660AP                         | 1                  |

| 4   | T <sub>1</sub> , T <sub>2</sub>                    | BC577                            | 2                  |

| 5   | T <sub>3</sub>                                     | 2N5460                           | 1                  |

| 6   | T <sub>4</sub>                                     | 2N3904                           | 1                  |

| 7   | $D_1, D_2$                                         | 2N2811                           | 2                  |

| 8   | $D_3$                                              | IN4148                           | 1                  |

| 9   | $R_1, R_3, R_5$                                    | $56\Omega$                       | 3                  |

| 10  | R <sub>IN</sub>                                    | 2kΩ                              | 1                  |

| 11  | $R_{qm}$                                           | 51Ω                              | 1                  |

| 12  | R <sub>6</sub> , R <sub>13</sub> , R <sub>15</sub> | 100Ω                             | 3                  |

| 13  | R <sub>7</sub>                                     | 20kΩ                             | 1                  |

| 14  | $R_{_4}$                                           | 22kΩ                             | 1                  |

| 15  | R <sub>8</sub> , R <sub>20</sub>                   | 10kΩ                             | 2                  |

| 16  | R <sub>11</sub> , R <sub>22</sub>                  | 1kΩ                              | 2                  |

| 17  | R <sub>23</sub>                                    | 560kΩ                            | 1                  |

| 18  | R <sub>21</sub>                                    | 47kΩ                             | 1                  |

| 19  | R <sub>10</sub>                                    |                                  | 1                  |

| 20  | R <sub>12</sub> , R <sub>14</sub>                  | 2.2ΜΩ                            | 2                  |

| 21  | R <sub>18</sub>                                    | 100kΩ                            | 1                  |

| 22  | R <sub>17</sub>                                    | 330Ω                             | 1                  |

| 23  | R <sub>16</sub>                                    | 2.7kΩ                            | 1                  |

| 24  | R <sub>19</sub>                                    | 1ΜΩ                              | 1                  |

| 25  |                                                    | Capacitor 2.2μF                  | 6                  |

| 26  |                                                    | Capacitor 10nF                   | 6                  |

| 27  |                                                    | Capacitor 220μF                  | 2                  |

| 28  | $C_2, C_3$                                         | Capacitor 0.47μF                 | 2                  |

| 29  | C <sub>5</sub>                                     | Capacitor 470μF                  | 1                  |

| 30  | C <sub>6</sub>                                     | Capacitor 0.1μF                  | 1                  |

| 31  | C <sub>4</sub>                                     | Capacitor 1μF                    | 1                  |

| 32  |                                                    | $P_{REF}^{}POT1k\Omega$          | 1                  |

| 33  |                                                    | $P_{OFFSET}POT10k\Omega$         | 1                  |

| 34  |                                                    | $V_{IN}$ , $V_{OUT}$ , $H_K$ SMA | 3                  |

| 35  |                                                    | POS, GND, NEG Mini-Banana        | 3                  |