## SHC5320

# High Speed Bipolar Monolithic SAMPLE/HOLD AMPLIFIER

### **FEATURES**

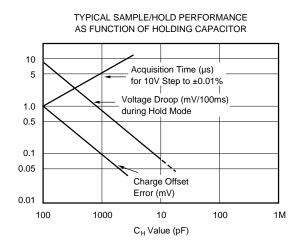

- ACQUISITION TIME TO 0.01%: 1.5µs max

- HOLD MODE SETTLING TIME: 350ns max

- DROOP RATE AT +25°C: 0.5µV/µs max

- TTL COMPATIBLE

- FULL DIFFERENTIAL INPUTS

- INTERNAL HOLDING CAPACITOR

- TWO TEMPERATURE RANGES: -40°C to +85°C (KH, KP, KU) -55°C to +125°C (SH)

- PACKAGE OPTIONS: 14-pin Ceramic, Plastic DIP, and 16-pin SOIC

### **APPLICATIONS**

- PRECISION DATA ACQUISITION SYSTEMS

- DIGITAL-TO-ANALOG CONVERTER DEGLITCHER

- AUTO ZERO CIRCUITS

- PEAK DETECTORS

### DESCRIPTION

The SHC5320 is a bipolar monolithic sample/hold circuit designed for use in precision high-speed data acquisition applications.

The circuit employs an input transconductance amplifier capable of providing large amounts of charging current to the holding capacitor, thus enabling fast acquisition times. It also incorporates a low leakage analog switch and an output integrating amplifier with input bias current optimized to assure low droop rates. Since the analog switch always drives into a load at virtual ground, charge injection into the holding capacitor is constant over the entire input voltage range. As a result, the charge offset (pedestal voltage) resulting from this charge injection can be adjusted to zero by use of the offset adjustment capability. The device includes an internal holding capacitor to simplify ease of application; however, provision is also made to add additional external capacitance to improve the output voltage droop rate.

The SHC5320 is manufactured using a dielectric isolation process which minimizes stray capacitance (enabling higher-speed operation), and eliminates latchup associated with substrate SCRs. The SHC5320KH, KP, and KU feature fully specified operation over the extended industrial temperature range of  $-40^{\circ}$ C to +85°C, while the SHC5320SH operates over the temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C. The device requires  $\pm 15$ V supplies for operation, and is packaged in a reliable 14-pin ceramic or plastic dual-in-line package, as well as a 16-pin surface-mount plastic package.

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706 Tel: (520) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

### SPECIFICATIONS

### ELECTRICAL

At +25°C, rated power supplies, gain = +1, and with internal holding capacitor, unless otherwise noted.

|                                                                                                                                                                                                                                                                                                                     | SHC5320KH, KP, KU                     |                                         |                                   |                            | SHC5320SH                |                              |                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------|-----------------------------------|----------------------------|--------------------------|------------------------------|--------------------------------------------|

| PARAMETERS                                                                                                                                                                                                                                                                                                          | MIN                                   | ТҮР                                     | MAX                               | MIN                        | TYP                      | MAX                          | UNITS                                      |

| INPUT CHARACTERISTICS                                                                                                                                                                                                                                                                                               |                                       |                                         |                                   |                            |                          |                              |                                            |

| ANALOG<br>Voltage Range<br>Common-Mode Range<br>Input Resistance                                                                                                                                                                                                                                                    | ±10<br>±10<br>1                       | 5                                       |                                   | *<br>*<br>*                | *                        |                              | V<br>V<br>MΩ                               |

| Input Capacitance<br>Bias Current<br>Bias Current Over Temperature Range<br>Offset Current<br>Offset Current Over Temperature Range                                                                                                                                                                                 |                                       | ±100<br>±30                             | 3<br>±300<br>±300<br>±300<br>±300 |                            | ±70<br>*                 | ±200<br>±200<br>±100<br>±100 | pF<br>nA<br>nA<br>nA<br>nA                 |

| $\label{eq:Digital} \begin{array}{l} \textbf{Digital} (\text{Over Temperature Range}) \\ V_{IH} (\text{Logic "1"}) \\ V_{IL} (\text{Logic "0"}) \\ I_{IH} (V_{I} = +5V) \\ I_{IL} (V_{I} = 0V) \\ \text{Logic "0"} = SAMPLE \\ \text{Logic "1"} = HOLD \end{array}$                                                 | 2.0                                   |                                         | 0.8<br>0.1<br>4                   | *                          |                          | * * *                        | ν<br>ν<br>μΑ<br>μΑ                         |

| OUTPUT CHARACTERISTICS<br>Voltage Range<br>Current<br>Output Impedance (Hold Mode)<br>Noise, DC to 10MHz: Sample Hold<br>Hold Mode                                                                                                                                                                                  | ±10<br>±10                            | 1<br>125<br>125                         | 200<br>200                        | *                          | * * *                    | *                            | V<br>mA<br>Ω<br>μVrms<br>μVrms             |

| DC ACCURACY/STABILITY<br>Gain, Open Loop, DC<br>Input Offset Voltage<br>Input Offset Voltage Over Temperature Range<br>Input Offset Voltage Drift<br>CMRR <sup>(1)</sup><br>Power Supply Rejection <sup>(2)</sup> :+V <sub>CC</sub><br>-V <sub>CC</sub>                                                             | 3 x 10 <sup>5</sup><br>72<br>80<br>65 | 2 x 10 <sup>6</sup><br>±0.5<br>±5<br>90 | ±1.5<br>±20                       | 10 <sup>6</sup><br>80<br>* | *<br>±0.2<br>*<br>*      | ±2<br>±15                    | V/V<br>mV<br>mV<br>µV/°C<br>dB<br>dB<br>dB |

| HOLD-TO-SAMPLE MODE<br>DYNAMIC CHARACTERISTICS<br>Acquisition Time, $A = -1$ , 10V Step <sup>(3)</sup> :<br>to $\pm 0.01\%$<br>to $\pm 0.1\%$                                                                                                                                                                       |                                       | 1<br>0.8                                | 1.5<br>1.2                        |                            | *                        | *                            | μs<br>μs                                   |

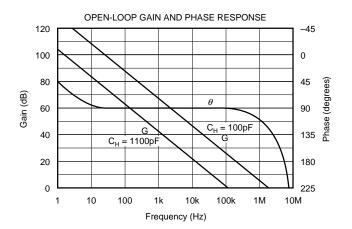

| $\begin{array}{l} \textbf{SAMPLE MODE} \\ \textbf{Gain-Bandwidth Product (Gain = +1)^{(4)}:} \\ \textbf{C}_{H} = 100 \textbf{pF} \\ \textbf{C}_{H} = 100 \textbf{0pF} \\ \textbf{Full Power Bandwidth^{(5)}} \\ \textbf{Slew Rate^{(6)}} \\ \textbf{Rise Time^{(4)}} \\ \textbf{Overshoot^{(4)}} \end{array}$       |                                       | 2<br>180<br>600<br>45<br>100<br>15      |                                   |                            | * * * * *                |                              | MHz<br>kHz<br>kHz<br>V/μs<br>ns<br>%       |

| SAMPLE-TO-HOLD MODE<br>DYNAMIC CHARACTERISTICS<br>Aperture Time <sup>(7)</sup><br>Effective Aperture Time<br>Aperture Uncertainty (Aperture Jitter)<br>Charge Offset (Pedestal) <sup>(8)</sup> (Adjustable to Zero)<br>Charge Transfer <sup>(8)</sup><br>Sample-to-Hold Transient Settling Time<br>to ±0.01% of FSR | -50                                   | 25<br>-25<br>0.3<br>1<br>0.1<br>165     | 0<br>5<br>0.5<br>350              | *                          | * * * * *                | * * *                        | ns<br>ns<br>mV<br>pC<br>ns                 |

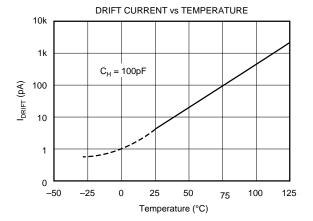

| HOLD MODE<br>Droop <sup>(9)</sup><br>Droop at Maximum Temperature <sup>(9)</sup><br>Drift Current <sup>(9)</sup><br>Drift Current at Maximum Temperature <sup>(9)</sup><br>Feedthrough, 10Vp-p, 100kHz Sinewave                                                                                                     |                                       | 0.08<br>1.2<br>8<br>0.12<br>2           | 0.5<br>100<br>50<br>10            |                            | *<br>17<br>*<br>1.7<br>* | * * * *                      | μV/μs<br>μV/μs<br>pA<br>nA<br>mV           |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

### SPECIFICATIONS (CONT)

### ELECTRICAL

At +25°C, rated power supplies, gain = +1, and with internal holding capacitor, unless otherwise noted.

|                                              | SH         | SHC5320KH, KP, KU |              | SHC5320SH |               |      |       |

|----------------------------------------------|------------|-------------------|--------------|-----------|---------------|------|-------|

| PARAMETERS                                   | MIN        | TYP               | MAX          | MIN       | TYP           | MAX  | UNITS |

| POWER SUPPLIES                               |            |                   |              |           |               |      |       |

| +V <sub>CC</sub>                             | +12        | +15               | +18          | *         | *             | *    | V     |

| -V <sub>cc</sub>                             | -12        | -15               | -18          | *         | *             | *    | V     |

| $+I_{CC}$ ( $+V_{CC} = 15V$ ) <sup>(9)</sup> |            | 11                | 13           |           | *             | *    | mA    |

| $-I_{CC}(-V_{CC} = 15V)^{(9)}$               |            | -11               | -13          |           | *             | *    | mA    |

| TEMPERATURE                                  |            |                   |              |           |               |      |       |

| Specification                                | -40        |                   | +85          | -55       |               | +125 | °C    |

| Storage                                      | -65        |                   | +150         | *         |               | *    | °C    |

| PACKAGE                                      | Hermetic ( | Ceramic, Plast    | ic DIP, SOIC | F         | ermetic Ceram | ic   |       |

\*Specification same as grade to the left.

NOTES: (1)  $V_{CM} = \pm 5VDC$ . (2) Based on a  $\pm 0.5V$  swing for each supply with all other supplies held constant. (3)  $V_O = 10V$  step,  $R_L = 2k\Omega$ ,  $C_L = 50pF$ . (4)  $V_O = 200mVp-p$ ,  $R_L = 2k\Omega$ ,  $C_L = 50pF$ . (5)  $V_{IN} = 20Vp-p$ ,  $R_L = 2k\Omega$ ,  $C_L = 50pF$ . (5)  $V_{IN} = 20Vp-p$ ,  $R_L = 2k\Omega$ ,  $C_L = 50pF$ . (6)  $V_O = 20V$  step,  $R_L = 2k\Omega$ ,  $C_L = 50pF$ . (7) Simulated only, not tested. (8)  $V_{IN} = 0V$ ,  $V_{IH} = +3.5V$ ,  $t_R < 20ns$  ( $V_{IL}$  to  $V_{IH}$ ). (9) Specified for zero differential input voltage between pins 1 and 2. Supply current will increase with differential input (as may occur in the Hold mode) to approximately  $\pm 28mA$  average at 20V differential.

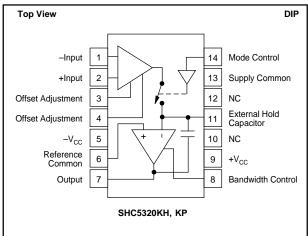

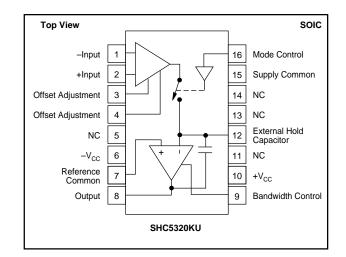

#### **PIN CONNECTIONS**

| Voltage Between +V <sub>CC</sub> and -V <sub>CC</sub> Terminals |                       |

|-----------------------------------------------------------------|-----------------------|

| Input Voltage                                                   | Actual Supply Voltage |

| Differential Input Voltage                                      | ±24V                  |

| Digital Input Voltage                                           | +15V, –1V             |

| Output Current, continuous <sup>(2)</sup>                       | ±20mA                 |

| Internal Power Dissipation                                      | 450mW                 |

| Storage Temperature Range                                       |                       |

| Output Short-Circuit Duration <sup>(3)</sup>                    | None                  |

| Lead Temperature (soldering, 10s)                               | 300°C                 |

NOTES: (1) Absolute maximum ratings are limiting values, applied individually, beyond which the serviceability of the circuit may be impaired. Functional operation under any of these conditions is not necessarily implied. Absolute maximum ratings apply to both dice and package parts, unless otherwise noted. (2) Internal power dissipation may limit output current to less than +20mA. (3) WARNING: This device cannot withstand even a momentary short circuit to either supply.

#### **ORDERING INFORMATION**

| MODEL     | TEMPERATURE<br>RANGE | PACKAGE            |

|-----------|----------------------|--------------------|

| SHC5320KP | -40°C to +85°C       | 14-pin Plastic DIP |

| SHC5320KU | -40°C to +85°C       | 16-pin SOIC        |

| SHC5320KH | -40°C to +85°C       | 14-pin Cerdip      |

| SHC5320SH | -55°C to +125°C      | 14-pin Cerdip      |

### PACKAGE INFORMATION

| MODEL     | PACKAGE            | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|-----------|--------------------|------------------------------------------|

| SHC5320KP | 14-Pin Plastic DIP | 010                                      |

| SCH5320KU | 16-Pin SOIC        | 211                                      |

| SHC5320KH | 14-Pin Cerdip      | 163                                      |

| SHC5320SH | 14-Pin Cerdip      | 163                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

### ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### DICE INFORMATION

|  | PAD    | F      |

|--|--------|--------|

|  | 1      |        |

|  | 2      |        |

|  | 3      |        |

|  | 4      | Offs   |

|  | 5      | Offs   |

|  | 6      |        |

|  | 7      |        |

|  | 8      | Refer  |

|  |        |        |

|  |        |        |

|  | MECH   | IANI   |

|  |        |        |

|  | Die Si | ze     |

|  | Die Th |        |

|  | Min. P | ad Siz |

|  |        |        |

|  |        |        |

|  |        |        |

| PAD | FUNCTION          | PAD | FUNCTION           |

|-----|-------------------|-----|--------------------|

| 1   | –Input            | 9   | Output             |

| 2   | +Input            | 10  | Bandwidth Control  |

| 3   | NC                | 11  | NC                 |

| 4   | Offset Adjustment | 12  | +V <sub>CC</sub>   |

| 5   | Offset Adjustment | 13  | External Hold Cap. |

| 6   | -V <sub>CC</sub>  | 14  | NC                 |

| 7   | NC                | 15  | Supply Common      |

| 8   | Reference Common  | 16  | Mode Control       |

### **MECHANICAL INFORMATION**

|               | MILS (0.001") | MILLIMETERS   |

|---------------|---------------|---------------|

| Die Size      | 140 x 95      | 3.56 x 2.41   |

| Die Thickness | 18 ±0.8       | 0.45 ±0.02    |

| Min. Pad Size | 5 x 5         | 0.127 x 0.127 |

SHC5320 DIE TOPOGRAPHY

### **TYPICAL PERFORMANCE CURVES**

$\pm V_{cc} = 15V.$

### DISCUSSION OF SPECIFICATIONS

### WHAT IS A SAMPLE/HOLD AMPLIFIER?

A sample/hold amplifier (also sometimes called a track-andhold amplifier) is a circuit that captures and holds an analog voltage at a specific point in time under control of an external circuit, such as a microprocessor. This type of circuit has many applications; however, its primary use is in data acquisition systems which require that the voltage be captured and held during the analog-to-digital conversion process. Use of a sample/hold effectively increases the bandwidth of a data acquisition system by a significant amount. For further discussion of this capability, refer to "Signal Digitization" in the Applications section of this data sheet.

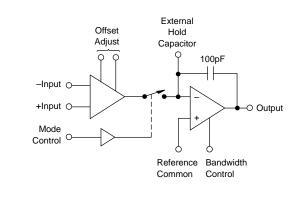

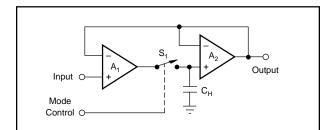

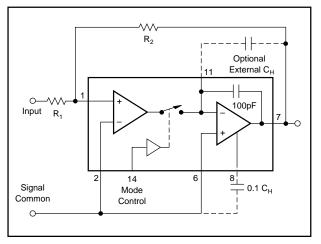

The ideal sample/hold amplifier in its simplest form contains four primary components as illustrated in Figure 1, although in actual practice they may not be internally connected exactly as shown. Amplifier A1, the input buffer, provides a high impedance load to the source circuit and supplies charging current to the holding capacitor C<sub>H</sub>. Switch S<sub>1</sub> opens and closes under external control to gate the buffered input signal to the holding circuit or to remove it so that the most recently sampled signal will be held. Amplifier A<sub>2</sub> serves to present a high impedance load to the holding capacitor and to provide a low impedance voltage source for external loads. A minimum of three terminals are provided for the user: input, output, and mode control (or sample/hold control). When  $S_1$ , is closed, the output signal follows the input signal, subject to errors imposed by amplifier bandwidth and other errors as discussed below. When  $S_1$ , is opened, the voltage stored on the holding capacitor will be held indefinitely (in the ideal case), and will appear at the output of the circuit until S<sub>1</sub>, is again closed under command of the mode control signal.

FIGURE 1. Ideal Sample/Hold Amplifier.

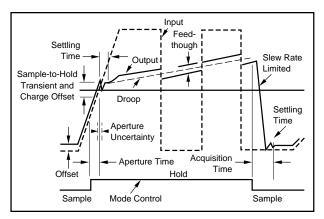

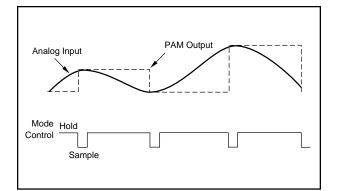

The following discussion of specifications covers the critical types of errors which may be experienced in applications of a sample/hold amplifier. These errors are depicted graphically in Figure 2, and in the Typical Performance Curves.

Acquisition Time is the time required for the sample/hold output to settle within a given error band of its final value after the sample mode is initiated. Included in this time are effects of switch delay time, slew rate of the buffer amplifier, and settling time for a specified change in held voltage value. Slew rate limitations of the buffer amplifier will cause

FIGURE 2. Illustration of Sample/Hold Specifications.

actual acquisition time to be highly dependent on the amplitude of the voltage to be acquired, relative to the value already held by the capacitor. Therefore, proper specification of sample/hold amplifier performance includes definition of both output value step size and required error band accuracy.

Aperture Time (or aperture delay time) is the time required for switch  $S_1$ , to open and remove the charging signal from the capacitor after the mode control signal has changed from "sample" to "hold." This time is measured from the 50% point of the Hold mode transition to the time at which the output stops tracking the input. This parameter is very important in applications for which the input signal is changing very rapidly when the Hold mode is initiated.

*Effective Aperture Time* is the difference in propagation delay times of the analog signal and the mode control signal from their respective input pins to switch  $S_1$ . This time may be negative, zero, or positive. A negative value indicates that the mode control propagation delay is shorter than the analog propagation delay, with the result that the analog value present on the capacitor at the time the switch opens occurred earlier than the application of the mode control signal by the amount of the effective aperture delay time.

*Aperture Uncertainty* (or aperture jitter) is the variation observed in the aperture time over a large number of observations. This parameter is important when the analog input is a rapidly changing signal, as aperture uncertainty contributes to lack of knowledge (at the output) about the true value of the input at the precise time the Hold mode is initiated. The maximum input frequency for a given acceptable error contribution due to aperture uncertainty is

### $f_{MAX} = Maximum Fractional Error/2\pi t_U$

where Maximum Fractional Error (MFE) is the ratio of the maximum allowable error voltage to peak voltage, and  $t_U$  is the aperture uncertainty time. For a bipolar ±10V signal and a maximum uncertainty error of 1/2LSB in a 12-bit system, the MFE is equal to 1/2LSB ÷  $V_{PEAK} = 2.44$ mV ÷ 10V = 0.000244V/V, since 1/2LSB = 2.44mV for a 20V full-scale range.

For the same system operating with a unipolar 0V to 10V signal, MFE would be 0.000122V/V.

*Charge Offset* (pedestal) is the output voltage change that results from charge transfer into the hold capacitor through stray capacitance when the Hold mode command is given. This charge appears as an offset voltage at the output, and in some sample/hold amplifiers may be a function of the input voltage.

Charge offset is specified for the SHC5320 using only the internal holding capacitor. When an external capacitor is added, charge offset is calculated as Charge Transfer (pC) divided by total hold capacitance. Charge Transfer is also specified for the SHC5320, and total hold capacitance is the sum of the internal hold capacitor value (100pF) and the external hold capacitor. Since charge transfer is not a function of analog input voltage for the SHC5320, this error may be removed by means of the offset adjustment capability of the amplifier.

*Droop Rate* is the change in output voltage over time during the Hold mode as a result of hold capacitor leakage, switch leakage, and bias current of the output amplifier. Droop rate varies with temperature and the quality of the external holding capacitor, if used. Careful circuit layout is also required to minimize droop.

*Drift Current* is the net leakage current affecting the hold capacitor during the Hold mode. With knowledge of the drift current, droop can be calculated as:

Droop

$$(V/s) = I_D(pA)/C_H(pF)$$

*Hold Mode Feedthrough* is the fraction of the input signal which appears at the output while in the Hold mode. It is primarily a function of switch capacitance, but may also be increased by poor layout practices.

*Hold Mode Settling Time* is the time required for the sample-to-hold transient to settle within a specified error band.

### **OPERATING INSTRUCTIONS**

### (Developed Around 14-Pin Package) OFFSET ADJUSTMENT

The offset should be adjusted with the input grounded. During the adjustment, the sample/hold should be switching continuously between the Sample and the Hold modes. The offset should then be adjusted to zero output for the periods when the amplifier is in the Hold mode. In this way, the effects of both amplifier offset and charge offset will be accounted for.

### SAMPLE/HOLD CONTROL

A TTL logic "0" applied to pin 14 switches the SHC5320 into the Sample (track) mode. In this mode, the device acts as an amplifier which exhibits normal operational amplifier behavior, with the relationship of output to input signal depending upon the circuit configuration selected (see the Installation section below). Application of a logic "1" to pin 14 switches the SHC5320 into the Hold mode, with the output voltage held constant at the value present when the hold command is given. Pin 14 presents less than one LSTTL load to the driving circuit throughout the full operating temperature range.

Teflon® Du Pont Corporation

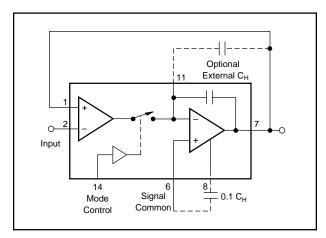

#### ADDITION OF AN EXTERNAL CAPACITOR

The SHC5320 contains an internal 100pF MOS holding capacitor, sufficient for most high-speed applications. If improved droop performance is desired (with increased acquisition time), additional capacitance may be added between pins 7 and 11. If an external holding capacitor  $C_H$  is used, then a noise-bandwidth capacitor with a value  $0.1C_H$  should be connected from pin 8 to ground. The exact value and type of this bandwidth capacitor are not critical.

Capacitors with high insulation resistance and low dielectric absorption, *such as Teflon® or polystyrene units*, should be used as storage elements (polystyrene should not be used above +85°C). Care should be taken in the printed circuit layout to minimize leakage currents from the capacitor to minimize droop errors.

The value of the external capacitor determines the droop, charge offset, and acquisition time of the sample/hold. Both droop and charge offset will vary linearly with total hold capacitance from the values given in the specification table for the internal 100pF capacitor. The behavior of acquisition time versus total hold capacitance is shown in the Typical Performance Curves.

### **OUTPUT PROTECTION**

In order to optimize high-frequency performance of this device, output protection is not included. This high frequency performance is mandatory for a good sample/hold, which must absorb high-frequency changes in load current when driving a successive-approximation A/D converter. Due to the lack of output protection, the output circuit will not tolerate an indefinite short to common, but a momentary short is permissible. The output should never be shorted to a supply.

### **INSTALLATION**

### (Developed Around 14-Pin Package) LAYOUT PRECAUTIONS

Since the holding capacitor is connected to virtual ground at one end (pin 11) and to a low-impedance voltage source at the other (pin 7), the SHC5320 does not require the use of guard rings and other careful layout techniques which are required by many sample/hold circuits. However, normal good layout practice should be observed, minimizing the possibility of leakage paths across the holding capacitor. As in all digital-analog circuits, analog signal lines on the circuit board should cross digital signal paths at right angles whenever possible.

### **GROUNDING AND BYPASSING**

Pin 6 (Reference Common) should be connected to the system analog signal common as close to the unit as possible. Likewise, pin 13 (Supply Common) should be connected to the system supply common. If the system design prevents running these two common lines separately, they should be connected together close to the unit, preferably to

a large ground plane surrounding the sample/hold. Bypass capacitors  $(0.01\mu\text{F} \text{ to } 0.1\mu\text{F} \text{ ceramic}$  in parallel with  $1\mu\text{F}$  to  $10\mu\text{F}$  tantalum) should be connected from each power supply terminal of the device to pin 13 (Supply Common).

#### OFFSET ADJUSTMENT

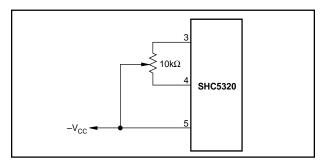

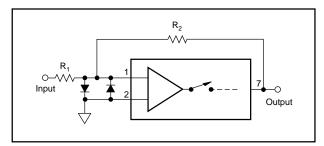

Offset adjustment capability may be achieved by connecting a  $10k\Omega$ , 10-turn potentiometer as illustrated in Figure 3.

FIGURE 3. Connection of Offset Adjustment Potentiometer.

### NONINVERTING MODE

The most common application of the SHC5320 will utilize the connection illustrated in Figure 4. In this mode of operation, the sample/hold will operate as a unity-gain noninverting amplifier when in the Sample mode, and the output signal will track the input. The high bandwidth of the SHC5320 and the large open-loop gain assure that gain error will be minimized.

FIGURE 4. Noninverting Unity-Gain Connections.

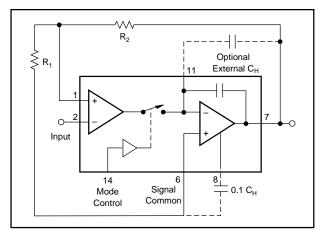

When sampling lower-amplitude signals, the SHC5320 may also be connected as a noninverting amplifier with gain, as illustrated in Figure 5. In this circuit the gain of the amplifier is equal to  $-R_2/R_1$  when sampling.

The Burr-Brown SHC5320 uses current sources to bias the internal amplifiers. This means that the bias of the amplifiers is not dependent on the common-mode voltage of the input signal. This makes the spurious free dynamic range in the non-inverting mode equal that of the inverting mode.

FIGURE 5. Noninverting Configuration with Gain = 1 +  $R_2/R_1$ .

FIGURE 6. Inverting Configuration with Gain =  $-(R_y/R_1)$ .

### **INVERTING MODE**

Unlike most sample/holds, the SHC5320 may also be connected to act as an inverting amplifier, as shown in Figure 6. For this configuration, the gain is equal to  $-R_2/R_1$ .

### INPUT OVERLOAD PROTECTION

It is possible that the input transconductance amplifier of the SHC5320 will saturate when the unit is in the Hold mode, due to a non-zero differential signal appearing between pins 1 and 2. This differential signal may be the result of a rapidly changing input signal or application of a new channel from an input multiplexer. When the input buffer is saturated in this fashion, acquisition time may be degraded because of the time required for the buffer to recover from saturation. In addition, the input buffer, which is designed to provide large amounts of charging current to the output integrator, may draw large amounts of supply current which may exceed 40mA peak in some applications. For these reasons, it is desirable to limit the differential voltage which may appear at the summing junction of the input buffer. Figures 7 and 8 illustrate possible methods of providing this voltage limitation for the inverting and noninverting configurations. The

diodes may be Schottky diodes, which will provide the fastest clamping action and lowest clamping voltage, but fast signal diodes such as IN914 will also work in most applications. In each configuration the value of  $R_1$  should be large enough to avoid excessive loading of the input signal source. Similarly,  $R_2$  should have a value of  $2k\Omega$  or greater to insure sufficient load current capability from the sample/hold. If the value of  $R_2$  becomes too large, however, the added capacitance of the diodes may change the sample/hold phase response enough to cause oscillation.

FIGURE 7. Input Overload Protection—Inverting Configuration.

FIGURE 8. Input Overload Protection—Noninverting Configuration.

### **APPLICATIONS**

### (Developed Around 14-Pin Package) SIGNAL DIGITIZATION

Sample/hold amplifiers are normally used to hold input voltages to an A/D converter constant during conversion. Digitizing errors result if the analog signal being digitized varies excessively during conversion.

For example, the Burr-Brown ADC80MAH-12 is a 12-bit successive-approximation converter with a  $25\mu s$  conversion time. To insure the accuracy of the output data, the analog input signal to the A/D converter must not change more than 1/2LSB during conversion.

The maximum rate of change of a sine wave of frequency, f, is dv/dt (max) =  $2\pi Af(V/s)$ . If one allows a 1/2LSB change (2.44mV) for a ±10V input swing to the A/D converter, the allowable input rate-of-change limit would be 2.44mV/25µs = 0.0976mV/µs. Thus the sampled sinusoidal signal frequency limit is

$f = (0.0976 \text{ x } 10^3)/2\pi A = 15.5/A \text{ (Hz)},$

where A is the peak amplitude of the sine wave. For a  $\pm 10V$

sine wave, this corresponds to a frequency of 1.6Hz, hardly acceptable for the majority of sampled data systems.

However, a sample/hold in front of the A/D converter "freezes" the converter's input signal whenever it is necessary to make a conversion. The rate-of-change limitation calculated above no longer exists. If a sample/hold has acquired an input signal and is tracking it, the sample/hold can be commanded to hold it at any instant in time. There is a short delay (aperture delay) between the time the hold command is asserted and the time the circuit actually holds. The hold command signal can usually be advanced in time (or delayed, in the case of negative effective aperture delay) to cause the amplifier to hold the signal actually desired.

Aperture uncertainty (also called aperture jitter) is also a key consideration. For the SHC5320 there is a 300ps period during which the signal should not change more than the amount allowed for aperture uncertainty in the system error budget, perhaps 1/2LSB for a 12-bit system. For a  $\pm 10V$  input range (1/2LSB = 2.44mV), the input signal rate of change limitation is 2.44mV/0.3ns = 8.13mV/ns. The equivalent input sine wave frequency is

$$f = 8.13 \times 10^{6}/2\pi A = 1.29/A$$

(MHz),

a factor of almost 84,000 higher than using the A/D alone.

However, there are other considerations. The resampling rate of an ADC80/SHC5320 combination is 26.5 $\mu$ s (25 $\mu$ s A/D) conversion time plus 1.5 $\mu$ s S/H acquisition time). Sampling a sine wave at the Nyquist rate, this permits a maximum input signal frequency of 37.7kHz. The above analysis assumes that the droop rate of the sample/hold is negligible—less than 1/2LSB during the conversion time and that the large signal bandwidth response of the sample/ hold causes negligible waveform distortion. Both of these assumptions are valid for the SHC5320 in this application.

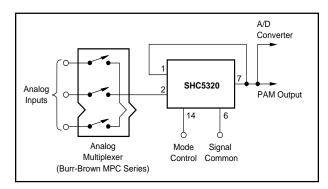

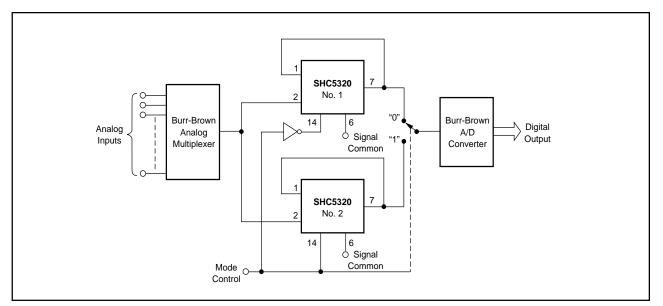

#### DATA ACQUISITION

The SHC5320 may be used to hold data for analog-to-digital conversion or may be used to provide pulse-amplitude modulation (PAM) data output (see Figures 9 and 10).

FIGURE 9. Typical Data Acquisition Configuration.

FIGURE 10. PAM Output.

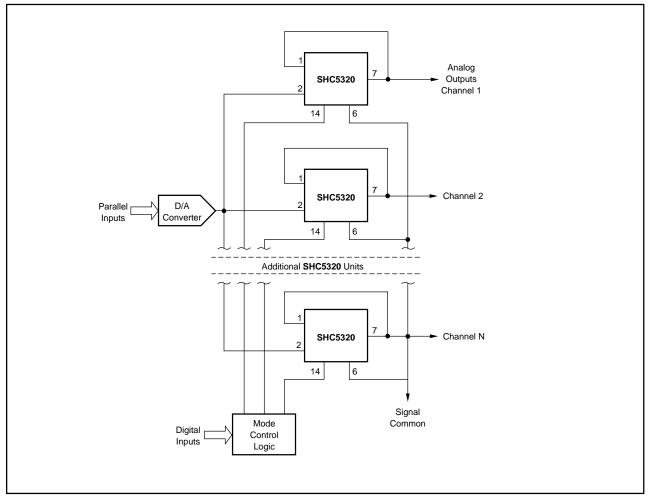

#### DATA DISTRIBUTION

The SHC5320 may be used to hold the output of a digitalto-analog converter and distribute several different analog voltages to different loads (see Figure 11).

#### **HIGH-SPEED DATA ACQUISITION**

The minimum sample time for one channel in a data acquisition system is usually considered to be the acquisition time of the sample/hold plus the conversion time of the A/D converter. If two or more sample/holds are used with a multiplexer (such as the Burr-Brown MPC800 or MPC801) as shown in Figure 12, the acquisition time of the sample/ hold can be virtually eliminated. While the first channel is in hold and switched into the A/D converter, the multiplexer may be addressed to the next channel. The second sample/ hold will have acquired this signal by the time the conversion is complete. Then, the sample/holds reverse roles and another channel is addressed. In low level systems an instrumentation amplifier (such as the Burr-Brown INA101) and a differential multiplexer (such as the Burr-Brown MPC509A or MPC507A) may be required in front of the sample/hold. The settling and acquisition times of the multiplexer, instrumentation amplifier, and sample/hold can be eliminated from the total conversion time as before by operating in this overlapped mode with the sample/holds.

FIGURE 11. Typical Data Distribution Configuration.

FIGURE 12. Typical Overlapped Sample/Hold Configuration.