# **DAC650**

# 12-Bit 500MHz DIGITAL-TO-ANALOG CONVERTER

# **FEATURES**

- 12-BIT RESOLUTION

- **500MHz UPDATE RATE**

- GUARANTEED SPURIOUS PERFORMANCE

- LOW GLITCH

- FAST SETTLING

- INTERNAL EDGE-TRIGGERED LATCH

- LASER TRIMMED ACCURACY

- INTERNAL REFERENCE

- CLEAN LOW-NOISE OUTPUT

### DESCRIPTION

The DAC650 is a high performance 12-bit digital to analog converter for high frequency waveform generation. It is complete with an internal low drift reference and edge-triggered data latch. The internal segmentation and latching provide for minimal output glitch energy.

The ECL compatibility provides for low digital noise at high update rates. The  $50\Omega$  output resistance and low output capacitance simplify transmission line design and filtering at the output. Complementary outputs are offered for increased performance while driving transformers or differential amplifiers.

The DAC650 combines precision thin film and bipolar technology with high speed gallium arsenide to create a high performance, cost effective solution for modern waveform synthesis systems.

## **APPLICATIONS**

- DIRECT DIGITAL SYNTHESIS

- ARBITRARY WAVEFORM GENERATION

- HIGH RESOLUTION GRAPHICS

- COMMUNICATIONS LOCAL OSCILLATORS Spread Spectrum Base Stations Digitally Tuned Receivers

- HIGH-SPEED MODEMS

International Airport Industrial Park

• Mailing Address: PO Box 11400

• Tucson, AZ 85734

• Street Address: 6730 S. Tucson Blvd.

• Tucson, AZ 85706

Tel: (520) 746-1111

• Twx: 910-952-1111

• Cable: BBRCORP

• Telex: 066-6491

• FAX: (520) 889-1510

• Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

### **ELECTRICAL**

Over full specified temperature range, using the internal +10V reference and rated supplies, unless otherwise noted.

|                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                        |                                                      | DAC650JL                                                           | _                                                                            |                                  | DAC650KL                                                 |                                            |                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------|--------------------------------------------|----------------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                   | CONDITIONS                                                                                                                                                                                                                             | MIN                                                  | TYP                                                                | MAX                                                                          | MIN                              | TYP                                                      | MAX                                        | UNITS                                              |

| TEMPERATURE RANGE Specification: DAC650JL, KL(1) $\theta_{\rm CA}$ $\theta_{\rm JC}$                                                                                                                                                                                                                                                                                        | Ambient                                                                                                                                                                                                                                | 0                                                    | 27<br>13                                                           | +70                                                                          | *                                | *                                                        | *                                          | °C<br>°C/W<br>°C/W                                 |

| DIGITAL INPUTS Logic Resolution ECL Logic Input Levels <sup>(2)</sup> : V <sub>IL</sub> I <sub>IL</sub> V <sub>IH</sub> I <sub>IH</sub> Logic Threshold Voltage  DIGITAL TIMING Input Data Rate CLK Pulse Width Low Set-Up Time Hold Time (Referred to CLK) Propagation Delay                                                                                               | 12 Parallel Input Lines  Logic "0"  Logic "1"                                                                                                                                                                                          | -1.475<br>-1.115<br>-1.2<br>DC<br>1.0<br>2.0<br>-500 | -1.8<br>1.0<br>-0.8<br>1.0<br>-1.3                                 | ECL Co<br>12<br>-2<br>10<br>-0.6<br>10<br>-1.4                               | mpatible  *  *  *  *  *  *       | * * * * * * * * * * * * * * * * * * * *                  | :                                          | Bits V                                             |

| ANALOG OUTPUT Bipolar Output Current Bipolar Output Voltage Output Resistance Output Resistance Drift Output Capacitance                                                                                                                                                                                                                                                    | $\begin{array}{c} R_L = 0\Omega \\ R_L = \infty \\ V_{OUT}, V_{OUT} \text{ to Ground} \end{array}$                                                                                                                                     | 49                                                   | ±20<br>±1.0<br>50<br>50                                            | 51                                                                           | *                                | * * * * *                                                | *                                          | mA<br>V<br>Ω<br>ppm/°C<br>pF                       |

| TRANSFER CHARACTERISTICS Integral Linearity Error Differential Linearity Error Monotonicity Bipolar Gain Error Bipolar Offset Error                                                                                                                                                                                                                                         | Best Fit Straight Line<br>+25°C<br>Over Temperature<br>Output Voltage, R <sub>L</sub> = ∞<br>Output Voltage, R <sub>L</sub> = ∞                                                                                                        |                                                      | ±0.018<br>±0.018<br>±0.018<br>Typical<br>±0.5<br>±0.5              | ±0.036<br>±0.036<br>±0.036<br>±1.0<br>±1.0                                   |                                  | ±0.012<br>±0.08<br>±0.012<br>Guaranteed<br>±0.5<br>±0.25 | ±0.024<br>±0.024<br>±0.024<br>±1.0<br>±0.5 | %FSR<br>%FSR<br>%FSR<br>%FSR<br>%FSR               |

| TIME DOMAIN PERFORMANCE Glitch Energy Output Rise Time Output Fall Time Settling Time <sup>(3)</sup> : ±0.1%FSR                                                                                                                                                                                                                                                             | Major Carry<br>10% to 90%<br>90% to 10%<br>Major Carry, 1LSB Change                                                                                                                                                                    |                                                      | 20<br>300<br>350<br>2.0                                            |                                                                              |                                  | * * *                                                    |                                            | pV-s<br>ps<br>ps<br>ns                             |

| REFERENCES  V <sub>BB</sub> Input Range (Pin 1)  V <sub>BB INT</sub> Reference (Pin 68)  V <sub>BB EXT</sub> Tracking Reference (Pin 67) Internal Reference Voltage (Ref Out) Ref in Resistance Ref in Operating Voltage Range                                                                                                                                              | ECL <sub>HI IN</sub> = -0.8V, ECL <sub>LO IN</sub> = -1.8V                                                                                                                                                                             | -1.4<br>-1.4<br>-1.4<br>9.95                         | -1.3<br>-1.3<br>-1.3<br>10<br>4950<br>10.0                         | -1.2<br>-1.2<br>-1.2<br>10.05                                                | * * * *                          | * * * * *                                                | * * * *                                    | V<br>V<br>V<br>V<br>Ω<br>V                         |

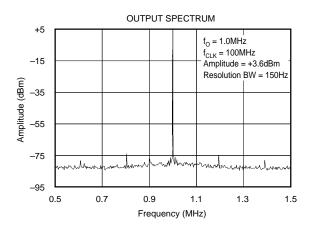

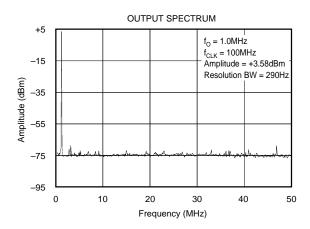

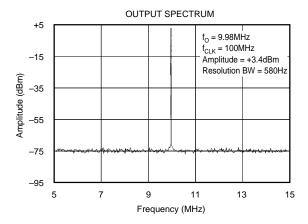

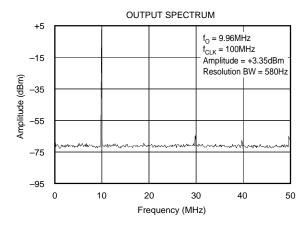

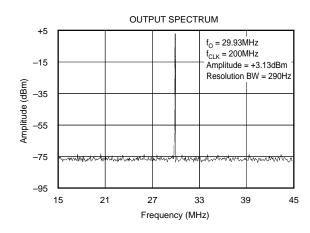

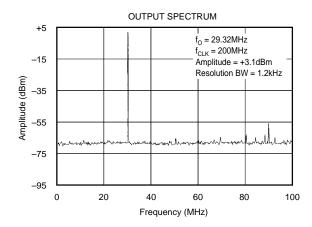

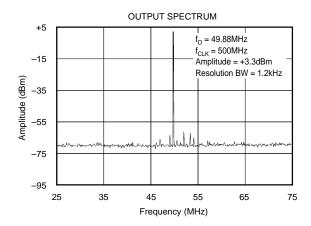

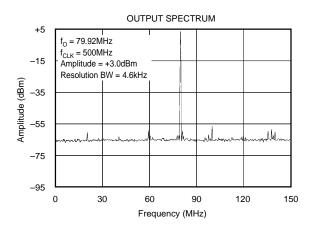

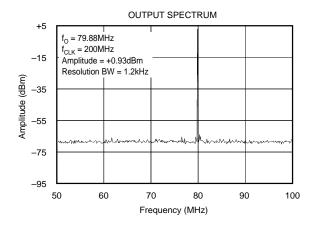

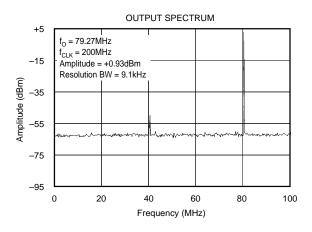

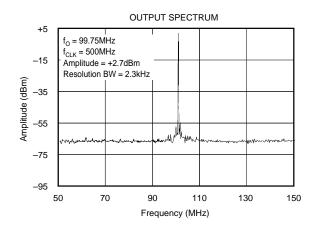

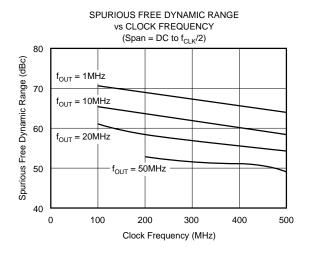

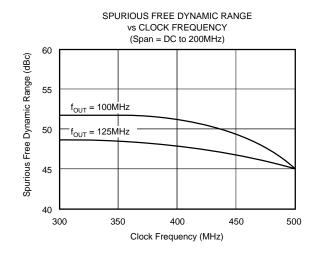

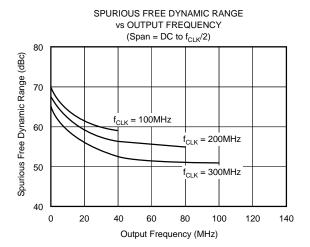

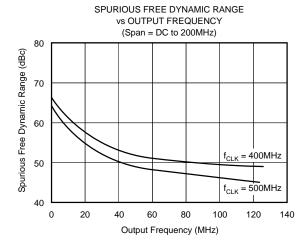

| DYNAMIC PERFORMANCE Spurious Free Dynamic Range(4) f <sub>O</sub> = 1MHz, f <sub>CLK</sub> = 100MHz f <sub>O</sub> = 10MHz, f <sub>CLK</sub> = 100MHz f <sub>O</sub> = 30MHz, f <sub>CLK</sub> = 200MHz f <sub>O</sub> = 80MHz, f <sub>CLK</sub> = 200MHz f <sub>O</sub> = 80MHz, f <sub>CLK</sub> = 500MHz f <sub>O</sub> = 100MHz, f <sub>CLK</sub> = 500MHz Output Noise | +25°C, Span = DC to $f_{CLK}/2$<br>+25°C, Span = DC to 150MHz<br>+25°C, Span = 50MHz to 150MHz<br>Full Scale Sine Wave Output | 65<br>59<br>50<br>47<br>49<br>51                     | 68<br>63<br>52<br>50<br>55<br>56<br>1.0                            |                                                                              | 68<br>62<br>53<br>50<br>52<br>54 | 70<br>65<br>56<br>52<br>58<br>59                         |                                            | dBc <sup>(5)</sup> dBc dBc dBc dBc dBc dBc dBc dBc |

| POWER SUPPLIES  Supply Voltages: +V <sub>CC</sub> -V <sub>CC</sub> +V <sub>DD1</sub> -V <sub>DD2</sub> Power Supply Rejection  Supply Currents: +I <sub>CC</sub> -I <sub>CC</sub> +I <sub>DD1</sub> -I <sub>DD2</sub> Power Consumption                                                                                                                                     | Operating, T <sub>MIN</sub> to T <sub>MAX</sub> All Supplies, ±5% Change Operating  Operating                                                                                                                                          | +14.25<br>-15.75<br>+4.75<br>-5.46                   | +15<br>-15<br>+5<br>-5.2<br>0.05<br>10<br>-47<br>53<br>-191<br>2.0 | +15.75<br>-14.25<br>+5.25<br>-4.94<br>0.08<br>13<br>-50<br>57<br>-245<br>2.6 | * * *                            | * * * * * * * * * * * * * * * * * * * *                  | * * * * * * * * * * * * * * * * * * * *    | V<br>V<br>V<br>V/%<br>mA<br>mA<br>mA<br>MA         |

NOTE: (1) Extended temperature range devices are available, inquire. (2) V<sub>BBIN</sub> (Pin 1) connected to V<sub>BB INT</sub> (Pin 68). (3) Settling time is influenced by load due to fast edge speeds. Use good transmission line techniques for best results. (4) Spurious Free Dynamic Range includes both harmonic and non-harmonic related spurs in the bandwidth indicated. (5) dBc is "dB referred to the fundamental amplitude."

### ORDERING INFORMATION

| MODEL        | DESCRIPTION                    | TEMPERATURE<br>RANGE (AMBIENT) |

|--------------|--------------------------------|--------------------------------|

| DAC650JL, KL | 68-Pin Ceramic, Gullwing Leads | 0°C to +70°C                   |

### **ABSOLUTE MAXIMUM RATINGS**

| ±V <sub>CC</sub>                             | ±18V               |

|----------------------------------------------|--------------------|

| Logic Input                                  | +0.5V to -5.5V     |

| Case Temperature                             |                    |

| Junction Temperature                         | +150°C             |

| Storage Temperature                          | 55°C to +125°C     |

| Lead Temperature (soldering, 10s)            | +300°C             |

| Stresses above these ratings may permanently | damage the device. |

### **PACKAGE INFORMATION**

| MODEL        | PACKAGE                 | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|--------------|-------------------------|------------------------------------------|

| DAC650JL, KL | 68-Pin Ceramic Gullwing | 256                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

Electrostatic discharge can cause damage ranging from performance degradation to complete device failure. Burr-Brown Corporation recommends that this integrated circuit be handled and stored using appropriate ESD protection methods.

### **PIN DEFINITIONS**

| PIN NO | DESIGNATION        | DESCRIPTION                                | PIN NO | DESIGNATION          | DESCRIPTION                                                  |

|--------|--------------------|--------------------------------------------|--------|----------------------|--------------------------------------------------------------|

| 1      | V <sub>BB</sub>    | Sets Logic Threshold for Bits 1-12         | 35     | AGND                 | Ground for Analog Output Current                             |

| 2      | Bit 1              | MSB                                        | 36     | AGND                 |                                                              |

| 3      | Bit 2              |                                            | 37     | AGND                 |                                                              |

| 4      | Bit 3              |                                            | 38     | AGND                 |                                                              |

| 5      | Bit 4              |                                            | 39     | V <sub>OUT</sub>     | Complementary Output Voltage                                 |

| 6      | Bit 5              |                                            | 40     | V <sub>OUT</sub>     |                                                              |

| 7      | Bit 6              |                                            | 41     | V <sub>OUT</sub>     |                                                              |

| 8      | Bit 7              |                                            | 42     | AGND                 |                                                              |

| 9      | Bit 8              |                                            | 43     | AGND                 |                                                              |

| 10     | Bit 9              |                                            | 44     | AGND                 |                                                              |

| 11     | Bit 10             |                                            | 45     | V <sub>OUT</sub>     | Output Voltage                                               |

| 12     | Bit 11             |                                            | 46     | V <sub>OUT</sub>     |                                                              |

| 13     | Bit 12             | LSB                                        | 47     | V <sub>OUT</sub>     |                                                              |

| 14     | V <sub>EE</sub>    | Logic Power (–5.2V Nominal) <sup>(1)</sup> | 48     | AGND                 |                                                              |

| 15     | V <sub>EE</sub>    |                                            | 49     | AGND                 |                                                              |

| 16     | CLK                | Clock                                      | 50     | AGND                 |                                                              |

| 17     | CLK <sub>NOT</sub> | Not Clock                                  | 51     | AGND                 |                                                              |

| 18     | DNC                | Do Not Connect                             | 52     | -15V                 | -15V Supply                                                  |

| 19     | V <sub>EE</sub>    |                                            | 53     | -15V                 |                                                              |

| 20     | V <sub>EE</sub>    |                                            | 54     | PWR GND              | Ground for Analog Supplies                                   |

| 21     | V <sub>EE</sub>    |                                            | 55     | +5V                  | +5V Supply                                                   |

| 22     | V <sub>EE</sub>    |                                            | 56     | +5V                  | +5V Supply                                                   |

| 23     | V <sub>EE</sub>    |                                            | 57     | V <sub>OS</sub> ADJ  | Offset Adjust                                                |

| 24     | V <sub>EE</sub>    |                                            | 58     | PWR GND              | Ground for Analog Supplies                                   |

| 25     | V <sub>EE</sub>    |                                            | 59     | Ref <sub>ADJ</sub>   | Reference Out Adjust                                         |

| 26     | V <sub>EE</sub>    |                                            | 60     | Ref <sub>OUT</sub>   | Reference Out (+10V, Buffered)                               |

| 27     | DGND               | Ground for Logic                           | 61     | Ref <sub>IN</sub>    | Reference In (4.950kΩ)                                       |

| 28     | DGND               |                                            | 62     | +15V                 | +15V Supply                                                  |

| 29     | DGND               |                                            | 63     | PWR GND              | Ground for Analog Supplies                                   |

| 30     | DGND               |                                            | 64     | -5.2V Analog         | Analog Power (-5.2V Nominal)(1)                              |

| 31     | DGND               |                                            | 65     | ECL LO <sub>IN</sub> | External ECL LOW input (optional)                            |

| 32     | DGND               |                                            | 66     | ECL HI <sub>IN</sub> | External ECL HI input (optional)                             |

| 33     | DGND               |                                            | 67     | V <sub>BBEXT</sub>   | The buffered mean of LO <sub>EXT</sub> and HI <sub>EXT</sub> |

| 34     | DGND               |                                            | 68     | V <sub>BBINT</sub>   | Internally generated –1.3V reference                         |

NOTE: (1) Both the -5.2V Logic and -5.2V analog pins should be powered from a common supply.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

# **TYPICAL PERFORMANCE CURVES**

$T_A = +25^{\circ}C$  unless otherwise noted.

# **TYPICAL PERFORMANCE CURVES (CONT)**

$T_A = +25$ °C unless otherwise noted.

# **TYPICAL PERFORMANCE CURVES (CONT)**

$T_A = +25$ °C unless otherwise noted.

### TECHNOLOGY OVERVIEW

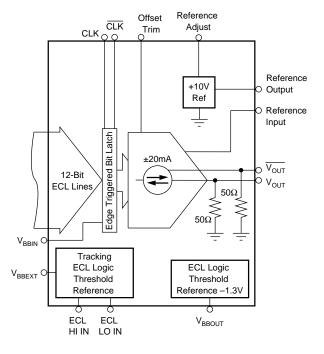

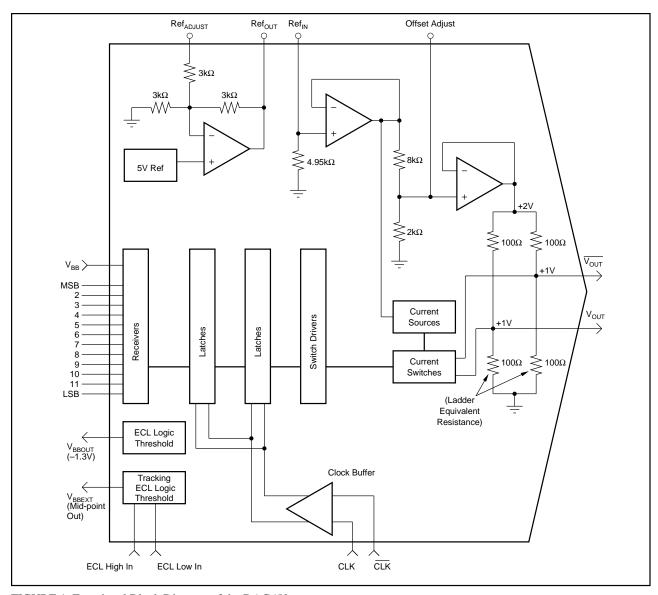

The DAC650 uses a unique design approach to achieve very fast settling time and high resolution. This mixed-technology design uses two active chips: one gallium arsenide and the other silicon.

The GaAs MESFET die is used for those circuits which determine speed. This includes the latches, data decoders, and current switches. A silicon die with thin film is used for those circuits which determine accuracy, such as the precision references and current sources. The precision R-2R resistor ladders are laser trimmed to further increase the accuracy of the DAC650. A block diagram of the DAC650 is shown in Figure 1.

## THEORY OF OPERATION

The DAC650 employs a familiar architecture where input bits switch on the appropriate current sources. Bits 1-3 are decoded into 7 segments before the first set of latches. A similar delay is given for the 9 least significant bits to minimize data skew. The edge triggered master-slave latches are driven by an internal clock buffer. This buffer placement has matched the clock lines to each of the 32 latches, thus minimizing output glitch energy.

There are 7 current sources for bits 1 to 3. Current sources for bits 4-8 are scaled down in binary fashion. These current sources are switched directly to the output of the R-2R ladder. Bits 9-12 are fed to the laser trimmed R-2R ladder for proper scale-down. The segmentation further minimizes output glitch which can cause spectral degradation.

The output current sees  $50\Omega$  of output impedance from the equivalent resistance of a R-2R ladder (100 $\Omega$ ) in parallel with  $100\Omega$  (Figure 1). With all of the current sources off, the output voltage is at +1V. With all current sources on (-40mA), the output voltage is at -1V. There is also a complementary  $\overline{V_{OUT}}$  output that allows for a differential output signals. The full scale complementary outputs (VOUT and  $\overline{V_{OUT}}$ ) can be simply modeled as  $\pm 20$ mA in parallel with  $50\Omega$ . This gives an output swing of 1Vp-p with an external  $50\Omega$  load.

#### REFERENCE/GAIN ADJUSTMENT

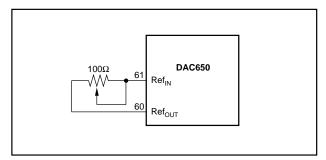

A precision +10V reference is included in the DAC650. A  $50\Omega$  resistor should be connected between REF<sub>IN</sub> and REF<sub>OUT</sub> for the specified unadjusted gain. This internal reference has been laser trimmed to minimize offset and gain drift. Alternatively, an external reference may be used. Multiple DACs may be run from one master reference by connecting a  $50\Omega$ resistor from each REF<sub>IN</sub> to the master REF<sub>OUT</sub>. A  $100\Omega$ potentiometer may be used in place of the  $50\Omega$  resistor in order to provide a ±1% gain adjustment range (Figure 2).

A wider adjustment range of ±20% may be achieved by connecting a  $10k\Omega$  potentiometer from REF<sub>OUT</sub> to ground, with the wiper connected to the REFADI pin. Adjusting the output to more than 40mA full scale may degrade high

frequency performance and reliability due to higher current densities and operating temperature. Alternatively, lower full scale currents will affect operation because there is less current available to charge internal and external capacitances.

It should be noted that the gain adjust techniques mentioned above affect the current output and thus the voltage output from the DAC650. The voltage output will also be affected by an external load acting in parallel with the  $50\Omega$  output impedance.

### **OFFSET ADJUST**

The offset may be adjusted by connecting a potentiometer between the +5V supply and ground with the wiper connected to the offset adjust pin. The voltage on this pin with no connection is about 2V, with an equivalent impedance of  $1.6k\Omega$ . A  $10k\Omega$  potentiometer will give the necessary adjustment range. The full scale range of the DAC output may be offset so it is not symmetrical around zero, but the full scale range must also be adjusted so that the output swing does not exceed ±1V. Connecting the offset adjust pin to ground gives a unipolar output of 0 to -2V (with no load) or 0 to -1V (with a  $50\Omega$  load). This also reduces the current requirements for the +5V supply by 20mA.

### DIGITAL INPUTS, LOGIC THRESHOLDS, and TERMINATION

The input logic levels and clock levels are ECL compatible. The data inputs are single ended ECL and the clock input is differential.

The internal impedance of the data and clock inputs is a high impedance (FET gate), and is clamped to the digital supply and ground to protect against ESD damage. ESD precautions should still be used when handling the DAC650.

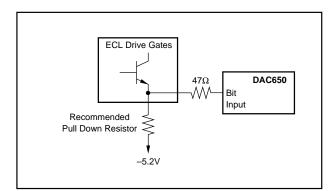

The inputs will most likely be driven by high-speed ECL gate outputs. These outputs should be terminated using standard high-speed transmission line techniques. Consult an ECL handbook for proper methods of termination.

Termination resistors should not be connected to the analog ground plane close to the DAC650. The fast changing digital bit currents will cause noise in the analog ground plane under this layout scheme. These fast changing digital currents should be steered away from the sensitive DAC650 analog ground plane. For speeds of up to 256MHz, series termination with  $47\Omega$  resistors will be adequate (Figure 3). This termination technique will greatly lessen the issue of termination currents coupling into the analog ground plane. Above 256MHz, parallel termination of the transmission line at the package pin may be required for clean digital

The input data threshold level is set by connecting the appropriate voltage (-1.2V to -1.4V) to pin 1. The actual level may be provided 3 ways:

(1) The user connects the DAC650's internal -1.3V threshold reference directly to pin 1. This simple connection provides excellent noise margins for ECL levels.

FIGURE 1. Functional Block Diagram of the DAC650.

FIGURE 2. Using a Potentiometer for  $\pm 1\%$  Gain Adjust.

FIGURE 3. Series Bit Termination.

- (2) An external V<sub>BB</sub> system reference is applied to pin 1. This technique may allow data threshold levels to track the system over supply and temperature variations.

- (3) The internal tracking ECL threshold reference (pin 67) is applied to pin 1. The output of the tracking ECL threshold reference is simply the average of two externally applied levels. These levels are a system logic low (pin 65) and system logic high (pin 66). This technique may provide increased noise margin for systems with levels slightly different from ECL. Leave pins 65-67 open if this option is not used.

### **TIMING**

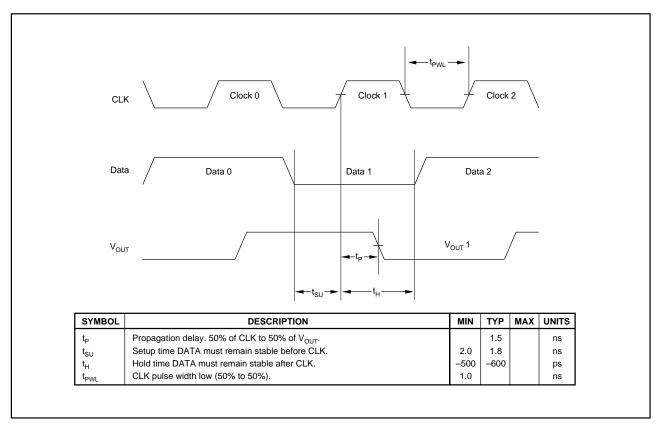

The DAC650 has an internal edge triggered latch. The output changes on the positive edge of CLK. This master-slave latching will assure that the 12 bits will arrive at the bit switches with a minimum of data skew. Data must have adequate setup and hold time for proper operation (refer to Figure 4). Note that the Hold time is negative. Therefore the data may change before the rising edge of clock and still be valid.

The DAC650 has a differential ECL clock input. This clock input can also be driven by a single-ended clock if desired by tying the  $\overline{\text{CLK}}$  input to an external voltage of -1.3V. Using a true differential clock provides much improved digital feedthrough immunity, however.

#### DATA IN/VOUT CORRESPONDENCE

The each full scale output of the DAC650 may be modeled as either  $\pm 20$ mA current source in parallel with  $50\Omega$  or a  $\pm 1$ V voltage source in series with  $50\Omega$ . The nominal current and voltage bit weights are given in Table I and the input code vs output voltage relationships are given in Table II.

Transmission line techniques at the output are also recommended to minimize ringing and glitching. Ideally, both of the outputs should see the same termination, including any delay between the DAC650 and the load.

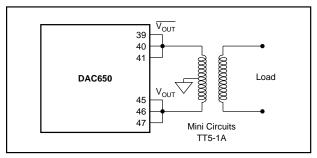

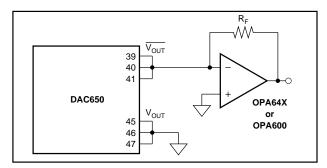

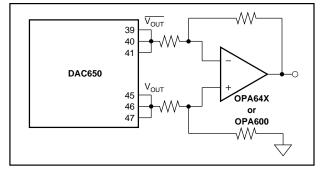

Since the outputs  $V_{OUT}$  and  $\overline{V_{OUT}}$  are equal in magnitude but opposite in sign, they are ideal for driving RF transformers (Figures 5). The primary may be connected between the two outputs. The secondary may be floating or referenced to ground. This results in a 2X signal power and some cancellation of clock feedthrough, glitching, and distortion. Figures 6 and 7 give recommended output amplifiers.

FIGURE 4. Timing Diagram for the DAC650.

If only one output is used, the unused output should be terminated identically. If the terminations cannot be identical and the unused output must be unterminated, the termination for the used output should be as close as possible to the DAC650.

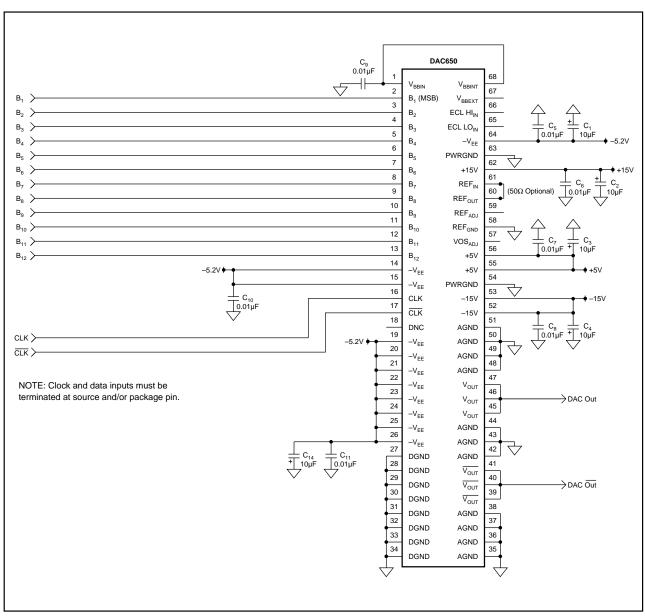

### LAYOUT AND POWER SUPPLIES

A multilayer PC board with a solid ground and power planes is recommended. An example of a typical circuit configuration is given in Figures 8. The DAC650 has multiple ground pins to minimize pin impedances. All of the ground pins (analog and digital both) should be connected directly to the analog ground plane at the DAC650.

Wide busses for the power paths are recommended as good general practice. There are several internal power supply bypass capacitors, but external bypassing is still recom-

| ВІТ      | VOLTAGE (No External Load) | CURRENT  |

|----------|----------------------------|----------|

| 1        | 1V                         | 20mA     |

| 2        | .5V                        | 10mA     |

| 3        | 0.25V                      | 5mA      |

| 4        | 0.125V                     | 2.5mA    |

| 5        | 62.5mV                     | 1.25mA   |

| 6        | 31.25mV                    | 625μΑ    |

| 7        | 15.625mV                   | 312.5μΑ  |

| 8        | 7.8125mV                   | 156.25μΑ |

| 9        | 3.9063mV                   | 78.125μA |

| 10       | 1.9531mV                   | 39.06μΑ  |

| 11       | 976μV                      | 19.53μΑ  |

| 12 (LSB) | 488μV                      | 9.76μΑ   |

TABLE I. Nominal Bit Weight Values.

| INPUT BITS                 | OUTPUT VOLTAGES                    |

|----------------------------|------------------------------------|

| 1 2 3 4 5 6 7 8 9 10 11 12 | V <sub>OUT</sub> NV <sub>OUT</sub> |

| 0 0 0 0 0 0 0 0 0 0 0 0    | +1.000                             |

| 000000000001               | +1 – 488μV –1 + 976μV              |

| 000000000010               | +1 − 976μV       −1 + 1.464mV      |

| •                          |                                    |

| • 0 1 0 0 0 0 0 0 0 0 0    | 0.50                               |

| 1000000000000              | 0.000 +488μV                       |

| 1 1 1 1 1 1 1 1 1 1 1 1    | –1 + 488μV +1.000                  |

TABLE II. Input Code vs Output Voltage Relationships.

FIGURE 5. Using an RF Transformer at the Output of the DAC650. Filtering the Outputs Before the Transformer Improves the Performance in Some Applications.

mended. A  $10\mu F$  tantalum capacitor in parallel with a  $0.01\mu F$  chip capacitor will be sufficient in most applications. Pin 64, Analog  $V_{EE}$ , should be connected to the same supply as the digital  $V_{FE}$  pins (-5.2V).

### **MAXIMIZING PERFORMANCE**

The DAC650 has been designed to give a very clean analog output with minimal noise, overshoot, and ringing. In addition to optimizing the layout and ground of the DAC650, there are other important issues to consider when optimizing the performance of this DAC in various AC applications.

The DAC650 includes an internal  $50\Omega$  output impedance to simplify output interfacing to a  $50\Omega$  load. Because some loads may be a complex impedance, care must be taken to match the output impedance with the load. Mismatching of impedances can cause reflections which will affect the measured AC performance parameters such as settling time, harmonic distortion, rise/fall times, etc. Often complex impedances can be matched by placing a variable 3 to 10pF capacitor at the output of the DAC to ground. Also, probing the output can present a complex impedance.

The typical performance curves of Spurious Free Dynamic Range vs various combinations of clock rate and/or input frequency should give a general idea of the spectral performance of the DAC under system specific clock and output frequencies. We have defined Spurious Free Dynamic Range as any harmonic or non-harmonic spurs in the indicated bandwidth . In phase lock loop applications, the harmonics often fall outside the loop bandwidth of the PLL. In these cases, as well as cases where the output is filtered, Spurious

FIGURE 6. A High Speed Single Ended Amplifier at the Output. The Gain is  $-R_{\rm r}/50\Omega$ .

FIGURE 7. A High Speed Differential Amplifier at the Output.

Free Dynamic Range will generally be much better due to the harmonics falling outside the passband. Even with a bandpass filter, updating the DAC at greater than 4 times per cycle will (1) minimize the 2nd and 3rd harmonic magnitudes by having the output slew excessively between any successive clock and (2) will keep the  $(f_{CLK}-2f_O)$  spur and other even order spurs from folding back close to the fundamental under the condition  $f_{OUT}=1/3f_{CLK}$  and (3) will keep the  $(f_{CLK}-3f_O)$  spur and other spurs from folding back close to the fundamental under the condition  $f_{OUT}=1/4f_{CLK}$ . Making use of the high update rate of the DAC650 helps to lessen the problems of harmonics "folding back" into the passband.

#### **EVALUATION BOARD**

The high frequency signals used in operating the DAC650 can cause difficult layout problems. It is especially difficult to build a high-performance prototype board using the DAC650. It is recommended that an evaluation fixture be used for prototyping. An evaluation fixture includes a DAC650 soldered to the PC board. Both grades are available for the evaluation fixture.

### **ORDERING INFORMATION**

| MODEL                          | DESCRIPTION                                                                        |

|--------------------------------|------------------------------------------------------------------------------------|

| DEM-DAC650J-E<br>DEM-DAC650K-E | Evaluation Board with DAC650JL Attached<br>Evaluation Board with DAC650KL Attached |

| DEM-DAC650 PDS                 | Data Sheet for DAC650 Evaluation Board                                             |

FIGURE 8. Typical DAC650 Connection Diagram.