# ADS7803

# Autocalibrating, 4-Channel, 12-Bit ANALOG-TO-DIGITAL CONVERTER

### **FEATURES**

- LOW POWER: 10mW plus Power Down

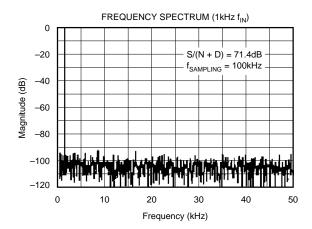

- SIGNAL-TO-(NOISE + DISTORTION) RATIO OVER TEMPERATURE: 69dB min with  $f_{IN} = 1kHz$ 66dB min with  $f_{IN} = 50kHz$

- FAST CONVERSION TIME: 8.5µs Including Acquisition (117kHz Sampling Rate)

- DC PERFORMANCE OVER TEMPERATURE: ±3/4 LSB max Total Error ±1/4 LSB max Channel Mismatch

- FOUR-CHANNEL INPUT MULTIPLEXER

- SINGLE SUPPLY: +5V

- PIN COMPATIBLE WITH ADC7802

## DESCRIPTION

The ADS7803 is a monolithic CMOS 12-bit analogto-digital converter with internal sample/hold and fourchannel multiplexer. It is designed and tested for full dynamic performance with input signals to 50kHz. An autocalibration cycle guarantees a total unadjusted error within  $\pm 3/4$ LSB over the specified temperature range, eliminating the need for offset or gain adjustment. The 5V single-supply requirements and standard  $\overline{CS}$ ,  $\overline{RD}$ , and  $\overline{WR}$  control signals make the part easy to use in microprocessor applications. Conversion results are available in two bytes through an 8-bit three-state output bus.

The ADS7803 is available in a 28-pin plastic DIP and 28-lead PLCC, fully specified for operation over the industrial  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

## **SPECIFICATIONS**

#### ELECTRICAL

V<sub>A</sub> = V<sub>D</sub> = V<sub>REF</sub>+ = 5V ±5%; V<sub>REF</sub>- = AGND = DGND = 0V; CLK = 2MHz external, T<sub>A</sub> = -40°C to +85°C, after calibration at any temperature, unless otherwise specified.

|                                                                                                                                                                                                                                 |                                                                                                                                        | Α        |                                                                                         |                             |                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------|

| PARAMETER                                                                                                                                                                                                                       | CONDITIONS                                                                                                                             | MIN TYP  |                                                                                         | MAX                         | UNITS                                        |

| RESOLUTION                                                                                                                                                                                                                      |                                                                                                                                        |          |                                                                                         | 12                          | Bits                                         |

| ANALOG INPUT<br>Voltage Input Range<br>Input Capacitance                                                                                                                                                                        | V <sub>REF</sub> + = 5V, V <sub>REF</sub> - = 0V                                                                                       | 0        | 50                                                                                      | 5                           | V<br>pF                                      |

| On State Bias Current<br>Off State Bias Current                                                                                                                                                                                 | $T_A = +25^{\circ}C$<br>$T_A = -40^{\circ}C$ to $+85^{\circ}C$                                                                         |          | 100                                                                                     | 10<br>100                   | nA<br>nA<br>nA                               |

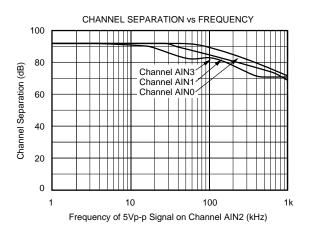

| On Resistance Multiplexer<br>Off Resistance Multiplexer                                                                                                                                                                         | 500Hz                                                                                                                                  |          | 2<br>10<br>92                                                                           | 100                         | kΩ<br>MΩ<br>dB                               |

| Channel Separation                                                                                                                                                                                                              | 500HZ                                                                                                                                  |          | 92                                                                                      |                             | uБ                                           |

| REFERENCE INPUT<br>For Specified Performance: V <sub>REF</sub> +<br>V <sub>REF</sub> -                                                                                                                                          | $V_{REF} + \leq V_A$                                                                                                                   |          | 5<br>0                                                                                  |                             | v<br>v                                       |

| For Derated Performance <sup>(1)</sup> : V <sub>REF</sub> +<br>V <sub>REF</sub><br>Input Reference Current                                                                                                                      | $V_{REF}$ + = 5V, $V_{REF}$ - = 0V                                                                                                     | 4.5<br>0 | 10                                                                                      | V <sub>A</sub><br>1<br>100  | ν<br>ν<br>μΑ                                 |

| THROUGHPUT TIMING                                                                                                                                                                                                               | VREFT = OV, VREFT = OV                                                                                                                 |          | 10                                                                                      | 100                         | μΛ                                           |

| Conversion Time With External Clock (Including<br>Multiplexer Settling Time and Acquisition Time)<br>With Internal Clock Using Recommended<br>Clock Components<br>Multiplexer Settling Time to 0.01%<br>Multiplexer Access Time | CLK = 2MHz<br>CLK = 1MHz<br>CLK = 500kHz<br>$T_A = +25^{\circ}C$<br>$T_A = -40^{\circ}C$ to +85^{\circ}C                               |          | 10<br>460                                                                               | 8.5<br>17<br>34<br>10<br>20 | μs<br>μs<br>μs<br>μs<br>μs<br>ns<br>ns       |

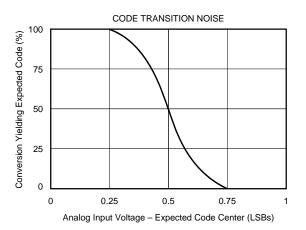

| DC ACCURACY<br>Total Error, All Channels <sup>(2)</sup><br>Differential Nonlinearity<br>No Missing Codes                                                                                                                        |                                                                                                                                        |          | ±1/2<br>±1/4<br>Guaranteed                                                              | ±3/4<br>±1/2                | LSB<br>LSB                                   |

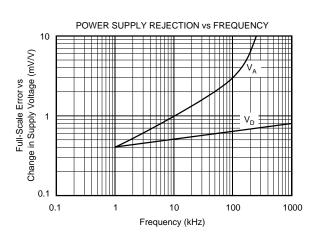

| Gain Error<br>Gain Error Drift<br>Offset Error<br>Offset Error Drift<br>Channel-to-Channel Mismatch<br>Power Supply Sensitivity                                                                                                 | All Channels<br>Between Calibration Cycles<br>All Channels<br>Between Calibration Cycles<br>$V_A = V_D = 4.75V$ to 5.25V               |          | $ \begin{array}{c} \pm 1/8 \\ \pm 0.2 \\ \pm 1/8 \\ \pm 0.2 \\ \pm 1/8 \\ \end{array} $ | ±1/4<br>±1/4<br>±1/4        | LSB<br>ppm/°C<br>LSB<br>ppm/°C<br>LSB<br>LSB |

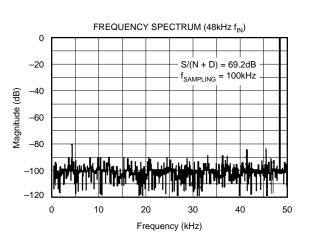

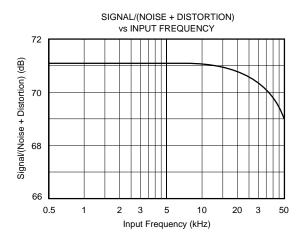

| AC ACCURACY<br>Signal-to-(Noise + Distortion) Ratio<br>Total Harmonic Distortion<br>Signal-to-Noise Ratio                                                                                                                       | $f_{IN} = 1 \text{ kHz}$ $f_{IN} = 50 \text{ kHz}$ $f_{IN} = 50 \text{ kHz}$ $f_{IN} = 50 \text{ kHz}$                                 | 69<br>66 | 71<br>69<br>75<br>70                                                                    |                             | dB<br>dB<br>dB<br>dB                         |

| Spurious Free Dynamic Range                                                                                                                                                                                                     | $f_{IN} = 1 \text{kHz}$<br>$f_{IN} = 50 \text{kHz}$                                                                                    |          | 90<br>82                                                                                |                             | dB<br>dB                                     |

| SAMPLING DYNAMICS<br>Full Power Bandwidth<br>Aperture Delay<br>Offset Error                                                                                                                                                     | -3dB<br>SFR D2 LOW<br>SRF D2 HIGH<br>SFR D2 LOW<br>SFR D2 HIGH, Internal Clock or<br>Sampling Command Synchronous<br>to External Clock |          | 4<br>2500<br>5<br>±1/8<br>±1/2                                                          | ±1/4<br>±1                  | MHz<br>ns<br>ns<br>LSB<br>LSB                |

|                                                                                                                                                                                                                                 | SFR D2 HIGH, Sampling Command<br>Asynchronous to External Clock                                                                        |          | ±4                                                                                      |                             | LSB                                          |

| DIGITAL INPUTS<br>All Pins Other Than CLK: V <sub>IL</sub><br>V <sub>IH</sub><br>Input Current                                                                                                                                  | $T_A = +25^{\circ}C, V_{IN} = 0 \text{ to } V_D$<br>$T_A = -40^{\circ}C \text{ to } +85^{\circ}C, V_{IN} = 0 \text{ to } V_D$          | 2.4      |                                                                                         | 0.8<br>1<br>10              | V<br>V<br>μΑ<br>μΑ                           |

| CLK Input: V <sub>IL</sub><br>V <sub>IH</sub><br>I <sub>IL</sub>                                                                                                                                                                | · · · · · · · · · · · · · · · · · · ·                                                                                                  | 3.5      |                                                                                         | 0.8                         | ν<br>V<br>μΑ                                 |

| ис<br>I <sub>IH</sub><br>I <sub>IH</sub>                                                                                                                                                                                        | Power Down Mode (D3 in SFR HIGH)                                                                                                       |          |                                                                                         | 1.5<br>100                  | mA<br>nA                                     |

NOTES: (1) For  $(V_{REF^+}) - (V_{REF^-})$  as low as 4.5V, the total error will typically not exceed ±1LSB. (2) After calibration cycle, without external adjustment. Includes gain (full scale) error, offset error, integral nonlinearity, differential nonlinearity, and drift.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

## **SPECIFICATIONS** (CONT)

#### ELECTRICAL

$V_A = V_D = V_{REF} + = 5V \pm 5\%$ ;  $V_{REF} - = AGND = DGND = 0V$ ; CLK = 2MHz external,  $T_A = -40^{\circ}C$  to +85°C, after calibration at any temperature, unless otherwise specified.

|                                                          |                                                                          | AD   |     |      |       |

|----------------------------------------------------------|--------------------------------------------------------------------------|------|-----|------|-------|

| PARAMETER                                                | CONDITIONS                                                               | MIN  | ТҮР | MAX  | UNITS |

| DIGITAL OUTPUTS                                          |                                                                          |      |     |      |       |

| V <sub>OL</sub>                                          | I <sub>SINK</sub> = 1.6mA                                                |      |     | 0.4  | V     |

| V <sub>OH</sub>                                          | $I_{SOURCE} = 200 \mu A$                                                 | 4    |     |      | V     |

| Leakage Current                                          | High-Z State, V <sub>OUT</sub> = 0V to V <sub>D</sub>                    |      |     | ±1   | μΑ    |

| Output Capacitance                                       | High-Z State                                                             | 4    |     | 15   | pF    |

| POWER SUPPLIES                                           |                                                                          |      |     |      |       |

| Supply Voltage for Specified Performance: V <sub>A</sub> |                                                                          | 4.75 | 5   | 5.25 | V     |

| V <sub>D</sub>                                           | $V_A \ge V_D$                                                            | 4.75 | 5   | 5.25 | V     |

| Supply Current: I <sub>A</sub>                           |                                                                          |      | 1   | 2.5  | mA    |

| l <sub>D</sub>                                           | Logic Input Pins HIGH or LOW                                             |      | 1   | 2    | mA    |

| Power Dissipation                                        | $\overline{WR} = \overline{RD} = \overline{CS} = \overline{BUSY} = HIGH$ |      | 10  |      | mW    |

| Power Down Mode                                          | See Table III                                                            |      | 50  |      | μW    |

| TEMPERATURE RANGE                                        |                                                                          |      |     |      |       |

| Specification                                            |                                                                          | -40  |     | +85  | °C    |

| Storage                                                  |                                                                          | -65  |     | +150 | °C    |

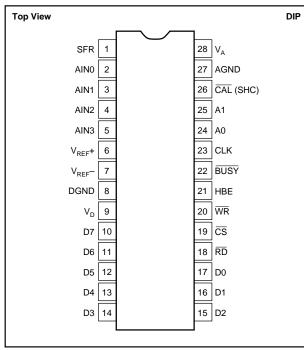

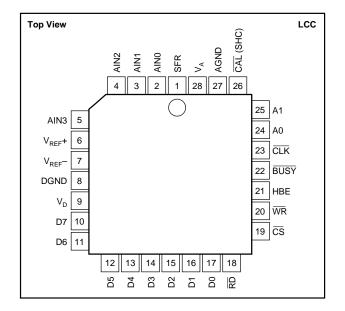

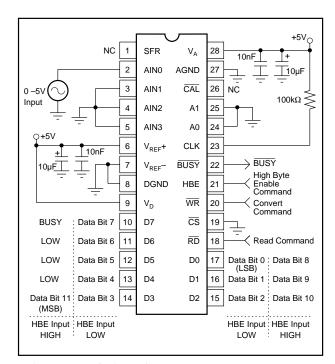

#### **PIN CONFIGURATIONS**

#### PACKAGE INFORMATION

| MODEL     | PACKAGE            | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|-----------|--------------------|------------------------------------------|

| ADC7803BN | 28-Pin LCC         | 251                                      |

| ADS7803BP | 28-Pin Plastic DIP | 215                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

#### **ORDERING INFORMATION**

| MODEL     | MINIMUM SIGNAL-TO-<br>(NOISE + DISTORTION)<br>RATIO, dB | MAXIMUM TOTAL<br>ERROR, LSB | SPECIFICATION<br>TEMPERATURE<br>RANGE |

|-----------|---------------------------------------------------------|-----------------------------|---------------------------------------|

| ADS7803BN | 69                                                      | ±3/4                        | -40°C to +85°C                        |

| ADS7803BP | 69                                                      | ±3/4                        | -40°C to +85°C                        |

#### **ABSOLUTE MAXIMUM RATINGS**

## **TYPICAL PERFORMANCE CURVES**

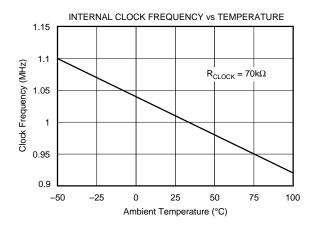

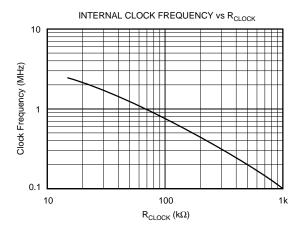

At  $V_A = V_D = V_{REF} + = 5V$ ,  $V_{REF} - = AGND = 0V$ ,  $T_A = +25^{\circ}C$ , dynamic performance based on 2048 point FFTs, unless otherwise noted.

## **TYPICAL PERFORMANCE CURVES (CONT)**

At  $V_A = V_D = V_{REF}$  = 5V,  $V_{REF}$  = AGND = 0V,  $T_A$  = +25°C, dynamic performance based on 2048 point FFTs , unless otherwise noted.

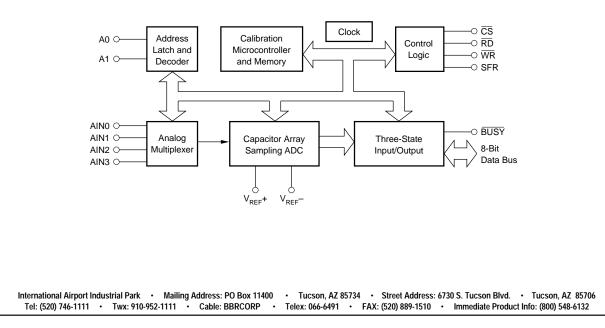

### THEORY OF OPERATION

ADS7803 uses the advantages of advanced CMOS technology (logic density, stable capacitors, precision analog switches, and low power consumption) to provide a precise 12-bit analog-to-digital converter with on-chip sampling and four-channel analog-input multiplexer.

The input stage consists of an analog multiplexer with an address latch to select from four input channels.

The converter stage consists of an advanced successive approximation architecture using charge redistribution on a capacitor network to digitize the input signal. A temperature-stabilized differential auto-zeroing circuit is used to minimize offset errors in the comparator.

Linearity errors in the binary weighted main capacitor network are corrected using a capacitor trim network and correction factors stored in on-chip memory. The correction terms are calculated by an on-chip microcontroller during a calibration cycle, initiated either by power-up or by applying an external calibration signal at any time. During conversion, the correct trim capacitors are switched into the main capacitor array as needed to correct the conversion accuracy. With all of the capacitors in both the main array and the trim array on the same chip, excellent stability is achieved, both over temperature and over time.

For flexibility, timing circuits include both an internal clock generator and an input for an external clock to synchronize with external systems. Standard control signals and threestate input/output registers simplify interfacing ADS7803 to most micro-controllers, microprocessors or digital storage systems.

The on-chip sampling provides excellent dynamic performance for input signals to 50kHz, and has a full-power –3dB bandwidth of 4MHz. Full control over sample-to-hold timing is available for applications where this is critical.

Finally, this performance is matched with the low-power advantages of CMOS structures to allow a typical power consumption of 10mW, with a  $50\mu$ W power down option.

### **OPERATION**

#### **BASIC OPERATION**

Figure 1 shows the simple circuit required to operate ADS7803 in the Transparent Mode, converting a single input channel. A convert command on pin 20 (WR) starts a conversion. Pin 22 (BUSY) will output a LOW during the conversion process (including sample acquisition and conversion), and rises only after the conversion is completed. The two bytes of output data can then be read using pin 18 (RD) and pin 21 (HBE).

FIGURE 1. Basic Operation.

#### **STARTING A CONVERSION**

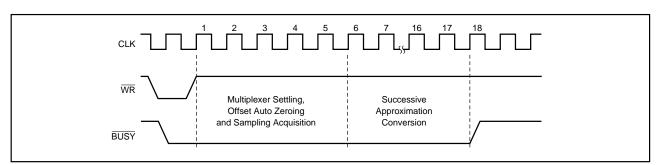

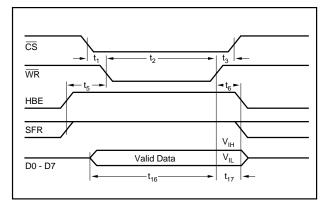

A conversion is initiated on the rising edge of the  $\overline{WR}$  input, with valid signals on A0, A1 and  $\overline{CS}$ . The selected input channel is sampled for five clock cycles. The successive approximation conversion takes place during clock cycles 6 through 17.

Figures 2 and 3 show the full conversion sequence and the timing to initiate a conversion.

A conversion can also be initiated by a rising edge on pin 26, if a HIGH has been written to D2 of the Special Function Register, as discussed below.

#### CALIBRATION

A calibration cycle is initiated automatically upon power-up (or after a power failure). Calibration can also be initiated by the user at any time by the rising edge of a minimum 100ns-wide LOW pulse on the  $\overline{CAL}$  pin (pin 26), or by setting D1 HIGH in the Special Function Register (see SFR section). A calibration command will initiate a calibration cycle, regardless of whether a conversion is in process. During a calibration cycle, convert commands are ignored.

Calibration takes 168 clock cycles, and a normal conversion (17 clock cycles) is added automatically. Thus, at the end of a calibration cycle, there is valid conversion data in the output registers. For maximum accuracy, the supplies and reference need to be stable during the calibration procedure. To ensure that supply voltages have settled and are stable, an internal timer provides a waiting period of 42,425 clock cycles between power-up/power-failure and the start of the calibration cycle.

#### **PIN ASSIGNMENTS**

| PIN #                            | NAME                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                | SFR                              | Special Function Register. When connected to a microprocessor address pin, allows access to special functions through D0 to D7. See the sections discussing the Special Function Register. If not used, connect to DGND. This pin has an internal pull-down.                                                                                                                                                                                                                                                |

| 2 to 5                           | AIN0 to AIN3                     | Analog inputs. Channel 0 to channel 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6                                | V <sub>REF</sub> +               | Positive voltage reference input. Normally +5V. Must be $\leq V_A$ .                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7                                | V <sub>REF</sub> -               | Negative voltage reference input. Normally 0V.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8                                | DGND                             | Digital ground. DGND = 0V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9                                | V <sub>D</sub>                   | Logic supply voltage. $V_D = +5V$ . Must be $\leq V_A$ and applied after $V_A$ .                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10 to 17<br>10                   | D0 to D7<br>D7                   | Data Bus Input/Output Pins. Normally used to read output data. See section on SFR (Special Function Register) for other uses.<br>When SFR is LOW, these function as follows:<br>Data Bit 7 if HBE is LOW; if HBE is HIGH, acts as converter status pin and is HIGH during conversion or calibration,                                                                                                                                                                                                        |

| 11<br>12<br>13<br>14<br>15<br>16 | D6<br>D5<br>D4<br>D3<br>D2<br>D1 | goes LOW after the conversion is completed. (Acts as an inverted BUSY).<br>Data Bit 6 if HBE is LOW; LOW if HBE is HIGH.<br>Data Bit 5 if HBE is LOW; LOW if HBE is HIGH.<br>Data Bit 4 if HBE is LOW; DOW if HBE is HIGH.<br>Data Bit 3 if HBE is LOW; Data Bit 11 (MSB) if HBE is HIGH.<br>Data Bit 2 if HBE is LOW; Data Bit 10 if HBE is HIGH.<br>Data Bit 1 if HBE is LOW; Data Bit 9 if HBE is HIGH.                                                                                                  |

| 17                               | D0                               | Data Bit 0 (LSB) if HBE is LOW; Data Bit 8 if HBE is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18                               | RD                               | Read Input. Active LOW; used to read the data outputs in combination with $\overline{CS}$ and HBE.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 19                               | CS                               | Chip Select Input. Active LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 20                               | WR                               | Write Input. Active LOW; used to start a new conversion and to select an analog channel via address inputs A0 and A1 in combination with $\overline{\text{CS}}$ . The minimum $\overline{\text{WR}}$ pulse LOW width is 100ns.                                                                                                                                                                                                                                                                              |

| 21                               | HBE                              | High Byte Enable. Used to select high or low data output byte in combination with CS and RD, or to select SFR.                                                                                                                                                                                                                                                                                                                                                                                              |

| 22                               | BUSY                             | BUSY is LOW during conversion or calibration. BUSY goes HIGH after the conversion is completed.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 23                               | CLK                              | Clock Input. For internal or external clock operation. For external clock operation, connect pin 23 to a 74HC-compatible clock source. For internal clock operation, connect pin 23 per the clock operation description.                                                                                                                                                                                                                                                                                    |

| 24 to 25                         | A0 to A1                         | Address Inputs. Used to select one of four analog input channels in combination with $\overline{CS}$ and $\overline{WR}$ . The address inputs are latched on the rising edge of $\overline{WR}$ or $\overline{CS}$ .         A1       A0       Selected Channel         LOW       LOW       AIN0         LOW       HIGH       AIN1         HIGH       LOW       AIN2         HIGH       HIGH       AIN3                                                                                                     |

| 26                               | CAL<br>(SHC)                     | Calibration Input. A calibration cycle is initiated when $\overrightarrow{CAL}$ is LOW. The minimum pulse width of $\overrightarrow{CAL}$ is 100ns. If not used, connect to V <sub>D</sub> . In this case calibration is only initiated at power on, or with SFR. If D2 of the SFR is programmed HIGH, pin 26 will be used as an input to control the sample-to-hold timing. A rising edge on pin 26 will switch from sample-mode to hold-mode and initiate a conversion. This pin has an internal pull-up. |

| 27                               | AGND                             | Analog Ground. AGND = 0V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 28                               | V <sub>A</sub>                   | Analog Supply. $V_A = +5V$ . Must be $\geq V_D$ and $V_{RFF}$ +.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

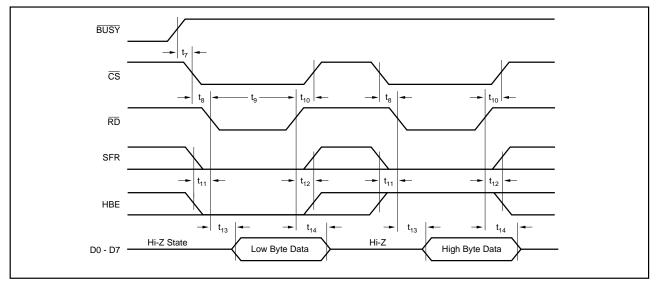

#### **READING DATA**

Data from the ADS7803 is read in two 8-bit bytes, with the Low byte containing the 8 LSBs of data, and the High byte containing the 4 MSBs of data. The outputs are coded in straight binary (with 0V = 000 hex, 5V = FFF hex), and the data is presented in a right-justified format (with the LSB as

the most right bit in the 16-bit word). Two read operations are required to transfer the High byte and Low byte, and the bytes are presented according to the input level on the High Byte Enable pin (HBE).

The bytes can be read in either order, depending on the status of the HBE input. If HBE changes while  $\overline{CS}$  and  $\overline{RD}$  are

FIGURE 2. Converter Timing.

FIGURE 3. Write Cycle Timing (for initiating conversion or calibration).

FIGURE 4. Read Cycle Timing.

LOW, the output data will change to correspond to the HBE input. Figure 4 shows the timing for reading first the Low byte and then the High byte.

ADS7803 provides two modes for reading the conversion results. At power-up, the converter is set in the Transparent Mode.

#### TRANSPARENT MODE

This is the default mode for ADS7803. In this mode, the conversion decisions from the successive approximation register are latched into the output register as they are made. Thus, the High byte (the 4 MSBs) can be read after the end of the ninth clock cycle (five clock cycles for the mux settling, sample acquisition and auto-zeroing of the comparator, followed by the four clock cycles for the 4MSB decisions.) The complete 12-bit data is available after BUSY has gone HIGH, or the internal status flag goes LOW (D7 when HBE is HIGH).

#### LATCHED OUTPUT MODE

This mode is activated by writing a HIGH to D0 in the Special Function Register with  $\overline{CS}$  and  $\overline{WR}$  LOW and SFR and HBE HIGH. (See the discussion of the Special Function Register below.)

In this mode, the data from a conversion is latched into the output buffers only after a conversion is complete, and remains there until the next conversion is completed. The conversion result is valid during the next conversion. This allows the data to be read even after a new conversion is started, for faster system throughput.

#### TIMING CONSIDERATIONS

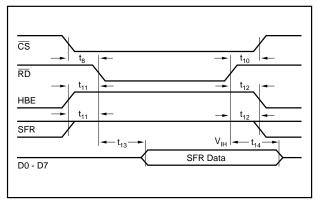

Table I and Figures 3 through 9 show the digital timing of ADS7803 under the various operating modes. All of the critical parameters are guaranteed over the full  $-40^{\circ}$ C to  $+85^{\circ}$ C operating range for ease of system design.

#### SPECIAL FUNCTION REGISTER (SFR)

An internal register is available, either to determine additional data concerning the ADS7803, or to write additional instructions to the converter.

Table II shows the data in the Special Function Register that will be transferred to the output bus by driving HBE HIGH (with SFR HIGH) and initiating a read cycle (driving  $\overline{RD}$  and  $\overline{CS}$  LOW with  $\overline{WR}$  HIGH.) The Power Fail flag in the SFR is set when the power supply falls below about 3V. The flag also means that a new calibration has been started, and any data written to the SFR has been lost. Thus, the ADS7803 will again be in the Transparent Mode. Writing a LOW to D5 in the SFR resets the Power Fail flag. The Cal Error flag in the SFR is set when an overflow occurs during calibration, which may happen in very noisy systems. It is reset by starting a calibration, and remains low after a calibration without an overflow is completed.

Table III shows how instructions can be transferred to the Special Function Register by driving HBE HIGH (with SFR HIGH) and initiating a write cycle (driving  $\overline{WR}$  and  $\overline{CS}$  LOW with  $\overline{RD}$  HIGH.) Note that writing to the SFR also initiates a new conversion.

| SYMBOL          | PARAMETER <sup>(1)</sup>                                                     | MIN | TYP | MAX | UNITS      |

|-----------------|------------------------------------------------------------------------------|-----|-----|-----|------------|

| t <sub>1</sub>  | CS to WR Setup Time <sup>(2)</sup>                                           | 0   | 0   | 0   | ns         |

| t <sub>2</sub>  | WR or CAL Pulse Width                                                        | 100 |     |     | ns         |

| t <sub>3</sub>  | CS to WR Hold Time <sup>(2)</sup>                                            | 0   | 0   | 0   | ns         |

| t <sub>4</sub>  | WR to BUSY Propagation Delay                                                 | 20  | 50  | 150 | ns         |

| t <sub>5</sub>  | A0, A1, HBE, SFR Valid to WR Setup Time                                      | 0   |     |     | ns         |

| t <sub>6</sub>  | A0, A1, HBE, SFR Valid to WR Hold Time                                       | 20  |     |     | ns         |

| t <sub>7</sub>  | BUSY to CS Setup Time                                                        | 0   |     |     | ns         |

| t <sub>8</sub>  | CS to RD Setup Time <sup>(2)</sup>                                           | 0   | 0   | 0   | ns         |

| t <sub>9</sub>  | RD Pulse Width                                                               | 100 |     |     | ns         |

| t <sub>10</sub> | CS to RD Hold Time <sup>(2)</sup>                                            | 0   | 0   | 0   | ns         |

| t <sub>11</sub> | HBE, SFR to RD Setup Time                                                    | 50  |     |     | ns         |

| t <sub>12</sub> | HBE, SFR to RD Hold Time                                                     | 0   |     |     | ns         |

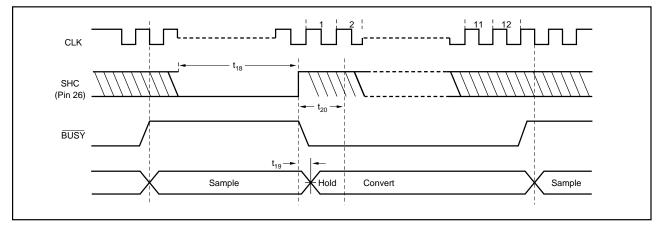

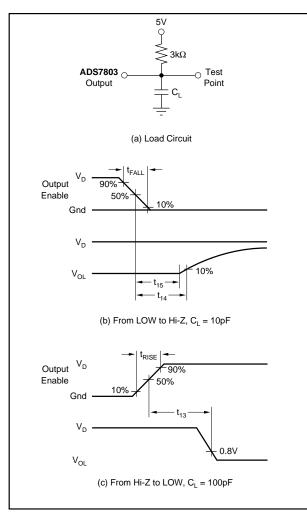

| t <sub>13</sub> | RD to Valid Data (Bus Access Time) <sup>(3)</sup>                            |     | 80  | 150 | ns         |

| t <sub>14</sub> | RD to Hi-Z Delay (Bus Release Time) <sup>(3)</sup>                           |     | 90  | 180 | ns         |

| t <sub>15</sub> | RD to Hi-Z Delay For SFR <sup>(3)</sup>                                      | 20  |     | 60  | ns         |

| t <sub>16</sub> | Data Valid to WR Setup Time                                                  | 100 |     |     | ns         |

| t <sub>17</sub> | Data Valid to WR Hold Time                                                   | 20  |     |     | ns         |

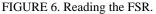

| t <sub>18</sub> | Acquisition Time. Pin 26 LOW with D2 in SFR HIGH                             | 2.5 |     |     | μs         |

| t <sub>19</sub> | Sample-to-Hold Aperture Delay. (D2 in SFR HIGH)                              |     | 5   |     | ns         |

| t <sub>20</sub> | Delay from rising edge on pin 26 to start of conversion.<br>(D2 in SFR HIGH) |     |     | 1.5 | CLK cycles |

$V_{IL}$ ,  $V_{OH}$  or  $V_{OL}$ . (2) The internal RD pulse is performed by a NOR wiring of  $\overline{CS}$  and  $\overline{RD}$ . The internal WR pulse is performed by a NOR wiring of  $\overline{CS}$  and  $\overline{WR}$ . (3) Figures 8 and 9 show the measurement circuits and pulse diagrams for testing transitions to and from Hi-Z states.

TABLE I. Timing Specifications (CLK = 2MHz external,  $T_A = -40^{\circ}$ C to +85°C).

| PIN     | FUNCTION                                                                                                                                                                                                                       | DESCRIPTION                                                                                                                       |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D0      | Mode Status                                                                                                                                                                                                                    | If LOW, Transparent Mode enabled for<br>data latches. If HIGH, latched Output<br>Mode enabled.                                    |  |  |  |  |  |

| D1      | CAL Flag                                                                                                                                                                                                                       | If HIGH, calibration cycle in progress.                                                                                           |  |  |  |  |  |

| D2      | Pin 26 Status                                                                                                                                                                                                                  | If LOW, pin 26 used as input to initiate<br>calibration cycle. If HIGH, pin 26 used as<br>input to control sample-to-hold timing. |  |  |  |  |  |

| D3      | Power Down Status                                                                                                                                                                                                              | If HIGH, in Power Down Mode.                                                                                                      |  |  |  |  |  |

| D4      |                                                                                                                                                                                                                                | Reserved for factory use.                                                                                                         |  |  |  |  |  |

| D5      | POWER FAIL Flag                                                                                                                                                                                                                | If HIGH, a power supply failure has<br>occurred. (Supply fell below 3V.)                                                          |  |  |  |  |  |

| D6      | CAL ERROR Flag                                                                                                                                                                                                                 | If HIGH, an overflow occurred during<br>calibration.                                                                              |  |  |  |  |  |

| D7      | BUSY Flag                                                                                                                                                                                                                      | If HIGH, conversion or calibration in progress.                                                                                   |  |  |  |  |  |

| with SF | NOTE: These data are transferred to the bus when a read cycle is initiated<br>with SFR and HBE HIGH. Reading the SFR with SFR HIGH and HBE LOW<br>is reserved for factory use at this time, and will yield unpredictable data. |                                                                                                                                   |  |  |  |  |  |

TABLE II. Reading the Special Function Register.

#### POWER DOWN MODE

Writing a HIGH to D3 in the SFR puts the ADS7803 in the Power Down Mode. Power consumption is reduced to  $50\mu$ W and D3 remains HIGH. The internal clock and analog circuitry are turned off, although the output registers and SFR can still be accessed normally. To exit Power Down Mode, either write a LOW to D3 in the SFR, or initiate a calibration by sending a LOW to the CAL pin or writing a HIGH to D1. Note that if the power supply falls below 3V and then recovers, a calibration is automatically initiated, and the SFR will be reset. D3 will be LOW, and the ADS7803 will not be in the Power Down Mode.

During Power Down Mode, a pulse on  $\overline{CS}$  and  $\overline{WR}$  will initiate a single conversion, then the ADS7803 will revert to power down. Also, writing to D1 and D3 in the SFR will initiate a calibration, do a single conversion and revert to the Power Down Mode, in 185 clock cycles. Accurate conversion results will be available in the output registers.

The activation delay from power down to normal operation is included in the sampling time. No extra time is required, either when coming out of the Power Down Mode or when making a single conversion in the Power Down Mode.

FIGURE 5. Writing to the SFR.

#### SAMPLE/HOLD CONTROL MODE

With D2 in the SFR HIGH, a rising edge input on pin 26 will switch the ADS7803 from sample-mode to hold-mode with a 5ns aperture delay. This also initiates a conversion, which will start within 1.5 CLK cycles.

This mode allows full control over the sample-to-hold timing, which is especially useful where external events trigger sampling timing.

In the Sample/Hold Control Mode, pin 26 must be held LOW a minimum of  $2.5\mu s$  between conversions to allow accurate acquisition of input signals. Also, offset error will increase in this mode, since auto-zeroing of the comparator is not synchronized to the sampling. Minimum offset is achieved by synchronizing the sampling signal to CLK, whether internal or external. Ideally, the sampling signal

| OPERATION                                    | CS/WR | SFR/HBE | D0                  | D1   | D2                  | D3                  | D5  | D4/D6/D7 |

|----------------------------------------------|-------|---------|---------------------|------|---------------------|---------------------|-----|----------|

| Enables Transparent Mode for Data Latches    | LOW   | HIGH    | LOW                 | Х    | Х                   | Х                   | Х   | LOW      |

| Enables Latched Output Mode for Data Latches | LOW   | HIGH    | HIGH <sup>(1)</sup> | Х    | Х                   | Х                   | Х   | LOW      |

| Initiates Calibration Cycle                  | LOW   | HIGH    | Х                   | HIGH | Х                   | Х                   | Х   | LOW      |

| Activates Sample/Hold Control Mode           | LOW   | HIGH    | Х                   | Х    | HIGH <sup>(1)</sup> | Х                   | Х   | LOW      |

| Activates Power Down Mode <sup>(2)</sup>     | LOW   | HIGH    | Х                   | Х    | Х                   | HIGH <sup>(1)</sup> | Х   | LOW      |

| Resets Power Fail Flag                       | LOW   | HIGH    | Х                   | Х    | Х                   | Х                   | LOW | LOW      |

NOTES: (1) Writing a LOW here reactivates the standard mode of operation. (2) In Power Down Mode, a pulse on CS and WR will initiate a single conversion, then the ADS7803 will revert to power down. (3) X means it can be either HIGH or LOW without affecting this action. Writing HIGH to D4 or D6, or writing with SFR HIGH and HBE LOW, may result in unpredictable behavior. These modes are reserved for factory use at this time.

TABLE III. Writing to the Special Function Register.

rising edge should be delayed 20ns from the falling edge of CLK. This will keep offset error to about 1LSB.

In the Sample/Hold Control Mode, a LOW pulse on  $\overline{WR}$  (with  $\overline{CS}$  LOW) will not initiate a conversion, but the rising edge will latch the multiplexer channel according to the inputs on A0 and A1. When changing channels, this must be done at least 2.5µs before pin 26 goes HIGH (to start a conversion.)

#### **CONTROL LINES**

Table IV shows the functions of the various control lines on the ADS7803. The use of standard  $\overline{CS}$ ,  $\overline{RD}$  and  $\overline{WR}$  control signals simplifies use with most microprocessors. At the same time, flexibility is assured by availability of status information and control functions, both through the SFR and directly on pins.

### INSTALLATION

#### INPUT IMPEDANCE

ADS7803 has a very high input impedance (input bias current over temperature is 100nA max), and a low 50pF input capacitance. To ensure a conversion accurate to 12 bits, the analog source must be able to charge the 50pF and settle within the first five clock cycles after a conversion is initiated. During this time, the input is also very sensitive to

noise at the analog input, since it could be injected into the capacitor array.

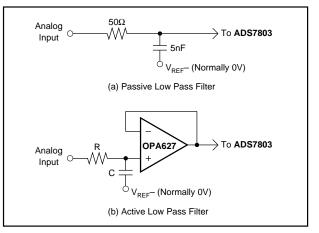

In many applications, a simple passive low-pass filter as shown in Figure 10a can be used to improve signal quality. In this case, the source impedance needs to be less than  $5k\Omega$  to keep the induced offset errors below 1/2LSB, and to meet the acquisition time of five clock cycles. The values in Figure 10a meet these requirements, and will maintain the full power bandwidth of the system. For higher source impedances, a buffer like the one in Figure 10b should be used.

#### INPUT PROTECTION

The input signal range must not exceed  $\pm V_{REF}$  or  $V_A$  by more than 0.3V.

The analog inputs are internally clamped to  $V_A$ . To prevent damage to the ADS7803, the current that can flow into the inputs must be limited to 20mA. One approach is to use an external resistor in series with the input filter resistor. For example, a 1k $\Omega$  input resistor allows an overvoltage to 20V without damage.

#### **REFERENCE INPUTS**

A 10 $\mu$ F tantalum capacitor is recommended between V<sub>REF</sub>+ and V<sub>REF</sub>- to insure low source impedance. These capacitors should be located as close as possible to the ADS7803

| ĊS | RD | WR  | SFR | HBE | CAL | BUSY | OPERATION                                                                                               |

|----|----|-----|-----|-----|-----|------|---------------------------------------------------------------------------------------------------------|

| X  | х  | х   | х   | х   | 011 | х    | Initiates calibration cycle. (See SFR section for alternate use as Sample/<br>Hold Control Mode input.) |

| Х  | Х  | Х   | Х   | Х   | Х   | 0    | Conversion or calibration in process. Inhibits new conversion from starting.                            |

| 1  | Х  | Х   | Х   | Х   | 1   | х    | None. Outputs in Hi-Z State.                                                                            |

| 0  | 1  | 0↑1 | 0   | Х   | 1   | 1    | Initiates conversion.                                                                                   |

| 0  | 0  | 1   | 0   | 0   | 1   | Х    | Low byte conversion results output on data bus.                                                         |

| 0  | 0  | 1   | 0   | 1   | 1   | х    | High byte conversion results output on data bus.                                                        |

| 0  | 1  | 0   | 1   | 1   | 1   | 1    | Write to SFR and rising edge on WR initiates conversion.                                                |

| 0  | 0  | 1   | 1   | 1   | 1   | х    | Contents of SFR output on data bus.                                                                     |

| 0  | 1  | 0   | 1   | 0   | 1   | х    | Reserved for factory use.                                                                               |

| 0  | 0  | 1   | 1   | 0   | 1   | х    | Reserved for factory use. (Unpredictable data on data bus.)                                             |

TABLE IV. Control Line Functions.

FIGURE 7. Timing for Initiating Conversion in Sample/Hold Control Mode (D2 in SFR HIGH).

FIGURE 8. Measuring Active LOW to/from Hi-Z State.

to reduce dynamic errors, since the reference provides packets of current as the successive approximation steps are carried out.

$V_{REF}^{+}$  must not exceed  $V_A$ . Although the accuracy is specified with  $V_{REF}^{+} = 5V$  and  $V_{REF}^{-} = 0V$ , the converter can function with  $V_{REF}^{+}$  as low as 4.5V and  $V_{REF}^{-}$  as high as 1V.

As long as there is at least a 4.5V difference between  $V_{REF}^+$ and  $V_{REF}^-$ , the absolute value of errors does not change significantly, so that accuracy will typically be within ±1LSB

The power supply to the reference source needs to be considered during system design to prevent  $V_{REF}$ + from exceeding (or overshooting)  $V_A$ , particularly at power-on. Also, after power-on, if the reference is not stable within 42,425 clock cycles, an additional calibration cycle may be needed.

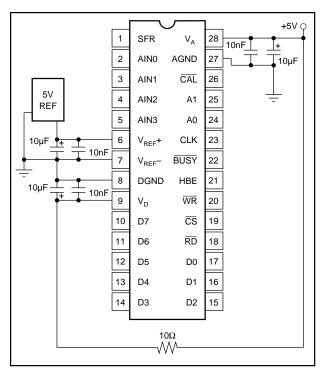

#### POWER SUPPLIES

The digital and analog power supply lines to the ADS7803 should be bypassed with  $10\mu$ F tantalum capacitors as close to the part as possible. Although ADS7803 has excellent

FIGURE 9. Measuring Active HIGH to/from Hi-Z State.

power supply rejection, even for higher frequencies, linear regulated power supplies are recommended.

Care should be taken to insure that  $V_D$  does not come up before  $V_A$ , or permanent damage to the part may occur.

FIGURE 10. Input Signal Conditioning.

FIGURE 11. Power Supply and Reference Decoupling.

Figure 11 shows a good supply approach, powering both  $V_A$  and  $V_D$  from a clean linear supply, with the 10 $\Omega$  resistor between  $V_A$  and  $V_D$  insuring that  $V_D$  comes up after  $V_A$ . This is also a good method to further isolate the ADS7803 from digital supplies in a system with significant switching currents that could degrade the accuracy of conversions.

#### GROUNDING

To maximize accuracy of the ADS7803, the analog and digital grounds are not connected internally. These points should have very low impedance to avoid digital noise feeding back into the analog ground. The  $V_{REF}$  pin is used as the reference point for input signals, so it should be connected directly to AGND to reduce potential noise problems.

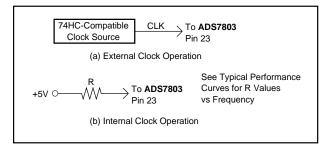

#### EXTERNAL CLOCK OPERATION

The circuitry required to drive the ADS7803 clock from an external source is shown in Figure 12a. The external clock must provide a 0.8V max for LOW and a 3.5V min for

FIGURE 12. Internal Clock Operation.

HIGH, with rise and fall times that do not exceed 200ns. The duty cycle of the external clock can vary as long as the LOW time and HIGH time are each at least 200ns wide. Synchronizing the conversion clock to an external system clock is recommended in microprocessor applications to prevent beat-frequency problems.

Note that the electrical specification tables are based on using an external 2MHz clock. Typically, the specified accuracy is maintained for clock frequencies between 0.5 and 2.4MHz.

#### INTERNAL CLOCK OPERATION

Figure 12b shows how to use the internal clock generating circuitry. The clock frequency depends only on the value of the resistor, as shown in "Internal Clock Frequency vs  $R_{CLOCK}$ " in the Typical Performance Curves section.

The clock generator can operate between 100kHz and 2MHz. With  $R = 100k\Omega$ , the clock frequency will nominally be 800kHz. The internal clock oscillators may vary by up to 20% from device to device, and will vary with temperature, as shown in the typical performance curves. Therefore, use of an external clock source is preferred in applications where control of the conversion timing is critical, or where multiple converters need to be synchronized.

### **APPLICATIONS**

#### **BIPOLAR INPUT RANGES**

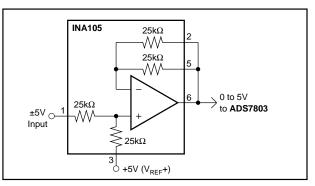

Figure 13 shows a circuit to accurately and simply convert a bipolar  $\pm 5V$  input signal into a unipolar 0 to 5V signal for conversion by the ADS7803, using a precision, low-cost complete difference amplifier, INA105.

FIGURE 13. ±5V Input Range.

FIGURE 14. ±10V Input Range.

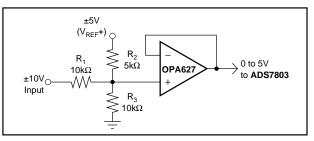

Figure 14 shows a circuit to convert a bipolar  $\pm 10V$  input signal into a unipolar 0 to 5V signal for conversion by the ADS7803. The precision of this circuit will depend on the matching and tracking of the three resistors used.

To trim this circuit for full 12-bit precision,  $R_2$  and  $R_3$  need to be adjustable over appropriate ranges. To trim, first have the ADS7803 converting continually and apply +9.9927V (+10V – 1.5LSB) at the input. Adjust  $R_3$  until the ADS7803 output toggles between the codes FFE hex and FFF hex. This makes  $R_3$  extremely close to  $R_1$ . Then, apply –9.9976V (-10V + 0.5LSB) at the input, and adjust  $R_2$  until the ADS7803 output toggles between 000 hex and 001 hex. At each trim point, the current through the third resistor will be almost zero, so that one trim iteration will be enough in most cases. More iterations may be required if the op amp selected has large offset voltage or bias currents, or if the +5V reference is not precise.

This circuit can also be used to adjust gain and offset errors due to the components preceding the ADS7803, to match the performance of the self-calibration provided by the converter.

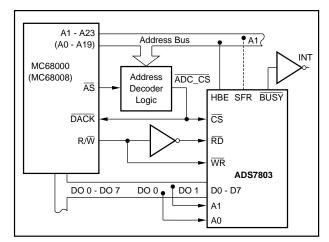

#### INTERFACING TO MOTOROLA MICROPROCESSORS

Figure 15 show a typical interface to Motorola microprocessors, while Figure 16 shows how the result can be placed in register D0.

Conversion is initiated by a write instruction decoded by the address decoder logic, with the lower two bits of the address bus selecting an ADC input channel, as follows:

#### MOVE.W D0, ADC-ADDRESS

The result of the conversion is read from the data bus by a read instruction to ADC-ADDRESS as follows:

FIGURE 15. Interface to Motorola Microprocessors.

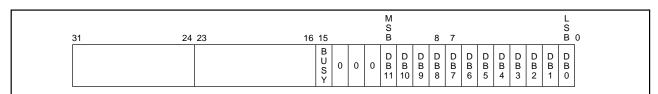

#### MOVEP.W \$000 (ADC-ADDRESS), D0

This puts the 12-bit conversion result in the D0 register, as shown in Figure 15. The address decoder must pull down ADC\_CS AT ADC-ADDRESS to access the Low byte and ADC-ADDRESS +2 to access the High byte.

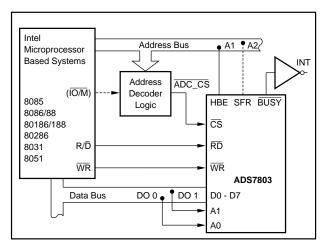

#### INTERFACING TO INTEL MICROPROCESSORS

Figure 17 shows a typical interface to Intel.

A conversion is initiated by write instruction to address ADC\_CS. Data pins DO0 and DO1 select the analog input channel. The BUSY signal can be used to generate a micro-processor interrupt (INT) when the conversion is completed.

A read instruction from the ADC\_CS address fetches the Low byte, and a read instruction from the ADC\_CS address +2 fetches the High byte.

FIGURE 16. Conversion Results in Motorola Register D0.

FIGURE 17. Interface to Intel Microprocessors.