## ADC80

# General Purpose ANALOG-TO-DIGITAL CONVERTER

#### **FEATURES**

- INDUSTRY-STANDARD 12-BIT ADC

- ±0.012% LINEARITY

- 25µs max CONVERSION TIME

- ±12V OR ±15V OPERATION

- NO MISSING CODES: -25°C to +85°C

- HERMETIC 32-PIN PACKAGE

- PARALLEL AND SERIAL OUTPUTS

- 595mW max DISSIPATION

## **DESCRIPTION**

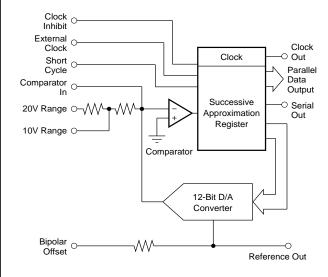

The ADC80 is a 12-bit successive-approximation analog-to-digital converter, utilizing state-of-the-art CMOS and laser-trimmed bipolar die custom designed for freedom from latch-up and optimum AC performance. It is complete with a comparator, a monolithic 12-bit DAC which includes a 6.3V reference laser-trimmed for minimum temperature coefficient, and a CMOS logic chip containing the successive approximation register (SAR), clock, and all other associated logic functions.

Internal scaling resistors are provided for the selection of analog input signal ranges of  $\pm 2.5$ V,  $\pm 5$ V,  $\pm 10$ V, 0 to +5V, or 0 to +10V. Gain and offset errors may be externally trimmed to zero, enabling initial endpoint accuracies of better than  $\pm 0.12$ % ( $\pm 1/2$ LSB).

The maximum conversion time of 25µs makes the ADC80 ideal for a wide range of 12-bit applications requiring system throughput sampling rates up to 40kHz. In addition, the ADC80 may be short-cycled for faster conversion speed with reduced resolution, and an external clock may be used to synchronize the converter to the system clock or to obtain higher speed operation.

Data is available in parallel and serial form with corresponding clock and status signals. All digital input and output signals are TTL/LSTTL-compatible, with internal pull-up resistors included on all digital inputs to eliminate the need for external pull-up resistors on digital inputs not requiring connection. The ADC80 operates equally well with either  $\pm 15$ V or  $\pm 12$ V analog power supplies, and also requires use of a  $\pm 5$ V logic power supply. However, unlike many ADC-type products, a  $\pm 5$ V analog power supply is not required. It is packaged in a hermetic 32-pin side-brazed ceramic dual-in-line package.

International Airport Industrial Park

• Mailing Address: PO Box 11400

• Tucson, AZ 85734

• Street Address: 6730 S. Tucson Blvd.

• Tucson, AZ 85706

Tel: (520) 746-1111

• Twx: 910-952-1111

• Cable: BBRCORP

• Telex: 066-6491

• FAX: (520) 889-1510

• Immediate Product Info: (800) 548-6132

## **SPECIFICATIONS**

#### **ELECTRICAL**

At  $T_A$  = +25°C,  $\pm V_{CC}$  = 12V or 15V,  $V_{DD}$  = +5V, unless otherwise specified.

|                                                                          | ADC80AG  |                   |              |                                     |  |

|--------------------------------------------------------------------------|----------|-------------------|--------------|-------------------------------------|--|

| PARAMETER                                                                | MIN      | TYP               | MAX          | UNITS                               |  |

| RESOLUTION                                                               |          |                   |              |                                     |  |

| ADC80AG-12, ADC80-AGZ-12 <sup>(1)</sup>                                  |          |                   | 12           | Bits                                |  |

| ADC80AG-10                                                               |          |                   | 10           | Bits                                |  |

| INPUT                                                                    |          |                   |              |                                     |  |

| ANALOG                                                                   |          |                   |              |                                     |  |

| Voltage Ranges: Unipolar                                                 |          | 0 to +5, 0 to +10 |              | V                                   |  |

| Bipolar                                                                  |          | ±2.5, ±5, ±10     |              | V                                   |  |

| Impedance: 0 to +5V, ±2.5V                                               | 2.45     | 2.5               | 2.55         | kΩ                                  |  |

| 0 to +10V, +5V                                                           | 4.9      | 5                 | 5.1          | kΩ                                  |  |

| ±10V                                                                     | 9.8      | 10                | 10.2         | kΩ                                  |  |

| DIGITAL                                                                  |          |                   |              |                                     |  |

| Logic Characteristics (Over specification temperature range)             | 0        |                   |              |                                     |  |

| V <sub>IH</sub> (Logic "1")                                              | 2        |                   | 5.5          | V                                   |  |

| V <sub>IL</sub> (Logic "0")<br>I <sub>IH</sub> (V <sub>IN</sub> = +2.7V) | -0.3     |                   | +0.8<br>-150 | μA                                  |  |

| $I_{IL}(V_{IN} = +2.7V)$ $I_{IL}(V_{IN} = +0.4V)$                        |          |                   | 500          | μΑ                                  |  |

| Convert Command Pulse Width <sup>(2)</sup>                               | 100      |                   | 2000         | ns                                  |  |

| TRANSFER CHARACTERISTICS                                                 |          |                   |              |                                     |  |

|                                                                          |          | T                 |              |                                     |  |

| ACCURACY Gain Error <sup>(2)</sup>                                       |          | +0.4              | 10.3         | 0/ of ECD(4)                        |  |

| Offset Error <sup>(3)</sup> : Unipolar                                   |          | ±0.1<br>±0.05     | ±0.3<br>±0.2 | % of FSR <sup>(4)</sup><br>% of FSR |  |

| Bipolar                                                                  |          | ±0.1              | ±0.2<br>±0.3 | % of FSR                            |  |

| Linearity Error: ADC80AG-12, ADC80AGZ-12                                 |          | ±0.1              | ±0.012       | % of FSR                            |  |

| ADC80AG-10                                                               |          |                   | ±0.048       | % of FSR                            |  |

| Differential Linearity Error                                             |          | ±1/2              | ±3/4         | LSB                                 |  |

| Inherent Quantization Error                                              |          | ±1/2              |              | LSB                                 |  |

| POWER SUPPLY SENSITIVITY                                                 |          |                   |              |                                     |  |

| $11.4V \le \pm V_{CC} \le 16.5V$                                         |          | ±0.003            | ±0.009       | % of FSR/%V <sub>CC</sub>           |  |

| $+4.5V \le V_{DD} \le +5.5V$                                             |          | ±0.002            | ±0.005       | % of FSR/%V <sub>DD</sub>           |  |

| DRIFT                                                                    |          |                   |              |                                     |  |

| Total Accuracy, Bipolar <sup>(5)</sup>                                   |          | ±10               | ±23          | ppm/°C                              |  |

| Gain                                                                     |          | ±15               | ±30          | ppm/°C                              |  |

| Offset: Unipolar                                                         |          | ±3                |              | ppm of FSR/°C                       |  |

| Bipolar                                                                  |          | ±7                | ±15          | ppm of FSR/°C                       |  |

| Linearity Error Drift                                                    |          | ±1                | ±3           | ppm of FSR/°C                       |  |

| Differential Linearity over Temperature Range                            |          |                   | ±3/4         | LSB                                 |  |

| No Missing Code Temperature Range                                        | –25      | 0                 | +85          | °C                                  |  |

| Monotonicity Over Temperature Range                                      |          | Guaranteed        |              |                                     |  |

| CONVERSION TIME <sup>(6)</sup>                                           | 45       | 00                | 05           |                                     |  |

| ADC80AG-12, ADC80-AGZ-12                                                 | 15<br>13 | 22 20             | 25<br>22     | μs                                  |  |

| ADC80AG-10                                                               | 13       | 20                | 22           | μs                                  |  |

| OUTPUT                                                                   |          | T                 |              |                                     |  |

| DIGITAL (Bits 1-12 , Clock Out, Status, Serial Out)                      |          |                   |              | 1                                   |  |

| Output Codes <sup>(7)</sup>                                              |          | CSB               |              | 1                                   |  |

| Parallel: Unipolar<br>Bipolar                                            |          | CSB<br>COB, CTC   |              |                                     |  |

| Serial (NRZ) <sup>(8)</sup>                                              |          | COB, CTC          |              | 1                                   |  |

| Logic Levels: Logic 0 (I <sub>SINK</sub> ≤ 3.2mA)                        |          | 000,000           | +0.4         | V                                   |  |

| Logic 1 (I <sub>SOURCE</sub> ≤ 80μA)                                     | +2.4     |                   |              | v                                   |  |

| Internal Clock Frequency                                                 |          | 545               |              | kHz                                 |  |

| INTERNAL REFERENCE VOLTAGE                                               |          |                   |              |                                     |  |

| Voltage                                                                  | +6.2     | +6.3              | +6.4         | V                                   |  |

| Source Current Available for External Loads <sup>(9)</sup>               | 200      |                   |              | μA                                  |  |

|                                                                          |          |                   |              |                                     |  |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

## **SPECIFICATIONS** (CONT)

#### **ELECTRICAL**

At  $T_A$  = +25°C,  $\pm V_{CC}$  = 12V or 15V,  $V_{DD}$  = +5V, unless otherwise specified.

|                                            | ADC80AG |     |       |       |

|--------------------------------------------|---------|-----|-------|-------|

| PARAMETER                                  | MIN     | TYP | MAX   | UNITS |

| POWER SUPPLY REQUIREMENTS (For all models) |         |     |       |       |

| Voltage: ±V <sub>CC</sub>                  | ±11.4   | ±15 | ±16.5 | V     |

| $V_{DD}$                                   | +4.5    | +5  | +5.5  | V     |

| Current: +I <sub>CC</sub>                  |         | 5   | 8.5   | mA    |

| -I <sub>cc</sub>                           |         | 21  | 26    | mA    |

| I <sub>DD</sub>                            |         | 11  | 15    | mA    |

| Power Dissipation ( $\pm V_{CC} = 15V$ )   |         | 450 | 595   | mW    |

| Thermal Resistance, $\theta_{JA}$          |         | 50  |       | °C/W  |

| TEMPERATURE RANGE (Ambient)                |         |     |       |       |

| Specification                              | -25     |     | +85   | °C    |

| Operating (derated specs)                  | -55     |     | +125  | °C    |

| Storage                                    | -65     |     | +150  | °C    |

NOTES: (1) ADC80AGZ-12 is not recommended for new designs. Standard ADC80AG-12 now meets the extended power supply range of the ADC80AGZ-12. (2) Accurate conversion will be obtained with any convert command pulse width of greater than 100ns; however, it must be limited to 2μs (max) to assure the specified conversion time. (3) Gain and offset errors are adjustable to zero. See "Optional External Gain and Offset Adjustment" section. (4) FSR means Full-Scale Range and is 20V for ±10V range, 10V for ±5V and 0 to +10V ranges, etc. (5) Includes drift due to linearity, gain, and offset drifts. (6) Conversion time is specified using internal clock. For operation with an external clock see "Clock Options" section. This converter may also be short-cycled to less than 12-bit resolution for shorter conversion time: see "Short Cycle Feature" section. (7) CSB means Complementary Straight Binary, COB means Complementary Offset Binary, and CTC means Complementary Two's Complement coding. See Table 1 for additional information. (8) NRZ means Non-Return-to-Zero coding. (9) External loading must be constant during conversion, and must not exceed 200μA for guaranteed specification.

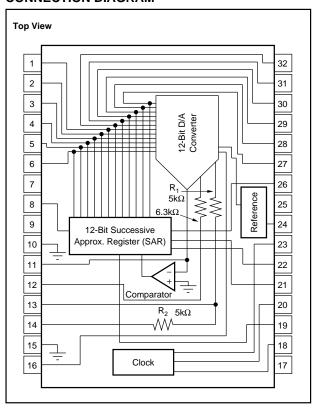

#### **PIN ASSIGNMENTS**

| PIN | DESCRIPTION                   | PIN               | DESCRIPTION           |

|-----|-------------------------------|-------------------|-----------------------|

| 1   | Bit 6                         | 32                | Bit 7                 |

| 2   | Bit 5                         | 31                | Bit 8                 |

| 3   | Bit 4                         | 30                | Bit 9                 |

| 4   | Bit 3                         | 29                | Bit 10 (LSB-10 Bits)  |

| 5   | Bit 2                         | 28                | Bit 11                |

| 6   | Bit 1 (MSB)                   | 27                | Bit 12 (LSB-12 Bits)  |

| 7   | NC <sup>(1)</sup>             | 26                | Serial Out            |

| 8   | Bit 1 (MSB)                   | 25                | -V <sub>cc</sub>      |

| 9   | +5V Digital Supply            | 24                | Reference Out (+6.3V) |

| 10  | Digital Common <sup>(2)</sup> | 23                | Clock Out             |

| 11  | Comparator In                 | 22                | Status                |

| 12  | Bipolar Offset                | 21                | Short Cycle           |

| 13  | R <sub>1</sub> 10V Range      | 20                | Clock Inhibit         |

| 14  | R <sub>2</sub> 20V Range      | 19 External Clock |                       |

| 15  | Analog Common                 | 18 Convert Comma  |                       |

| 16  | Gain Adjust                   | 17                | +V <sub>CC</sub>      |

NOTE: (1) +5V applied to pin 7 has no effect on circuit. (2) Metal lid of package is connected to pin 10.

#### **CONNECTION DIAGRAM**

ADC80

#### **ABSOLUTE MAXIMUM RATINGS**

| +V <sub>CC</sub> to Analog Common         | 0 to +16.5V                        |

|-------------------------------------------|------------------------------------|

| -V <sub>CC</sub> to Analog Common         |                                    |

| V <sub>DD</sub> to Digital Common         |                                    |

| Analog Common to Digital Common           |                                    |

| Logic Inputs (Convert Command, Clock In)  |                                    |

| to Digital Common                         | 0.3V to +V <sub>DD</sub> +0.5V     |

| Analog Inputs (Analog In, Bipolar Offset) |                                    |

| to Analog Common                          | ±16.5V                             |

| Reference Output                          | . Indefinite Short to Common,      |

|                                           | Momentary Short to V <sub>CC</sub> |

| Lead Temperature, (soldering, 10s)        | +300°C                             |

|                                           |                                    |

| CAUTION: These devices are sensitive      | to electrostatic discharge.        |

CAUTION: These devices are sensitive to electrostatic discharge Appropriate I.C. handling procedures should be followed.

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

#### ORDERING INFORMATION

| MODEL                     | RESOLUTION<br>(Bits) |

|---------------------------|----------------------|

| ADC80AG-10                | 10                   |

| ADC80G-12                 | 12                   |

| ADC80GZ-12 <sup>(1)</sup> | 12                   |

NOTE: (1) ADC80AGZ-12 is not recommended for new designs. Standard ADC80AG-12 now meets the extended power supply range of the ADC80AGZ-12.

#### **PACKAGE INFORMATION**

| MODEL                     | PACKAGE         | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|---------------------------|-----------------|------------------------------------------|

| ADC80AG-10                | 32-Pin Hermetic | 172                                      |

| ADC80G-12                 | 32-Pin Hermetic | 172                                      |

| ADC80AZ-12 <sup>(1)</sup> | 32-Pin Hermetic | 172                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

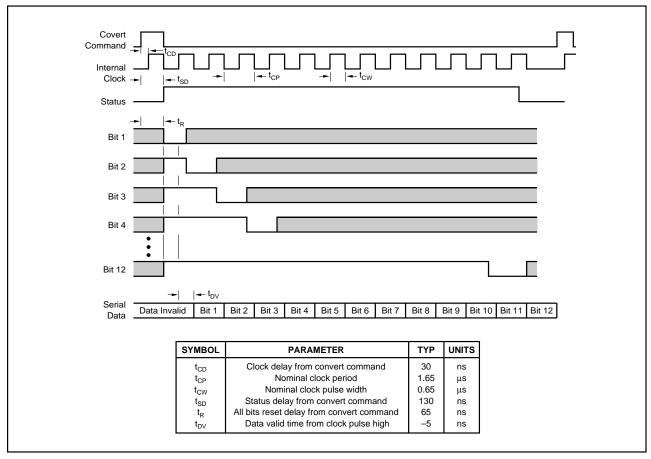

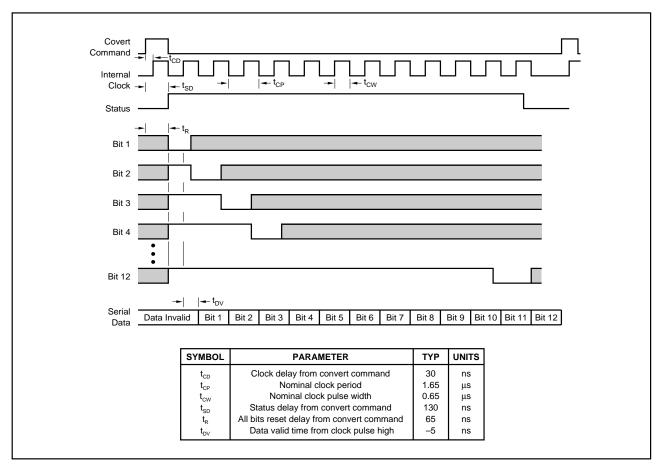

FIGURE 1. ADC80 Timing Diagram (nominal values at +25°C with internal clock).

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

#### **ABSOLUTE MAXIMUM RATINGS**

| +V <sub>CC</sub> to Analog Common         |                                   |

|-------------------------------------------|-----------------------------------|

| V <sub>DD</sub> to Digital Common         | 0 to +7V                          |

| Analog Common to Digital Common           | ±0.5V                             |

| Logic Inputs (Convert Command, Clock In)  |                                   |

| to Digital Common                         | $-0.3V$ to $+V_{DD} + 0.5V$       |

| Analog Inputs (Analog In, Bipolar Offset) |                                   |

| to Analog Common                          | ±16.5V                            |

| Reference Output Indefir                  | nite Short to Common,             |

| Mo                                        | omentary Short to V <sub>CC</sub> |

| Lead Temperature, (soldering, 10s)        | +300°C                            |

|                                           |                                   |

CAUTION: These devices are sensitive to electrostatic discharge. Appropriate I.C. handling procedures should be followed.

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

#### **ORDERING INFORMATION**

|                           | RESOLUTION |

|---------------------------|------------|

| MODEL                     | (Bits)     |

| ADC80AG-10                | 10         |

| ADC80G-12                 | 12         |

| ADC80GZ-12 <sup>(1)</sup> | 12         |

NOTE: (1) ADC80AGZ-12 is not recommended for new designs. Standard ADC80AG-12 now meets the extended power supply range of the ADC80AGZ-12.

#### PACKAGE INFORMATION(1)

| MODEL                     | PACKAGE         | PACKAGE DRAWING<br>NUMBER |

|---------------------------|-----------------|---------------------------|

| ADC80AG-10                | 32-Pin Hermetic | 172                       |

| ADC80G-12                 | 32-Pin Hermetic | 172                       |

| ADC80AZ-12 <sup>(1)</sup> | 32-Pin Hermetic | 172                       |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

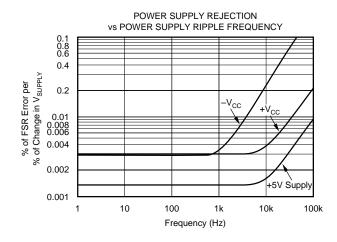

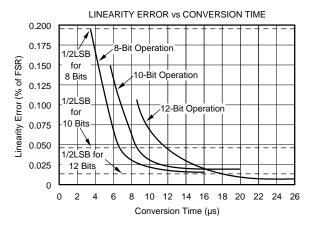

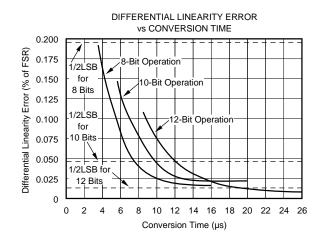

### TYPICAL PERFORMANCE CURVES

At  $T_A$  = +25°C,  $\pm V_{CC}$  = 12V or 15V,  $V_{DD}$  = +5V, unless otherwise specified.

## DISCUSSION OF SPECIFICATIONS

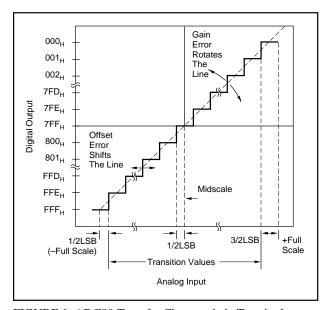

#### LINEARITY ERROR

Linearity error is defined as the deviation of actual code transition values from the ideal transition values. Under this definition of linearity (sometimes referred to as integral linearity), ideal transition values lie on a line drawn through zero (or minus full scale for bipolar operation) and plus full scale, providing a significantly better definition of converter accuracy than the best-straight-line-fit definition of linearity employed by some manufacturers.

The zero or minus full-scale value is located at an analog input value 1/2LSB before the first code transition (FFF $_{\rm H}$  to FFE $_{\rm H}$ ). The plus full-scale value is located at an analog value 3/2LSB beyond the last code transition (001 $_{\rm H}$  to 000 $_{\rm H}$ ). See Figure 1 which illustrates these relationships. A linearity specification which guarantees  $\pm 1/2$ LSB maximum linearity error assures the user that no code transition will differ from the ideal transition value by more than  $\pm 1/2$ LSB.

FIGURE 1. ADC80 Transfer Characteristic Terminology.

Thus, for a converter connected for bipolar operation and with a full-scale range (or span) or 20V ( $\pm 10$ V operation), the minus full-scale value of -10V is 2.44mV below the first code transition (FFF<sub>H</sub> to FFE<sub>H</sub> at -9.99756V) and the plus full-scale value of +10V is 7.32mV above the last code transition ( $001_H$  to  $000_H$  at +9.99268V). Ideal transitions occur 1LSB (4.88mV) apart, and the  $\pm 1/2$ LSB linearity specification guarantees that no actual transition will vary from the ideal by more than 2.44mV. The LSB weights, transition values, and code definitions for each possible ADC80 analog input signal range are described in Table I.

#### **CODE WIDTH (QUANTUM)**

Code width (or quantum) is defined as the range of analog input values for which a given output code will occur. The ideal code width is 1LSB, which for 12-bit operation with a 20V span is equal to 4.88mV. Refer to Table I for LSB values for other ADC80 input ranges.

## DIFFERENTIAL LINEARITY ERROR AND NO MISSING CODES

Differential linearity error is the difference between an ideal 1LSB code width (quantum) and the actual code width. A specification which guarantees no missing codes requires that every code combination appear in a monotonically increasing sequence as the analog input is increased throughout the range, requiring that every input quantum must have a finite width. If an input quantum has a value of zero (a differential linearity error of –1LSB), a missing code will occur but the converter may still be monotonic. Thus, no missing codes represent a more stringent definition of performance than does monotonicity. ADC80 is guaranteed to have no missing codes to 12-bit resolution over its full specification temperature range.

#### **QUANTIZATION UNCERTAINTY**

Analog-to-Digital converters have an inherent quantization error of  $\pm 1/2$ LSB. This error is a fundamental property of the quantization process and cannot be eliminated.

| BINARY OUTPUT                                                                                                                              | INPUT VOLTAGE RANGE AND LSB VALUES              |                                                    |                                                   |                                                  |                                                   |                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------|---------------------------------------------------|--------------------------------------------------|---------------------------------------------------|--------------------------------------------------|

| Analog Input Voltage Range                                                                                                                 | Defined As:                                     | ±10V                                               | ±5V                                               | ±2.5V                                            | 0 to +10V                                         | 0 to +5V                                         |

| Code Designation                                                                                                                           |                                                 | COB(1) or CTC(2)                                   | COB or CTC                                        | COB or CTC                                       | CSB <sup>(3)</sup>                                | CSB                                              |

| One Least Significant Bit (LSB)                                                                                                            | FSR/2 <sup>n</sup><br>n = 8<br>n = 10<br>n = 12 | 20V/2 <sup>n</sup><br>78.13mV<br>19.53mV<br>4.88mV | 10V/2 <sup>n</sup><br>39.06mV<br>9.77mV<br>2.44mV | 5V/2 <sup>n</sup><br>19.53mV<br>4.88mV<br>1.22mV | 10V/2 <sup>n</sup><br>39.06mV<br>9.77mV<br>2.44mV | 5V/2 <sup>n</sup><br>19.53mV<br>4.88mV<br>1.22mV |

| Transition Values  MSB LSB  001 <sub>H</sub> to 000 <sub>H</sub> 800 <sub>H</sub> to 7FF <sub>H</sub> FFF <sub>H</sub> to FFE <sub>H</sub> | +Full Scale<br>Mid Scale<br>-Full Scale         | +10V - 3/2LSB<br>0<br>-10V + 1/2LSB                | +5V -3/2LSB<br>0<br>-5V + 1/2LSB                  | +2.5V - 3/2LSB<br>0<br>-2.5V + 1/2LSB            | +10V - 3/2LSB<br>+5V<br>0 + 1/2LSB                | +5V – 3/2LSB<br>+2.5V<br>0 + 1/2LSB              |

NOTE: (1) COB = Complementary Offset Binary. (2) CTC = Complementary Two's Complement—obtained by using the complement of the most significant bit (MSB). MSB is available on pin 8. (3) CSB = Complementary Straight Binary.

TABLE I. Input Voltages, Transition Values, LSB Values, and Code Definitions.

#### UNIPOLAR OFFSET ERROR

An ADC80 connected for unipolar operation has an analog input range of 0V to plus full scale. The first output code transition should occur at an analog input value 1/2LSB above 0V. Unipolar offset error is defined as the deviation of the actual transition value from the ideal value, and is applicable only to converters operating in the unipolar mode.

#### **BIPOLAR OFFSET ERROR**

A/D converter specifications have historically defined bipolar offset at the first transition value above the minus full-scale value. The ADC80 follows this convention. Thus, bipolar offset error for the ADC80 is defined as the deviation of the actual transition value from the ideal transition value located 1/2LSB above minus full scale.

#### **GAIN ERROR**

The last output code transition  $(001_{\rm H}$  to  $000_{\rm H})$  occurs for an analog input value 3/2LSB below the nominal plus full-scale value. Gain error is the deviation of the actual analog value at the last transition point from the ideal value.

#### **ACCURACY DRIFT VS TEMPERATURE**

The temperature coefficients for gain, unipolar offset, and bipolar offset specify the maximum change from the actual  $25^{\circ}$ C value to the value at the extremes of the specification temperature range. The temperature coefficient applies independently to the two halves of the temperature range above and below  $+25^{\circ}$ C.

#### POWER SUPPLY SENSITIVITY

Electrical specifications for the ADC80 assume the application of the rated power supply voltages of  $\pm 5$ V and  $\pm 12$ V or  $\pm 15$ V. The major effect of power supply voltage deviations from the rated values will be a small change in the plus full-scale value. This change, of course, results in a proportional change in all code transition values (i.e., a gain error). The specification describes the maximum change in the plus full-scale value from the initial value for independent changes in each power supply voltage.

#### TIMING CONSIDERATIONS

Timing relationships of the ADC80 are shown in Figure 2. It should be noted that although the convert command pulse width must be between 100ns and 2µs to obtain the specified conversion time with internal clock, the ADC80 will accept longer convert commands with no loss of accuracy, assuming that the analog input signal is stable.

In this situation, the actual indicated conversion time (during which status is high) for 12-bit operation will be equal to

7

FIGURE 2. ADC80 Timing Diagram (nominal values at +25°C with internal clock).

approximately 1µs less than the sum of the factory-set conversion time and the length of the convert command. The code returned by the converter at the end of the convertion will accurately represent the analog input to the converter at the time the status returns to the low state. In addition, although the initial state of the converter will be indeterminate when power is first applied, it is designed to time-out and be ready to accept a convert command within approximately 25µs after power-up, provided that either an external clock source is present or the internal clock is not inhibited.

During conversion, the decision as to the proper state of any bit (bit "n") is made on the rising edge of clock pulse "n + 1". Thus, a complete conversion requires 13 clock pulses with the status output dropping from logic "1" to logic "0" shortly after the rising edge of the 13th clock pulse, and with valid output data ready to be read at the time. A new conversion may not be initiated until 50ns after the fall of the last clock pulse (pulse 13 for 12-bit operation).

Additional convert commands applied during conversion will be ignored.

#### **DEFINITION OF DIGITAL CODES**

#### **Parallel Data**

Three binary codes are available on the ADC80 parallel output; all three are complementary codes, meaning that logic "0" is true. The available codes are complementary straight binary (CSB) for unipolar input signal ranges, and complementary offset binary (COB) and complementary two's complement (CTC) for bipolar input signal ranges. CTC coding is obtained by complementing bit 1 (the MSB) of the COB code; the complement of bit 1 is available on pin 8.

#### **Serial Data**

Two (complementary) straight binary codes are available on the serial output of the ADC80; as in the parallel case, they are CSB and COB. The serial data is available only during conversion and appears with the most significant bit (MSB) occurring first. The serial data is synchronous with the internal clock as shown in the timing diagram of Figure 2. The LSB and transition values of Table I also apply to the serial data output, except that the CTC code is not available. All clock pulses available from the ADC80 have equal pulse widths to facilitate transfer of the serial data into external logic devices without external shaping.

## LAYOUT AND OPERATING INSTRUCTIONS

#### LAYOUT PRECAUTIONS

Analog and digital commons are not connected together internally in the ADC80, but should be connected together as close to the unit as possible, preferably to an analog common ground plane beneath the converter. If these common lines must be run separately, use a wide conductor pattern and a  $0.01\mu F$  to  $0.1\mu F$  non-polarized bypass capacitor between analog and digital commons at the unit. Low

impedance analog and digital common returns are essential for low noise performance. Coupling between analog input lines and digital lines should be minimized by careful layout. For instance, if the lines must cross, they should do so at right angles. Parallel analog and digital lines should be separated from each other by a pattern connected to common. If external gain and offset potentiometers are used, the potentiometers and associated resistors should be located as close to the ADC80 as possible.

#### **POWER SUPPLY DECOUPLING**

The power supplies should be bypassed with  $1\mu F$  to  $10\mu F$  tantalum bypass capacitors located close to the converter to obtain noise-free operation. Noise on the power supply lines can degrade the converter's performance. Noise and spikes from a switching power supply are especially troublesome.

#### ANALOG SIGNAL SOURCE IMPEDANCE

The signal source supplying the analog input signal to the ADC80 will be driving into a nominal DC input impedance of  $2.5k\Omega$  to  $10k\Omega$  depending upon the range selected. However the output impedance of the driving source should be very low, such as the output impedance provided by a wideband, fast-settling operational amplifier. Transients in A/D input current are caused by the changes in output current of the internal D/A converter as it tests the various bits. The output voltage of the driving source must remain constant while furnishing these fast current changes. If the application requires a sample/hold, select a sample/hold with sufficient bandwidth to preserve the accuracy or use a separate wideband buffer amplifier to lower the output impedance.

#### **INPUT SCALING**

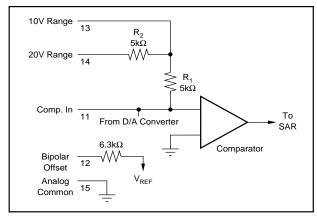

The ADC80 offers five standard input ranges: 0V to +5V, 0V to +10V,  $\pm 2.5V$ ,  $\pm 5V$ , and  $\pm 10V$ . The input range should be scaled as close to the maximum input signal range as possible in order to utilize the maximum signal resolution of the converter. Select the appropriate input range as indicated by Table II. The input circuit architecture is illustrated in Figure 3. External padding resistors can be added to modify the factory-set input ranges (such as addition of a small external input resistor to change the 10V range to a 10.24V range). Alternatively, the gain range of the converter may

| INPUT<br>SIGNAL<br>RANGE | OUTPUT<br>CODE | CONNECT<br>PIN 12<br>TO PIN | CONNECT<br>PIN 14<br>TO | CONNECT<br>INPUT<br>SIGNAL<br>TO |

|--------------------------|----------------|-----------------------------|-------------------------|----------------------------------|

| ±10V                     | COB or CTC     | 11                          | Input Signal            | 14                               |

| ±5V                      | COB or CTC     | 11                          | Open                    | 13                               |

| ±2.5V                    | COB or CTC     | 11                          | Pin 11                  | 13                               |

| 0 to +5V                 | CSB            | 15                          | Pin 11                  | 13                               |

| 0 to +10V                | CSB            | 15                          | Open                    | 13                               |

TABLE II. ADC80 Input Scaling Connections.

FIGURE 3. ADC80 Input Scaling Circuit.

easily be increased a small amount by use of a low temperature coefficient potentiometer in series with the analog input signal or by decreasing the value of the gain adjust series resistor in Figure 5.

#### **CALIBRATION**

#### **Optional External Gain and Offset Adjustments**

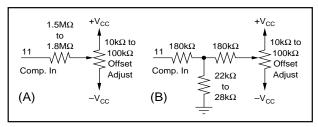

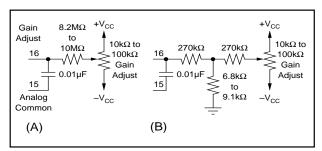

Gain and offset errors may be trimmed to zero using external offset and gain trim potentiometers connected to the ADC80 as shown in Figures 4 and 5 for both unipolar and bipolar operation. Multiturn potentiometers with 100ppm/°C or better TCR are recommended for minimum drift over temperature and time. These pots may be of any value between  $10k\Omega$  and  $100k\Omega$ . All fixed resistors should be 20% carbon or better. Although not necessary in some applications, pin 16 (Gain Adjust) should be preferably bypassed with a  $0.01\mu F$  non-polarized capacitor to analog common to minimize noise pickup at this high impedance point, even if no external adjustment is required.

FIGURE 4. Two Methods of Connecting Optional Offset Adjust.

FIGURE 5. Two Methods of Connecting Optional Gain Adjust.

#### **Adjustment Procedure**

OFFSET—Connect the offset potentiometer as shown in Figure 4. Set the input voltage to the nominal zero or minus full-scale voltage plus 1/2LSB. For example, referring to Table I, this value is -10V + 2.44mV or -9.99756V for the -10V to +10V range.

With the input voltage set as above, adjust the offset potentiometer until an output code is obtained which is alternating between FFE<sub>H</sub> and FFF<sub>H</sub> with approximately 50% occurrence of each of the two codes. In other words, the potentiometer is adjusted until bit 12 (the LSB) indicates a true (logic "0") condition approximately half the time.

GAIN—Connect the gain adjust potentiometer as shown in Figure 5. Set the input voltage to the nominal plus full-scale value minus 3/2LSB. Once again referring to Table I, this value is +10V –7.32mV or +9.99268V for the –10V to +10V range. Adjust the gain potentiometer until the output code is alternating between  $000_{\rm H}$  and  $001_{\rm H}$  with an approximate 50% duty cycle. As in the case of offset adjustment, this procedure sets the converter end-point transitions to a precisely known value.

#### **CLOCK OPTIONS**

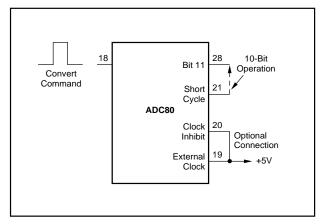

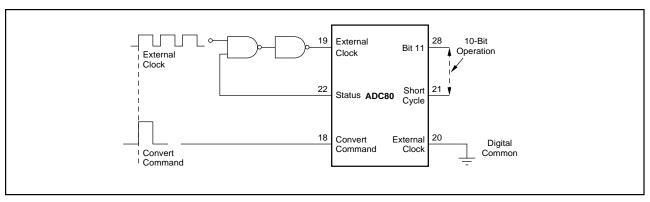

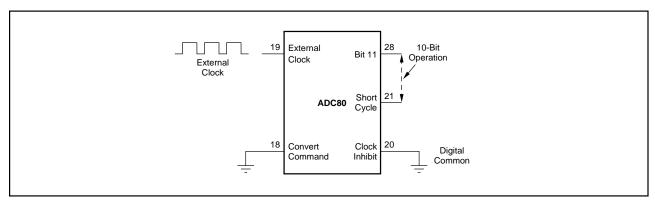

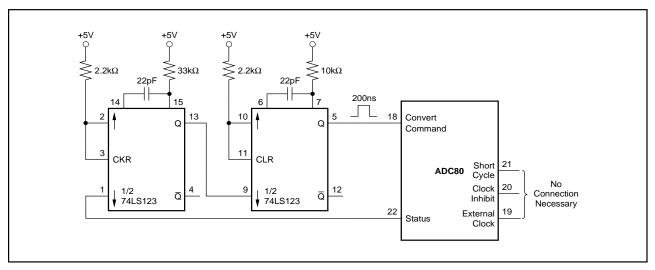

The ADC80 is extremely versatile in that it can be operated in several different modes with either internal or external clock. Most of these options can be implemented with inexpensive TTL logic as shown in Figures 6 through 9. When operating with an external clock, the conversion time may be as short as 15µs (800kHz external clock frequency) with assured performance within specified limits. When operating with the internal clock, pin 19 (external clock input) and pin 20 (clock inhibit) may be left unconnected. No external pull-ups are required due to the inclusion of pull-up resistors in the ADC80. Pin 20 (clock inhibit) must be grounded for use with an external clock, which is applied to pin 19.

FIGURE 6. Internal Clock—Normal Operating Mode. (Conversion initiated by the rising edge of the convert command. The internal clock runs only during conversion.)

FIGURE 7. Continuous External Clock. (Conversion initiated by rising edge of convert command. The convert command must be synchronized with clock.)

FIGURE 8. Continuous Conversion with External Clock. (Conversion is initiated by 14th clock pulse. Clock runs continuously.)

FIGURE 9. Continuous Conversion with 600ns between Conversions. (Circuit insures that conversion will start when power is applied.)

#### **SHORT-CYCLE FEATURE**

A short-cycle input (pin 21) permits the conversion to be terminated after any number of desired bits has been converted, allowing shorter conversion times in applications not requiring full 12-bit resolution. In these situations, the short-cycle pin should be connected to the bit output pin of the next bit after the desired resolution. For example, when 10-

bit resolution is desired, pin 21 is connected to pin 28 (bit 11). In this example, the conversion cycle terminates and status is reset after the bit 10 decision. Short-cycle pin connections and associated maximum 12-, 10-, and 8-bit conversion times (with internal clock) are shown in Table III. Also shown are recommended minimum conversion times (external clock) for these conversion lengths to obtain

the stated accuracies. The ADC80 is not factory-tested for these external clock conversion speeds and the product is not guaranteed to achieve the stated accuracies under these operating conditions; the recommended values are offered as an aid to the user.

| RESOLUTION (Bits)                                              | 12          | 10     | 8      |  |  |

|----------------------------------------------------------------|-------------|--------|--------|--|--|

| Connect pin 21 to                                              | Pin 9 or NC | Pin 28 | Pin 30 |  |  |

| Maximum Conversion Time <sup>(1)</sup> Internal Clock (μs)     | 25          | 22     | 18     |  |  |

| Maximum Conversion Time <sup>(1)</sup><br>External Clock (μs)  | 15          | 13     | 10     |  |  |

| Maximum Linearity Error<br>At +25°C (% of FSR)                 | 0.012       | 0.048  | 0.20   |  |  |

| NOTE: (1) Conversion time to maintain ±1/2LSB linearity error. |             |        |        |  |  |

TABLE III. Short-Cycle Connections and Conversion Times for 8-, 10-, and 12-Bit Resolutions—ADC80.

#### **ENVIRONMENTAL SCREENING**

The inherent reliability of a semiconductor device is controlled by the design, materials, and fabrication of the device—it cannot be improved by testing. However, the use of environmental screening can eliminate the majority of those units which would fail early in their lifetimes (infant mortality) through the application of carefully selected accelerated stress levels. Burr-Brown Q models are environmentally screened versions of our standard industrial products, designed to provide enhanced reliability. The screening illustrated in Table IV is performed to selected methods of MIL-STD-883. Reference to these methods provides a convenient way of communicating the screening levels and basic procedures employed; it does not imply conformance to any other military standards or to any methods of MIL-STD-883 other than those specified. Burr-Brown's detailed procedures may vary slightly, model-to-model, from those in MIL-STD-883.

| SCREEN                                              | MIL-STD-883<br>METHOD<br>CONDITION | SCREENING<br>LEVEL                                                               |

|-----------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------|

| Internal Visual                                     | Burr-Brown<br>QC4118               |                                                                                  |

| High Temperature<br>Storage<br>(Stabilization Bake) | 1008, C                            | 24 hour, +150°C                                                                  |

| Temperature<br>Cycling                              | 1010, C                            | 10 cycles, -65°C<br>to +150°C                                                    |

| Constant Acceleration                               | 2001, A                            | 5000 G                                                                           |

| Electrical Test                                     | Burr-Brown<br>Test Procedure       |                                                                                  |

| Burn-in                                             | 1015, B                            | 160 hr, +125°C<br>Steady-State                                                   |

| Hermeticity:<br>Fine Leak<br>Gross Leak             | 1014, A1 or A2<br>1014, C          | 5 x 10 <sup>-7</sup> atm cc/s<br>Bubble Test Only,<br>Preconditioning<br>Omitted |

| Final Electrical                                    | Burr-Brown<br>Test Procedure       |                                                                                  |

| Final Drift                                         | Burr-Brown<br>Test Procedure       |                                                                                  |

| External Visual                                     | Burr-Brown<br>QC5150               |                                                                                  |

TABLE IV. Screening Flow for ADC80AG-12Q.

ADC80