# **Quickstart Tutorial**

# Table of Contents

## Section 1

| Introducti | on                 | 1-1 |

|------------|--------------------|-----|

| 1.1        | Design Description | 1-1 |

| 1.2        | Design Flow        | 1-2 |

| 1.3        | Expected Results   | 1-2 |

## Section 2

| Step-by-S | Step | Procedure                                | 2-1  |

|-----------|------|------------------------------------------|------|

| 2.1       | Set  | tting Up the Example Files               | 2-1  |

| 2.2       | Ins  | talling ImageCraft <sup>™</sup> Compiler | 2-1  |

| 2.3       | Set  | tting Up the Project                     | 2-2  |

| 2.4       | Adv  | vanced Flow                              | 2-6  |

| 2.5       | Co   | mpiling the AVR Assembly File            | 2-7  |

| 2.6       | Syr  | nthesizing the FPGA file                 | 2-7  |

| 2.7       | AV   | R-FPGA Interface                         | 2-8  |

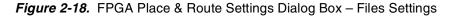

| 2.8       | FP   | GA Place & Route                         | 2-11 |

| 2.9       | Co   | -verification                            | 2-14 |

| 2.9       | 9.1  | Changing the Compiler Tool Settings      | 2-14 |

| 2.9       | 9.2  | Pre-layout<br>Co-verification2-18        |      |

| 2.9       | 9.3  | Post-layout<br>Co-verification2-26       |      |

| 2.9       | 9.4  | Introducing the Delay                    | 2-31 |

| 2.10      | Bit  | Stream Generation                        | 2-32 |

| 2.11      | Ru   | nning the Design                         | 2-35 |

i

Table of Contents

ii

# Section 1

# Introduction

This tutorial is intended for first time users. Software updates can be downloaded from the Atmel web site, at http://www.atmel.com/dyn/products/tools\_card.asp?tool\_id=2752.

When running the FPGA and AVR stand-alone designs, the design must be combined at the end using System Designer. If this method is used, the interface must be clearly defined prior to the design stage, since the FPGA-AVR interface is fixed in silicon.

# **1.1Design**<br/>DescriptionThe design in this tutorial shows the user how to use the switches to invoke different<br/>interrupt service routines.

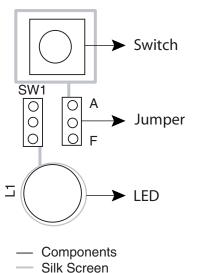

Four switches (SW1 – SW4) are connected to the AVR external interrupts. Pressing the switch will send the signal to an AVR external interrupt. When an interrupt occurs, it jumps to the corresponding program segment (C or Assembly) to execute the code that will be displayed on the LEDs.

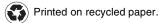

Four switches (SW5 – SW8) are connected to the FPGA I/Os. When the switch is pressed, the signal will be sent to the FPGA interrupt (INTA0 – INTA3). When the AVR receives an interrupt, it will jump to the interrupt service routine and send the load signal to the FPGA to display different characters on the Alphanumeric LEDs. The AVR CLK is connected to the FPGA Global Clock (GCLK 5), see Figure 1-1.

Figure 1-1. FPGA-AVR Connections

Results

| Design Flow | The flow below provides a step-by-step explanation of quickstart_lab:                                                                                                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design now  | <ol> <li>Compile Assembly/C Code: Wavrasm Assembler creates the qs_avr.hex<br/>file. Using ImageCraft Compiler creates the qs_avrim.hex (used for down-<br/>load) and qs_avrim.cof (used for debugging) files.</li> </ol>                    |

|             | <ol> <li>AVR-FPGA Interface: Defines the connections between the embedded FPGA<br/>and AVR Core; qs_fpga.ict is created.</li> </ol>                                                                                                          |

|             | <ol> <li>Pre-layout Co-verification: Pre-layout co-verification provides a simulation of<br/>the FPGA design with the AVR code, including the timing information from the<br/>FPGA.</li> </ol>                                               |

|             | 4. Synthesize VHDL Code: LeonardoSpectrum creates the <code>qs_fpga.edf</code> netlist file. This file is imported into the Figaro Place & Route tool.                                                                                       |

|             | 5. <b>FPGA Place &amp; Route Using Figaro:</b> qs_fpga.edf is imported into Figaro to place and route the design, qs_fpga.bst is created.                                                                                                    |

|             | <ol> <li>Post-layout Co-verification: Post-layout Co-verification provides a simulation of<br/>the FPGA design with the AVR code, including the timing information from the<br/>FPGA targeted to the architecture of your design.</li> </ol> |

| Expected    | There are four patterns that are shown on each set of LEDs depending on the swi                                                                                                                                                              |

There are four patterns that are shown on each set of LEDs depending on the switch pressed, see Table 1-1 and Table 1-2.

Table 1-1. LED Patterns

| Switches | LED         |

|----------|-------------|

| 1        | Count Up    |

| 2        | Count Down  |

| 3        | Knightrider |

| 4        | Bounce      |

#### Table 1-2. Alphanumeric LED Patterns

| Switches | Alphanumeric LED |

|----------|------------------|

| 5        | *                |

| 6        | +                |

| 7        | x                |

| 8        | 0                |

# Section 2

# **Step-by-Step Procedure**

## 2.1 Setting Up the Example Files

The source files for this application note can be found within the c:\SystemDesigner\Examples\AT94K\Coverify\2451.zip file. Alternatively, the source files may be found in the FPSLIC System Designer Software card of the Atmel web site (http://www.atmel.com).

The contents of the zip file are shown in Table 1.

#### Table 1. 2451.zip Contents

| File         | Description                                                                        |  |

|--------------|------------------------------------------------------------------------------------|--|

| qs_fpga.vhd  | VHDL <sup>®</sup> Design File                                                      |  |

| qs_fpga.pin  | FPGA Pin Assignments                                                               |  |

| wave.do      | Command File for Hardware Simulation. This File is not Required for this Tutorial. |  |

| qs_avr.asm   | Assembly File for the AVR Design                                                   |  |

| qs_avrim.c   | C File for ImageCraft Compiler                                                     |  |

| at94kdef.inc | Include File Used with Assembly File                                               |  |

Before starting the tutorial you need to set up a directory for training.

- 1. Create a directory under c:\training\fpslic\lab1.

- 2. Copy 2451.zip to the lab1 directory.

## 2.2 Installing ImageCraft<sup>™</sup> Compiler

- 1. Insert the System Designer CD into the CD-ROM drive.

- 2. From the CD browser go to Install Products and select ImageCraft C Compiler.

The complete version of ImageCraft will run for 30 days after the installation. After the 30 days, it will ask you to register the application. If you do not register the application, ImageCraft can still be used, but it is limited to 2K of code space.

## 2.3 Setting Up the Project

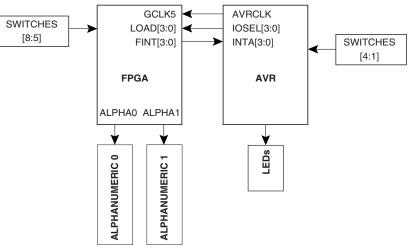

1. Double-click on the System Designer icon on the desktop. System Designer opens, see Figure 2-1.

Figure 2-1. System Designer Window

|                | tmei System Designer (no project)                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Proje          | ect <u>E</u> dit <u>O</u> ptions <u>H</u> elp                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0<br>\$        | Project - no name                                                                       | Part - no part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1<br>1         |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                |                                                                                         | Junna -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| *              |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <i>⊗</i><br>⊠. |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D              |                                                                                         | ATMEL Corporation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                |                                                                                         | The second and the se |

|                |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                | ▼<br>▼                                                                                  | × ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                | Log                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                | Log: Welcome to System Designer product of<br>Log: Select Project->New from the menu to |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                | no project                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

2. Go to the *Project* menu and select *New…* to create a new project. The *New Project Wizard* appears. The *New Project Wizard* allows you to select your project directory, select which part you want to target and set up the design tool flow, see Figure 2-2 to Figure 2-7.

Figure 2-2. New Project Wizard - Step 1 of 6

| 3          | Welcome to the New Project wizard                                                             |

|------------|-----------------------------------------------------------------------------------------------|

| Sist       | The New Project wizard will guide you in the creation of your<br>new System Designer project. |

| ₹~~        | The steps that follow will include:                                                           |

| - <b>三</b> | 1. Creating a project file                                                                    |

| i Co       | 2. Selecting the parts for use with your project                                              |

| DESI       | 3. Selecting the software tool sets<br>for use with each part                                 |

| ם ייסטיי   |                                                                                               |

|            | Cancel < Back Next > Fini                                                                     |

- 3. Press Next >. The Create Project File window opens, see Figure 2-3.

- Figure 2-3. New Project Wizard Step 2 of 6

| New Project Wizard - Step | <sup>2 of 6</sup> ×<br>Create Project File                                                                                 |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 515                       | Select a name and directory path for your new project using the co<br>below. When you are ready, click 'Next' to continue. |

| SYSTEM                    | c ∷training¥pslicVab1Vab1.apj                                                                                              |

|                           | Cancel < Back Next > Finish                                                                                                |

4. Change the directory to c:\training\fpslic\lab1 and name the project lab1.apj. Press *Next* >. The part selection window appears, see Figure 2-4.

Figure 2-4. New Project Wizard - Step 3 of 6

| New Project Wizard - Step 3 | of 6 🛛 🛛 🛛                                                                                                                                                                                                                            |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | What part do you want to use ?                                                                                                                                                                                                        |

| 515                         | Choose a part for your project from the<br>Part Number list below.<br>Architecture: Part Number:                                                                                                                                      |

| SYSTEM<br>DESIGNER          | Any   Any   Product Family:   Any   Any   Any   Any   Package:   Any   Package:   Any   Speed Grade:   Any   Application:   Any |

|                             | Cancel < Back Next > Finish                                                                                                                                                                                                           |

5. Select *AT94K40-25DQC* from the *Part Number* box. This is the part used in the ATSTK94 starter kit.

- 6. Press *Next* >. The software tool flow window appears, see Figure 2-5.

- Figure 2-5. New Project Wizard Step 4 of 6

| New Project Wizard |                                                                                                     | oftware toolflow for this                                                                                                                                                       |

|--------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSTEM<br>DESIGNER | Please select a softwa<br>from the list below.<br>Toolflow:<br><u>Mentor-VHDL</u><br>Mentor-Verilog | are toolset for part U1 : AT94K40-25DQC  Description:  Mentor-VHDL  Tools:  AT94K Device Options  HDL Synthesis Software Compiler  AVR-FPGA Interface Pre-lavout Coverification |

|                    | Cancel                                                                                              | < Back Next > Finish                                                                                                                                                            |

- 7. Select *Mentor-VHDL* from the tool flow box.

- 8. Press Next >. The add more parts window appears, see Figure 2-6.

Figure 2-6. New Project Wizard - Step 5 of 6

| New Project Wizard | Step 5 of 6     Vould you like to add more parts ?     The list below shows the parts you have selected for your project.     If you would like to add more parts, click the add more parts button below.     When you are ready, click 'Next' to continue. |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEM<br>IGNER       | Project Parts:<br>U1:AT94K40-25DQC - Mentor-VHDL                                                                                                                                                                                                            |

| SYS<br>DES         | <ul> <li>Add more parts</li> <li>Done with parts</li> </ul>                                                                                                                                                                                                 |

|                    | Cancel < Back Next > Finish                                                                                                                                                                                                                                 |

It is possible to add multiple parts to work on, but for the purpose of this tutorial only one part will be used.

- 9. Press Next >. The last window of the wizard appears, see Figure 2-7.

- Figure 2-7. New Project Wizard Step 6 of 6

| 🔏 New Project Wizard - | Step 6 of 6                                                                                                                                                                                                      |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Congratulations!                                                                                                                                                                                                 |

| 515                    | You have successfully completed the creation of your new<br>System Designer project.                                                                                                                             |

| Ž~                     | The project tree shows the tools and design files included in your<br>project. Using the vertical toolbar on the side of the tree you can add or<br>delete parts, modify toolflows, or include new design files. |

| GNEF                   | To begin, click on a part in the project tree. This will display the design<br>flow in the part window. Then, click on any button in the design flow to<br>run the associated design tool.                       |

| SYS<br>DESI            | To close the New Project wizard and begin working with your<br>project, click the 'Finish' button.                                                                                                               |

|                        | Cancel < Back Next> Finish                                                                                                                                                                                       |

10. Press *Finish* to exit the wizard.

The project window now contains lab1.apj and the part window displays the part selected, see Figure 2-8.

Figure 2-8. System Designer Window - lab1.apj

Clicking on *more info >>* opens the online help.

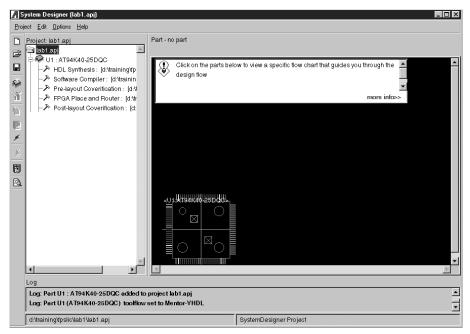

11. Click on the graphic in the part window to display the *Quick Flow View*, see Figure 2-9.

Figure 2-9. Quick Flow View

## 2.4 Advanced Flow

The Advanced Flow view shows the steps available for designing with an FPSLIC device. The arrows on the diagram show the dependencies between the steps, see Figure 2-10.

#### Figure 2-10. Advanced Flow

# 2.5 Compiling the AVR Assembly File For design entry using assembly language refer to the AVR Instruction Set summary in the AT94K series datasheet. The instruction set summary describes the details for each of the supported functions in the FPSLIC.

- 1. Press the SW Compiler button to open wavrasm.

- 2. Go to the File menu and select Open File ...

- 3. Navigate to the correct folder c:\training\fpslic\lab1 and select qs\_avr.asm.

- 4. Go to the Assemble menu and press Assemble. A report window opens.

If successful, close the assembler and return to System Designer.

If the design is not assembled successfully, the message window will display the error messages. Check if at94kdef.inc is missing in your design directory; if this is the case, extract at94kdef.inc from 2451.zip and save it to the lab1 folder.

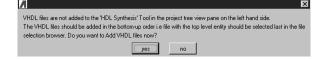

# 2.6 Synthesizing the 1. Press the *Synthesis Tool* button. A dialog box to add VHDL files appears, see FPGA file Figure 2-11.

#### Figure 2-11. Add VHDL Files Dialog Box

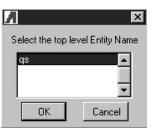

- 2. Press Yes. A file selection window appears.

- 3. Select qs\_fpga.vhd and press OK. LeonardoSpectrum opens, see Figure 2-12

#### Figure 2-12. LeonardoSpectrum

| 🖉 Exemplar Logic - LeonardoSpectrum Level 1 Atmel - [Exemplar Lo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | gic] 📃 🗖 🗶                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>.</u> £5 <u>F</u> ile <u>E</u> dit ⊻iew <u>I</u> ools <u>W</u> indow <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _ <del>_</del> <del>_</del> <del>_</del> <del>_</del>                                                                                                                                                                                                                                                |

| 5 BA A S S Q D F M @                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                      |

| Is     Is     Is     Is     Is       Quick Setup         Run the entire flow from this one condensed page. Specify your source files(s), technology and desired frequency, then press Run Flow.         Technology         Imput         Atmel         Atmel         Atmel         Imput         Rate Road         Atmel         Imput         Road Road         Imput         Imput |                                                                                                                                                                                                                                                                                                      |

| Speed Grade: Vorking Directory:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>@rc:/training/fpslic/labl/gs_fpgs.vhd",line 49:</li> <li>@rc:/training/fpslic/labl/gs_fpgs.vhd",line 56:</li> <li>@rc:/training/fpslic/labl/gs_fpgs.vhd",line 61:</li> <li>@rc:/training/fpslic/labl/gs_fpgs.vhd",line 63:</li> <li>@ Info. Command 'read' tinished successfully</li> </ul> |

| Run Flow Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Transcript Filtered Transcript                                                                                                                                                                                                                                                                       |

| Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Working Directory: c:\training\fpslic Line 42 Col 1                                                                                                                                                                                                                                                  |

- 4. Select *AT94K* as the *Technology*. Leonardo<sup>®</sup> automatically lists <code>qs\_fpga.vhd</code> under input files and lists the output file name <code>asqs\_fpga.edf.qs\_fpga.edf</code> will be imported into Atmel's Place & Route tool (IDS).

- 5. Press the *Run Flow* button. Leonardo shows the successful synthesis, see Figure 2-13.

| Functive entre flow from this one condensed page. Specify your source<br>field, technology and desired frequency, then press Run Flow.       Critical Path Report         Technology       Input       GATE       ARRIVAL         - AT40K       GATE       ARRIVAL         - AT40K       GATE       ARRIVAL         - AT6K02       - AT6K02       fd       0.00 (ideal)         - AT6K02       - AT6K02       fd       0.00 (ideal)         - AT6K02       - AT6K02       0.00 (ideal)       CATHODE dup0(0)/6       LUT2       2.90 7.29 up         CATHODE dup0(0)/6       LUT2       2.90 7.29 up       CATHODE (3)/0       0.00 9.29 up         CATHODE (3)/0       Outpl(3)       obuf /AD       obuf 2.00 9.29 up       CATHODE (3)/0         Constraints       Open files:       Working Directory:       working Directory:       unconstrained path         - Design summary in file 'c:/training/fpslic/labl/qs_fpga.xdb       -       Saving the design database in c:/training/fpslic/labl/qs_fpga.xdb         - Writing XDB version 1999.1       -       Saving the design database in c:/training/fpslic/labl/qs_fpga.xdb         - Virting XDB version 1999.1       -       Saving the design database in c:/training/fpslic/labl/qs_fpga.xdb         - Writing XDB version 1999.1       -       Saving the design database in c:/training/fpslic/labl/qs_fpga.xdb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Quick Setup                                                                                                                 |                           | Exemplar Logic                                                                                                                                                                               | : 100.1 MHz                                                                                                                                     |                                                        |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---|

| Interpretended and based indexed. Index of the present Higher (unconstrained path)         Image: provide index of the present Higher (unconstrained path)         Image: provide index of the present Higher (unconstrained path)         Image: provide index of the present Higher (unconstrained path)         Image: provide index of the present Higher (unconstrained path)         Image: provide index of the present Higher (unconstrained path)         Image: provide index of the present Higher (unconstrained path)         Image: provide index of the present Higher (unconstrained path)         Image: provide index of the present Higher (unconstrained path)         Image: provide index of the path index of the present Higher (unconstrained path)         Image: provide index of the path index of th                                                                                                                                                                                                                                                           | Run the entire flow from this one condensed                                                                                 | d page. Specify your sour |                                                                                                                                                                                              |                                                                                                                                                 |                                                        |   |

| • Atmel         • Atmel         • Attack         • |                                                                                                                             |                           |                                                                                                                                                                                              | icical Fach Report                                                                                                                              |                                                        |   |

| AT40K         AT6K02         AT6K04         AT94K         Olock information not specified         clock information not specified         clock information not specified         Clock information not specified         CATBODE_dap0(0)/6         LUT2       2.90         CATBODE_dap0(0)/6         LUT2       2.90         CATBODE_dap0(0)/6       LUT2         CATBODE_dap0(0)/6       LUT2         CATBODE_dap0(0)/6       LUT2         CATBODE_dap0(0)/6       LUT2         CATBODE_dap0(0)/6       UT2         CATBODE_dap0(0)/7       0.00         CATBODE_dap0(0)/7       0.00         CATBODE_dap0(0)/7       0.00         CATBODE_dap0(0)/7       0.00         Catareourid time       not specified         data arrival time       9.29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                             |                           |                                                                                                                                                                                              |                                                                                                                                                 |                                                        |   |

| ATEXO2         ATEXO4         ATEXO5         ATEXO5         Openide         Openide         Openide         Openide         Openide         Constraints         Openide         Constraints         Openide         Device:         Mthz         Openide         Constraints         Output         Openide         Direc And Route         Contime tand Ro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                             | Jga.vnu                   | NARE                                                                                                                                                                                         | GAIL                                                                                                                                            | ARRIVAL                                                |   |

| AT34K         reg_cToggle/0       fd       0.00       4.39 up         CATHODE (3)/d       LUT2       2.90       7.29 up         CATHODE (3)/d       obsf       2.00       9.29 up         Device:       Image: Constraints       0.00       9.29 up         Constraints       Ming Directory       Ming       0.00       9.29 up         Constraints       0.00       9.29 up       0.00       9.29 up         Constraints       0.00       0.00       9.29 up       0.00       9.29 up         Constraints       0.00       0.00       0.00       0.00       9.29 up       0.00         Output <td></td> <td></td> <td></td> <td>ified</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                             |                           |                                                                                                                                                                                              | ified                                                                                                                                           |                                                        |   |

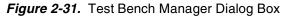

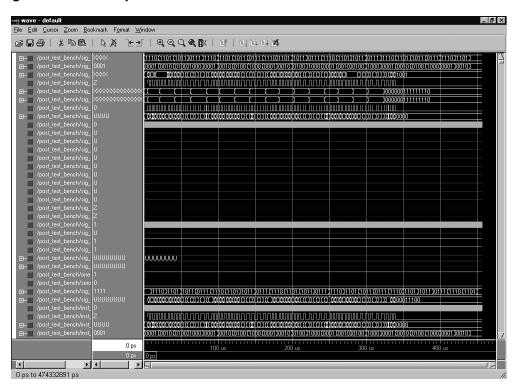

| Period:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                             |                           | delay thru clock network                                                                                                                                                                     |                                                                                                                                                 | 0.00 (ideal)                                           |   |