## High Speed SPI Functional Block for the FPSLIC

## Introduction

The AT94K-AL FPSLIC family includes several hard-wired peripherals. These include UARTs, timers, and a two-wire synchronous serial interface. Another popular interface, not currently implemented in the AT94K-AL, is the SPI synchronous serial interface.

This application note shows how to implement a high-speed SPI with the following features:

- Master only operation

- LSB first or MSB first data transfer

- Seven programmable bit rates

- End of transmission interrupt flag

- 32-byte FIFO on both the transceiver and the receiver

The design uses the internal Dual Port RAM (FreeRAM<sup>TM</sup>) available in the FPGA portion of the AT94 to implement 32-byte FIFOs on both the receiver and the transmitter to maximize throughput.

## Description

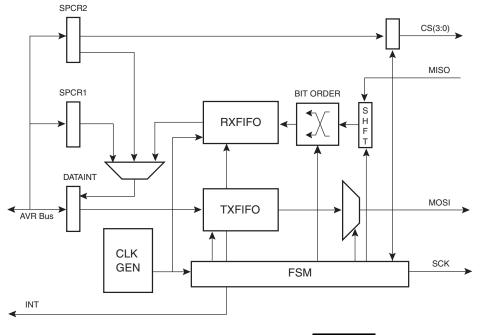

Figure 1 shows the block diagram of the SPI design.

Figure 1. SPI Interface Block Diagram

AT94K Series Field Programmable System Level Integrated Circuit

# Application Note

The AVR<sup>®</sup> programming interface consists of two I/O locations for control purposes and a single data location that is used to transfer data to the transmit FIFO and from the receive FIFO. Both FIFOs provide "empty" and "full" flags which can be tested by the AVR. An interrupt is available and is active whenever the transmit FIFO is empty. The part will automatically generate chip selects for up to four different peripherals. The timing generator allows prescaling the clock to allow a frequency between 2 to 256 times slower than the system clock or between 100 kbps to 12.5 Mbps.

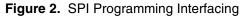

#### **Control Register Bit Definitions**

| SPIE     | SPI Interrupt Enable | When 1, the SPI Interrupt is enabled and will be asserted when the TX FIFO is empty                 |

|----------|----------------------|-----------------------------------------------------------------------------------------------------|

| SPE      | SPI Enable           | When 0, the SPI block is disabled<br>When 1, it shifts as long as the TX FIFO contains data.        |

| DORD     | Data Order           | When 0, the SPI block shifts data MSB first<br>When 1 it shifts data LSB first                      |

| MSTR     | Master/Slave         | When 0, the SPI block is in slave mode (not yet implemented)<br>When 1, it is in master mode        |

| СРНА     | Clock Phase          | See SPI specification or the AT90LS8515 datasheet                                                   |

| CPOL     | Clock Polarity       | See SPI specification or the AT90LS8515 datasheet                                                   |

| SPIF     | Transmit FIFO Empty  | Set to 1 when the transfer is completed                                                             |

| TXF      | Transmit FIFO Full   | Set to 1 when the TX FIFO is full                                                                   |

| RXE      | Receive FIFO Empty   | Set to 1 when the RX FIFO is empty                                                                  |

| RXF      | Receive FIFO Full    | Set to 1 when the RX FIFO is full                                                                   |

| /CS(3:0) | Chip Select Mask     | Set a bit to zero to enable the CS during the transfer<br>Only 1 bit should be set at the same time |

| SPR(2:0) | SPI Prescale         |                                                                                                     |

# <sup>2</sup> High Speed SPI Functional Block for the FPSLI

# **High Speed SPI Functional Block for the FPSLI**

## **File Structure**

The design consists of five files and they should be compiled in the following order:

1. SPI\_config.vhd

Definitions and auxiliary functions

2. Fifo2.vhd

FIFO (same block used for TX and RX)

3. SPI\_timing.vhd

The Clock Prescaler

4. SPI\_transmit.vhd

The Finite State Machine controlling the design Also contains the shift mechanism and bit order handling

5. SPI.vhd

Top level design, control section

## **Entity Port List**

| SPI Interface    |                                    |            |  |

|------------------|------------------------------------|------------|--|

| MISO             | Master In, Slave Out               |            |  |

| MOSI             | Master Out, Slave In               |            |  |

| SCK              | SPI Clock                          |            |  |

| SPI_CS_Z         | SPI Chip Select (3 : 0)            | Active Low |  |

| AVR Interface    |                                    |            |  |

| DOUT             | Connect to AVR ADOUT               |            |  |

| DIN              | Connect to AVR ADIN                |            |  |

| FIORE            | Connect to AVR FIORE               |            |  |

| FIOWR            | Connect to AVR FIOWR               |            |  |

| FIOSEL0          | Connect to AVR FIOSEL0             |            |  |

| FIOSEL4          | Connect to AVR FIOSEL4             |            |  |

| FIOSEL8          | Connect to AVR FIOSEL8             |            |  |

| FIOSEL12         | Connect to AVR FIOSEL12 (not used) |            |  |

| SPI_IRQ          | Connect to AVR INTA0               | Active Low |  |

| System interface |                                    |            |  |

| RESET_Z          | Connect to external RESET signal   | Active Low |  |

| CLOCK            | Connect to FPGA GCLKn              |            |  |

## **Control Section**

The Control Section consists of two registers, CTRL1 and CTRL2. The signals for both CTRL registers reside in the SPCR record, which is passed to all internal blocks (except the FIFOs).

The design uses three chip selects that need to be connected to the AVR in System Designer:

- FIOSEL0 => CTRL1 register

- FIOSEL4 => CTRL2 register

- FIOSEL8 => DATA register

.

For simplicity, they have been named according to the AVR convention in the port list.

While FIOSEL12 is part of the port list, it is not used in the current design.

| FIFO           | The FIFO is 32 by 8 and contains two 6-bit address pointers for read and write pur-<br>poses. They are one bit wider than necessary to simplify the settings of the "full" and<br>"empty" flags. When the lower five bits of the address are equal and the upper bit is also<br>equal, the FIFO is empty. When the lower part is equal and the upper bit is different, the<br>FIFO is full.                                      |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prescaler      | The Prescaler runs at the system frequency, creating an enable signal for the flip-flops in the Finite State Machine controlling the SPI block. The FSM will only update its registers if the enable signal from the prescaler is asserted.                                                                                                                                                                                      |

|                | The enable signal is the carry out from a timer. After each clock cycle, the timer is updated with its previous value incremented by one, and OR'ed with a mask that was generated from the 3-bit SPR prescale configuration bits. The effect of the OR is to reduce the number of clock cycles needed to generate the carry out signal. This can be accomplished by a simple add, but the OR is faster and uses less logic.     |

| Transmitter    | The Transmitter State Machine will monitor the Transmit FIFO empty signal and when-<br>ever this is deasserted (the FIFO contains data), the transmitter will sample the control<br>register and start shifting out data. The shift is implemented by an 8 to 1 multiplexer,<br>where the 3-bit select signal is either first be incremented or de-incremented depending<br>on if the current transmission should be MSB or LSB. |

|                | The transmitter also generates the SPI clock. The Phase and Polarity of the clock is pro-<br>grammable according to normal SPI conventions. The chip select and receive enable<br>signals receive their enable signal from the transmitter FSM.                                                                                                                                                                                  |

| Receiver       | The Receiver is a single shift register running from the system clock. The receive enable signal generated by the Transmit State Machine will control the shift rate.                                                                                                                                                                                                                                                            |

|                | When eight bits of data is shifted in, it gets written to the receive FIFO, possibly getting the bits reversed to handle the MSB/LSB configuration.                                                                                                                                                                                                                                                                              |

| Example Driver | An Example Driver is included in the "driver" directory. This was compiled using the IAR AVR C compiler v1.51C.                                                                                                                                                                                                                                                                                                                  |

### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

### **Atmel Operations**

Memory 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

## Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

**Disclaimer:** Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

© Atmel Corporation 2004. All rights reserved. Atmel<sup>®</sup> and AVR<sup>®</sup> combinations are registered trademarks and FreeRAM<sup>™</sup> and FPSLIC<sup>™</sup> are the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be the trademarks of others.