# FPSLIC on-chip Partial Reconfiguration of the Embedded AT40K FPGA

## Features

- Demonstrates Usage of Built-in FPGA Cache Logic<sup>®</sup> Interface

- Implementation Targeted for FPSLIC<sup>™</sup> Starter Kit

- Full FPGA and AVR<sup>®</sup> Source Code Included

## Description

This example demonstrates the reconfiguration process of the FPGA using the built-in Cache Logic Interface. This example takes a simple AND gate implemented in the FPGA and reconfigures the FPGA Core Cell Look-Up Table (LUT) into an OR gate.

The FPSLIC combined Bitstream file is included for convenience.

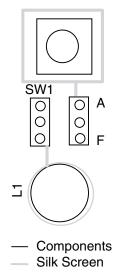

On the FPSLIC Starter Kit, set the jumpers for SW7, SW8 and L1 to the FPGA side, while SW1 is set to the AVR side, see Figure 1. After power-on-reset (POR) from the Configurator, SW7 and SW8 perform the AND function; the result is displayed on L1. Pressing SW1 initiates an External Interrupt 0 to the AVR, which reconfigures the FPGA from the AVR (internally) and writes an OR gate to the FPGA LUT, previously configured as an AND gate. SW7 and SW8 now perform the OR function; the result is displayed on L1.

Figure 1. ATSTK94 Switch/LED Jumper Settings

Programmable SLI AT94K AT94S

# Application Note

Rev. 3013A-FPSLI-01/02

## Implementation

Assuming a default System Designer installation, the source files for this application note can be found at the **\SystemDesigner\Examples\AT94K\Designs\doc3013** folder. Alternatively, the source files may be found in the FPSLIC Software section of the Atmel web site (http://www.atmel.com/atmel/products/prod320.htm). The contents of **doc3013.zip** are shown in Table 1.

Table 1. Contents of doc3013.zip

| File             | Description                               |

|------------------|-------------------------------------------|

| AND.FGD          | Previously Compiled AND Gate Design File  |

| AND.PIN          | FPGA Pin Lock File for FPSLIC Starter Kit |

| AND.VHD          | FPGA Design Source File                   |

| AT94KDEF.INC     | Atmel AVR Assembler FPSLIC Include File   |

| CACHE.ASM        | AVR Design Source File                    |

| FPSLIC_CACHE.BST | FPSLIC Combined Bitstream File            |

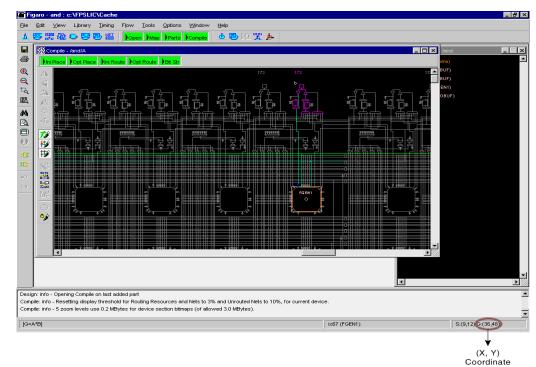

In Figaro, the FPGA Place and Route tool, locate the core cell used to implement the AND gate:

- Go to the **Window** menu and choose **New Compile Window**. The **New Compile** window appears. Use **F7** to zoom in and **F8** to zoom out.

- Place the cursor over the AND gate (on the top edge of the array) to see the (X, Y) coordinates of the core cell location. The coordinates appear on the status bar in the lower right corner of the Figaro window, see Figure 2.

Figure 2. FPGA Place & Route Tool New Compile Window

# **FPSLIC on-chip Partial Reconfiguration**

It is then necessary to subtract one from each of these numbers as the actual Core Cells start at (0, 0) not (1, 1) as Figaro does. This yields, in this example, X = 36 - 1 and Y = 48 - 1.

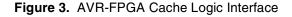

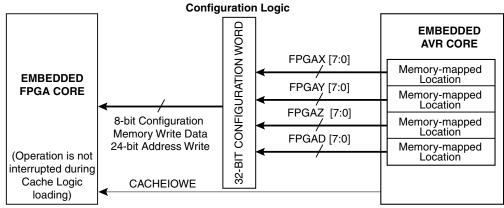

The AVR Assembly file takes the X and Y values and places them in the FPGAX and FPGAY registers, respectively. The FPGAZ and FPGAD values can be obtained from "FPGA Mode 4 Configuration", available under Non-Disclosure Agreement (NDA) from Atmel Corporation. This data is only made available under NDA to protect customers from the reverse engineering of their FPGA designs. The execution of the *out FPGAD, rTemp* instruction initiates the reconfiguration cycle; reconfiguration occurs automatically when the Interrupt Service Routine (ISR) for External Interrupt 0 is executed, see Figure 3.

Configuration Clock – Each tick is generated when the Memorymapped I/O location FPGAD is written to inside the AVR.

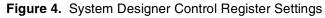

When the combined Bitstream for the FPSLIC is created using System Designer<sup>™</sup>, make sure that System Control Register (SCR) Bit 62 is set. The enabling of this bit allows the FPGA to accept Cache Writes from the AVR via the Cache Logic interface, see Figure 4. An FPGA cell can be reconfigured in a very short time with few instructions.

### **Atmel Headquarters**

*Corporate Headquarters* 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

Europe

Atmel SarL Route des Arsenaux 41 Casa Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

### Japan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

### **Atmel Operations**

Memory Atmel Corporate 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 436-4270 FAX 1(408) 436-4314

Microcontrollers Atmel Corporate 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 436-4270 FAX 1(408) 436-4314

Atmel Nantes La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

ASIC/ASSP/Smart Cards Atmel Rousset Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

Atmel Colorado Springs 1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Atmel Smart Card ICs Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

Atmel Programmable SLI Hotline (408) 436-4119

Atmel Programmable SLI e-mail fpslic@atmel.com

FAQ Available on web site

#### © Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Atmel<sup>®</sup> is a registered trademark of Atmel. FPSLIC<sup>™</sup> and System Designer<sup>™</sup> are the trademarks of Atmel. AVR<sup>®</sup> and Cache Logic<sup>®</sup> are the registered trademarks of Atmel.

Other terms and product names may be trademarks of others

*RF/Automotive* Atmel Heilbronn Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

Atmel Colorado Springs 1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Atmel Grenoble Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

*e-mail* literature@atmel.com

Web Site http://www.atmel.com