### **IP Core Generator: Pulse Generator**

- Pulse Generator Fixed

- Pulse Generator Loadable

- Accessible from the Macro Generator Dialog and HDLPlanner<sup>™</sup> Included in IDS for FPGA Devices and System Designer™ for AT94K FPSLIC™ Devices

- Variable Pitch

- Clock Inversion Capability

- Initialization Polarity Selection

- Fixed Pulse Generator Only

- Variable Output Clock Cycles

- Initialization Radix of Above Value Selection

- Loadable Pulse Generator Only

- Variable Width of Pulse Generator

#### Pulse Generator – Fixed

This can be used to create a pulse generator that asserts its output once every n clock cycles, where *n* is a fixed value specified by the user.

#### **Parameters**

| Parameter                             | Value       | Explanation                                                                                                               |  |

|---------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------|--|

| Generate a Pulse Every n Clock Cycles | Integer > 1 | Output will be low for $n$ - 1 clock cycle, then high for 1 clock cycle, in a repeating pattern                           |  |

| Radix of<br>Above Value               | Binary      | n is specified in binary representation                                                                                   |  |

|                                       | Octal       | n is specified in octal representation                                                                                    |  |

|                                       | Decimal     | n is specified in decimal representation                                                                                  |  |

|                                       | Hex         | n is specified in hexadecimal representation                                                                              |  |

| Pitch                                 | Integer ≥ 1 | Spacing between cells in the pulse generator. A pitch of 2 doubles the size of the generator by spreading out its layout. |  |

| Invert Clock                          | Boolean     | Inverts the clock input                                                                                                   |  |

| Initialization<br>Polarity = Low      | Boolean     | Preset input is active low                                                                                                |  |

## **Programmable** SLI AT40K AT40KAL AT94K

## **Application Note**

#### **Pins**

| Туре | Name     | Option | Explanation                                |  |

|------|----------|--------|--------------------------------------------|--|

| In   | CLK/CLKN | No     | Clock (noninverted/inverted)               |  |

| In   | P/PN     | No     | Preset to starting value (active high/low) |  |

| Out  | TERMONT  | No     | Terminal count (pulse output)              |  |

#### **Statistics**

| Device            | Name  | Speed (MHz) | Delay (ns) | Cells | Size (x * y) |

|-------------------|-------|-------------|------------|-------|--------------|

| AT40K             | pls16 | 133.7       | 7.5        | 5     | 1 x 5        |

| AT40K             | pls8  | 171.5       | 5.8        | 4     | 1 x 4        |

| AT94K/<br>AT40KAL | pls16 | 141.4       | 7.1        | 5     | 1 x 5        |

| AT94K/<br>AT40KAL | pls8  | 171.5       | 5.8        | 4     | 1 x 4        |

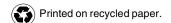

Figure 1 shows an example of the pls16 macro options.

Figure 1. Pulse Generator - Fixed

## IP Core Generator: Pulse Generator

# Pulse Generator – Loadable

This can be used to create a pulse generator that asserts its output once every n clock cycles, where n is a value that is loaded into the macro at run-time. Performing a parallel load operation modifies the value of n, i.e., the pulse frequency.

#### **Parameters**

| Parameter                        | Value       | Explanation                                                                                                                                                       |

|----------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Width                            | Integer > 1 | Width of the pulse generator (i.e., the number of registers it contains). This parameter dictates the maximum size of <i>n</i> that can be loaded into the macro. |

| Pitch                            | Integer ≥ 1 | Spacing between cells in the pulse generator. A pitch of 2 doubles the size of the generator by spreading out its layout.                                         |

| Invert Clock                     | Boolean     | Inverts the clock input                                                                                                                                           |

| Initialization<br>Polarity = Low | Boolean     | Reset input is active low                                                                                                                                         |

#### **Pins**

| Туре | Name              | Option | Explanation                                            |

|------|-------------------|--------|--------------------------------------------------------|

| In   | SLOAD             | No     | 0 = Load pulse frequency value;<br>1 = Generate pulses |

| In   | DATA[Width - 1:0] | No     | Parallel load inputs for pulse frequency value         |

| In   | CLK/CLKN          | No     | Clock (noninverted/inverted)                           |

| In   | R/RN              | No     | Reset (active high/low)                                |

| Out  | TERMCNT           | No     | Terminal count (pulse output)                          |

#### **Statistics**

| Device            | Name  | Speed (MHz) | Delay (ns) | Cells | Size (x * y) |

|-------------------|-------|-------------|------------|-------|--------------|

| AT40K             | pll16 | 20.3        | 49.3       | 48    | 3 x 17       |

| AT40K             | pll8  | 38.6        | 25.9       | 24    | 3 x 9        |

| AT94K/<br>AT40KAL | pll16 | 25.2        | 39.8       | 48    | 3 x 17       |

| AT94K/<br>AT40KAL | pll8  | 47.9        | 20.9       | 24    | 3 x 9        |

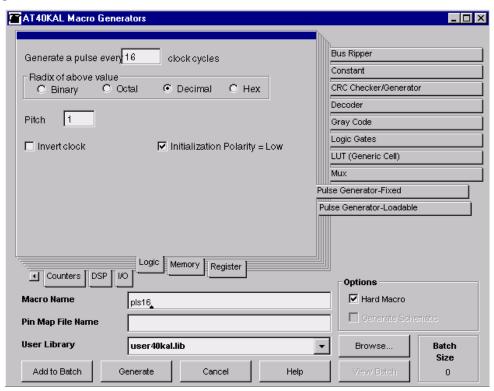

Figure 2 shows an example of the pll16 macro options.

Figure 2. Pulse Generator - Loadable

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

#### Europe

Atmel SarL Route des Arsenaux 41 Casa Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Iapan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Product Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

#### Atmel Grenoble

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-7658-3000 FAX (33) 4-7658-3480

#### Atmel Heilbronn

Theresienstrasse 2 POB 3535 D-74025 Heilbronn, Germany TEL (49) 71 31 67 25 94 FAX (49) 71 31 67 24 23

#### Atmel Nantes

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 0 2 40 18 18 18 FAX (33) 0 2 40 18 19 60

#### Atmel Rousset

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-4253-6000 FAX (33) 4-4253-6001

#### Atmel Smart Card ICs

Scottish Enterprise Technology Park East Kilbride, Scotland G75 0QR TEL (44) 1355-357-000 FAX (44) 1355-242-743

Atmel Programmable SLI Hotline (408) 436-4119

Atmel Programmable SLI e-mail fpga@atmel.com – fpslic@atmel.com

FAQ Available on web site *e-mail* literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2001.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Atmel<sup>®</sup> is the registered trademark of Atmel.  $\mathsf{FPSLIC}^\mathsf{TM}$ ,  $\mathsf{HDLPlanner}^\mathsf{TM}$  and  $\mathsf{System\ Designer}^\mathsf{TM}$  are the trademarks of Atmel.

Other terms and product names may be the trademarks of others.