# **AVR-FPGA Interface Design 1**

### Features

- Initialization and Use of AVR-FPGA Interface and Interrupts

- Full Source Code for AVR® Microcontroller and FPGA Included

## Description

Atmel's AT94K sample designs are provided to familiarize the user with the AT94K FPSLIC<sup>™</sup> device. This design is intended to demonstrate the communication between the AVR and FPGA, utilizing the Data Bus, Interrupts and I/O Select signals.

This design is composed of a simple AVR program and a loadable ripple-carry counter implemented in the FPGA. The counter begins counting at zero upon power-up and will generate an interrupt to the AVR using the ripple-carry out signal. The active low interrupt must be held for three clock cycles prior to being acknowledged by the AVR.

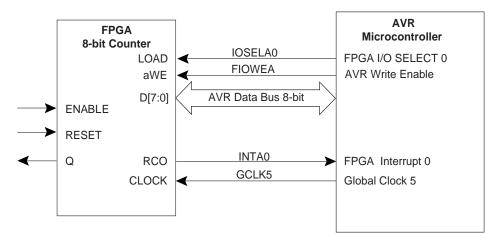

## **Functional Block Diagram**

The block diagram shows the connections used in this example, all interface connections are implemented using dedicated resources. This example makes use of the AVR-FPGA Data Bus, one FPGA Interrupt and one I/O Select signal.

Programmable SLI AT94K

# Application Note

Rev. 2325B-FPSLI-09/27/02

### Implementation

The AVR source of this design has been implemented in C for the CodeVision AVR, IAR Systems and ImageCraft compilers, and in assembly for the Atmel Assembler. The FPGA design has been implemented in Verilog and VHDL. Each file is commented.

Assuming a default System Designer<sup>™</sup> installation, the source files for this application note can be found within the \SystemDesigner\Examples\AT94K\Coverify\doc2325.zip archive. Alternatively, the source files may be found in the FPSLIC Software section of the Atmel web site (http://www.atmel.com), under the doc2325.zip archive. The source files for the Design 1 are shown in Table 1

| File         | Description                              |

|--------------|------------------------------------------|

| AT94KDEF.INC | Atmel AVR Assembler FPSLIC Include File  |

| D1-ATML.ASM  | Atmel AVR Assembler Design 1 Source File |

| D1-CVAVR.C   | CodeVision AVR Design 1 Source File      |

| D1-IAR.C     | IAR Systems Design 1 Source File         |

| D1-ICC.C     | ImageCraft Design 1 Source File          |

| COUNTER.V    | Top-level Verilog Source File            |

| COUNTER.VHD  | Top-level VHDL Source File               |

Table 1. Source Files for Design 1

The top-level HDL source code is COUNTER.V or COUNTER.VHD. The code implements an 8bit loadable ripple-carry counter, which counts from \$00 to \$3F. The counter's ENABLE and RESET lines are active high. The ripple-carry out signal is connected to the AVR Interrupt Signal INTA0.

The file containing the AVR microcontroller source code depends on the programming language and the compiler being targeted, consult the archive contents above to determine the corresponding file to your tool flow. When the AVR senses an interrupt resulting from the counter's ripple-carry out signal, the Interrupt Service Routine (ISR) for INTA0 is executed. During the ISR for INTA0, the AVR increments the count of INTA0 occurrences and places it on the 8-bit AVR-FPGA Data Bus, which triggers the AVR Write Enable (FPGA signal aWE) and FPGA I/O Select 0 (FPGA signal LOAD), and loads the counter with the value from the AVR-FPGA Data Bus.

Once the LOAD and aWE signals are released, the counter will start counting from the loaded value. When it has reached its terminal count value (\$3F), it will drive RCO low and will generate an interrupt to the AVR, causing the ISR to be executed. This operation will then be repeated.

# **AVR-FPGA Interface Design 1**

### Simulation

When performing co-verification simulation using Atmel's System Designer software, it is necessary to provide stimulus for the counter's RESET and ENABLE signals. Listed below is the suggested HDL stimulus that should be added to the test bench:

• For VHDL Design Flows:

stimulus: process

begin

sig\_reset <= '0';

sig\_enable <= '0';

wait for 100 ns;

sig\_reset <= '1';

wait for 100 ns;

sig\_reset <= '0';

sig\_enable <= '1';

wait for 200 us;</pre>

end process stimulus;

For Verilog Design Flows:

```

initial

begin

sig_reset = 1'b0;

sig_enable = 1'b0;

#100 sig_reset = 1'b1;

#100 sig_reset = 1'b1;

#200000;

end

```

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743 **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

Atmel Programmable SLI Hotline (408) 436-4119

Atmel Programmable SLI e-mail fpslic@atmel.com

#### FAQ

Available on web site

#### © Atmel Corporation 2001.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL<sup>®</sup> and AVR<sup>®</sup> are the registered trademarks of Atmel; FPSLIC<sup>™</sup> and System Designer<sup>™</sup> are the trademarks of Atmel.

Other terms and product names may be the trademarks of others.

literature@atmel.com

e-mail

Web Site http://www.atmel.com