Configuration is the process by which a design is loaded into an AT94K Field Programmable System Level Integrated Circuit (FPSLIC<sup>™</sup>) device. AT94K Series devices are SRAM based and can be configured any number of times. The entire device or select portions can be configured. Sections can be configured while others continue to operate undisturbed. Full configuration takes only milliseconds. Partial configuration takes even less time and is a function of design density.

## **Configuration Modes**

The FPSLIC configuration process involves configuring the FPGA, the FPSLIC (AVR<sup>®</sup>) program code and the FPSLIC data memory. This configuration requires a single bitstream that configures the FPGA, the FPSLIC (AVR) Program SRAM and the FPSLIC Data SRAM. The combined bitstream is automatically generated by the Bitstream Generator, a System Designer<sup>™</sup> software utility.

The Bitstream Generator takes the output from the FPGA place and route software and the AVR compiler, and generates a single programming file that will program the FPSLIC device by loading the programming code and the configuration memory. The FPSLIC will automatically read out of a configuration memory on power-up. The programming code can also be serially loaded into the FPSLIC device from another microprocessor or downloaded from a PC.

The configuration programming code is transferred to the device in one of three modes (see Table 1). Two dedicated input pins,  $M_0$  and  $M_2$ , determine the configuration mode. There is one auto-configuring Master mode, one Slave mode and a Synchronous RAM mode for accessing the SRAM-based configuration memory directly from a parallel microprocessor port.

| Table 1. AT94K Series Cont | figuration Modes |

|----------------------------|------------------|

|----------------------------|------------------|

| Mode | Description             | M2 | MO | Clock  | Data       | Notes                                                    |

|------|-------------------------|----|----|--------|------------|----------------------------------------------------------|

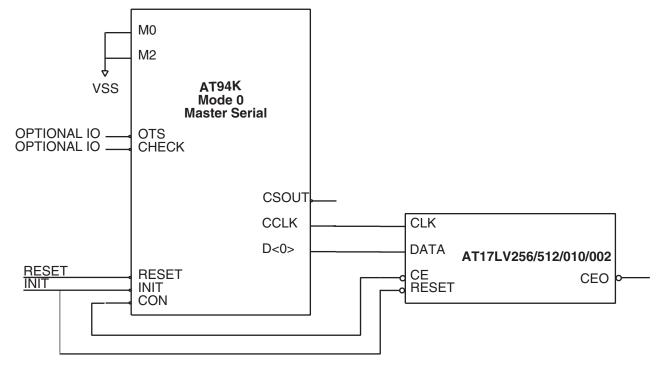

| 0    | Master Serial           | 0  | 0  | Output | Serial     | Auto Configuration,<br>Serial EEPROM                     |

| 1    | Slave Serial<br>Cascade | 0  | 1  | Input  | Serial     | Microprocessor or<br>Serial EEPROM                       |

| 4    | Synchronous<br>RAM      | 1  | 0  | Input  | 8-bit Word | 24-bit Address In,<br>Parallel Port of<br>Microprocessor |

AT94K Series Field Programmable System Level Integrated Circuit

## Application Note

## AIMEL

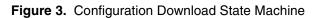

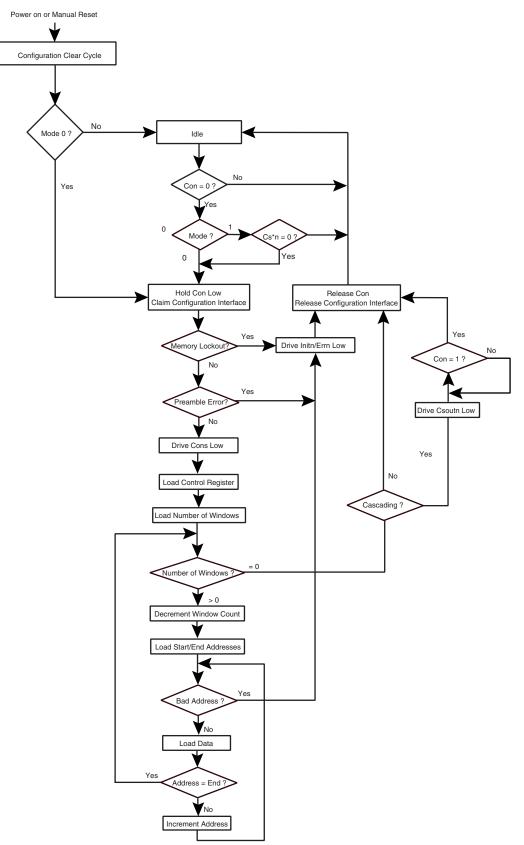

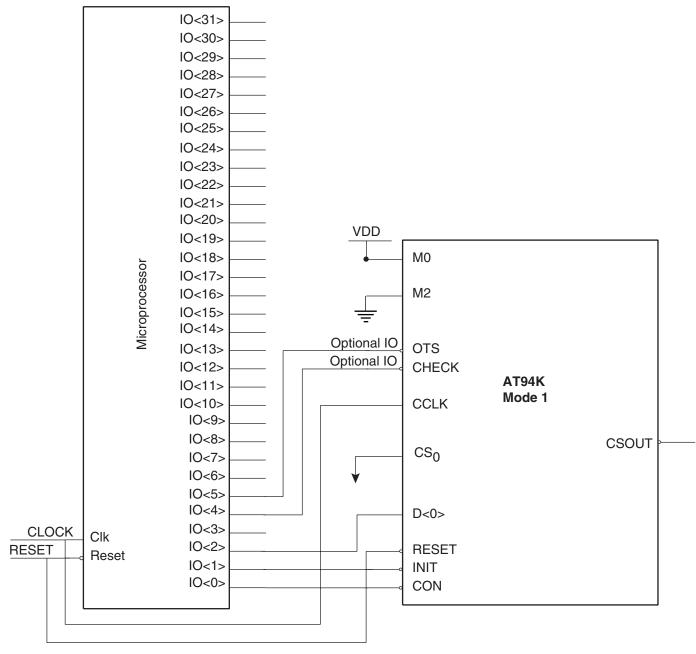

| Master Mode          | The Master mode is auto-configuring: after reset and the internal clearing of configura-<br>tion memory, the FPSLIC device self-initiates configuration. The Master mode uses an<br>internal oscillator to provide CCLK for clocking the external EEPROMs (configurators)<br>which contain a configuration data. CCLK will also drive a downstream device (Slave) in<br>The Master Serial mode clocks and receives data from a EEPROM Serial Configuration<br>Memory (AT17C/LV512, AT17C/LV010). After auto-configuration is complete, reconfig-<br>uration can be initiated manually by the user, if needed. |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

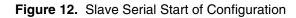

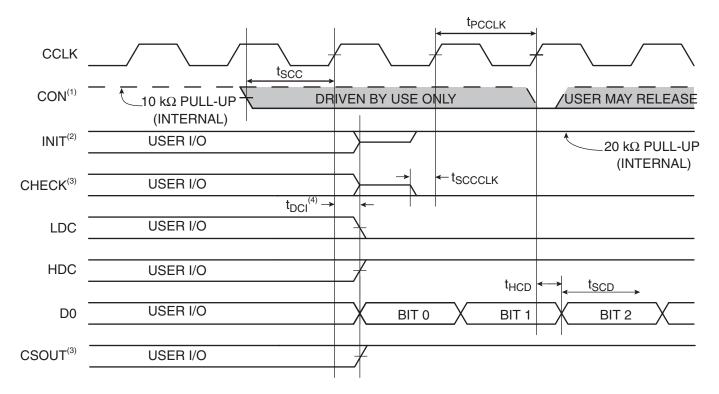

| Slave Mode           | In Slave mode, configuration is always initiated by an external source. Data is applied to the device on the rising edge of CCLK. In Slave mode, the device receives serial configuration data. CCLK is not generated in Slave mode.                                                                                                                                                                                                                                                                                                                                                                          |

| Synchronous RAM Mode | In Synchronous RAM mode, the device receives a 32-bit wide bitstream composed of a 24-bit address and 8-bit wide data. Address, data and write enable are applied simultaneously at the rising edge of CCLK. In this mode the FPSLIC configuration SRAM is seen as a simple memory mapped address space. The user has full write and limited read access to the entire FPSLIC configuration SRAM. The overhead normally associated with bitstreams is eliminated, resulting in faster (re)configuration.                                                                                                      |

| Configuration Pins   | There are four basic configuration states of operation. Power-on-reset, occurs when power is first applied to the part. The FPSLIC initiates a complete clearing of all internal configuration SRAM (configuration clear cycle).                                                                                                                                                                                                                                                                                                                                                                              |

|                      | The second state, manual reset, occurs when the RESET pin is driven low by the user.<br>Again, the FPSLIC initiates a configuration clear cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                      | The third state is configuration download. In this state the configuration mode is active.<br>The FPSLIC accepts serial or parallel data from an outside source and loads the config-<br>uration SRAM appropriately.                                                                                                                                                                                                                                                                                                                                                                                          |

|                      | The fourth state is idle, when there is no configuration activity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                      | During configuration, the flow of the programming code to and from the device is con-<br>trolled by the dedicated mode pins and a number of dual-function pins that double as<br>user I/O (FPGA) under normal programmed operation. The number of dual-function pins<br>required for each mode varies (see Table 2).                                                                                                                                                                                                                                                                                          |

|                      | The mode pins are dedicated TTL threshold inputs that determine the configuration mode to be used. Table 2 lists the states for each configuration mode. The mode pins should not be changed during power-on-reset, manual reset or configuration download. The user may change the mode pins during configuration idle. These pins have no pull-up resistors to VDD, so they need to be driven by the user, tied off or pulled up/down automatically.                                                                                                                                                        |

| Table 2. | Configuration | Pins | Interface | Definition |

|----------|---------------|------|-----------|------------|

|----------|---------------|------|-----------|------------|

|                     | State                                              |                                                          |                                                        |                                                        |                                                |                                                |  |  |

|---------------------|----------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|------------------------------------------------|------------------------------------------------|--|--|

|                     | Download                                           |                                                          |                                                        |                                                        |                                                |                                                |  |  |

| Pins                | Manual Reset                                       | Power-on-<br>Reset                                       | Download<br>Mode 0                                     | Download<br>Mode 1                                     | Download<br>Mode 4                             | Idle                                           |  |  |

| $M_{0,}M_{2}$       | TTL Input                                          | TTL Input                                                | TTL Input                                              | TTL Input                                              | TTL Input                                      | TTL Input                                      |  |  |

| RESET               | TTL Input,<br>50 kΩ Pull-up                        | TTL Input,<br>50 k $\Omega$ Pull-up                      | TTL Input,<br>50 kΩ Pull-up                            | TTL Input,<br>50 k $\Omega$ Pull-up                    | TTL Input, 50 k $\Omega$ Pull-up               | TTL Input,<br>50 kΩ Pull-up                    |  |  |

| INIT                | Open Drain<br>Bi-directional,<br>20 kΩ Pull-up     | Open Drain<br>Bi-directional,<br>20 k $\Omega$ Pull-down | Open Drain<br>Bi-directional,<br>20 k $\Omega$ Pull-up | Open Drain<br>Bi-directional,<br>20 k $\Omega$ Pull-up | Open Drain<br>Bi-directional,<br>20 kΩ Pull-up | User I/O                                       |  |  |

| CON                 | Open Drain<br>Bi-directional,<br>10 kΩ Pull-up     | Open Drain<br>Bi-directional,<br>10 k $\Omega$ Pull-up   | Open Drain<br>Bi-directional,<br>10 k $\Omega$ Pull-up | Open Drain<br>Bi-directional,<br>10 k $\Omega$ Pull-up | Open Drain<br>Bi-directional,<br>10 kΩ Pull-up | Open Drain<br>Bi-directional,<br>10 kΩ Pull-up |  |  |

| CCLK                | Schmitt<br>Trigger Input,<br>50 k $\Omega$ Pull-up | Schmitt<br>Trigger Input,<br>50 k $\Omega$ Pull-down     | Output                                                 | Schmitt<br>Trigger Input,<br>50 k $\Omega$ Pull-up     | Schmitt<br>Trigger Input,<br>50 kΩ Pull-up     | Schmitt<br>Trigger Input,<br>50 kΩ Pull-up     |  |  |

| HDC                 | Output                                             | Input<br>Pull-down                                       | Output                                                 | Output                                                 | User I/O                                       | User I/O                                       |  |  |

| LDC                 | Output                                             | Input<br>Pull-down                                       | Output                                                 | Output                                                 | User I/O                                       | User I/O                                       |  |  |

| D <sub>0</sub>      | CMOS<br>Input, 20 kΩ<br>Pull-up                    | CMOS<br>Input, 20 kΩ<br>Pull-up                          | CMOS<br>Input, 20 kΩ<br>Pull-up                        | CMOS<br>Input, 20 kΩ<br>Pull-up                        | CMOS<br>Input, 20 kΩ<br>Pull-up                | CMOS<br>Input, 20 kΩ<br>Pull-up                |  |  |

| TD <sub>(7:0)</sub> | CMOS<br>Input, 20 kΩ<br>Pull-up                    | CMOS<br>Input, 20 kΩ<br>Pull-down                        | User I/O                                               | User I/O                                               | Bi-directional                                 | User I/O                                       |  |  |

| A <sub>(29:0)</sub> | CMOS<br>Input, 20 kΩ<br>Pull-up                    | CMOS<br>Input, 20 kΩ<br>Pull-down                        | User I/O                                               | User I/O                                               | Input                                          | User I/O                                       |  |  |

| CS0                 | CMOS<br>Input, 20 kΩ<br>Pull-up                    | CMOS<br>Input, 20 kΩ<br>Pull-down                        | CMOS<br>Input, 20 kΩ<br>Pull-up                        | CMOS<br>Input, 20 kΩ<br>Pull-up                        | CMOS<br>Input, 20 kΩ<br>Pull-up                | CMOS<br>Input, 20 kΩ<br>Pull-up                |  |  |

| CSOUT               | CMOS<br>Input, 20 kΩ<br>Pull-up                    | CMOS<br>Input, 20 kΩ<br>Pull-down                        | Optional Output                                        | Optional<br>Output                                     | AVR WTP3<br>Input, 20 kΩ<br>Pull-up            | AVR WTP3<br>Input, 20 kΩ<br>Pull-up            |  |  |

| CHECK               | CMOS<br>Input, 20 kΩ<br>Pull-up                    | CMOS<br>Input, 20 kΩ<br>Pull-down                        | Check Input                                            | Check Input                                            | Check Input                                    | User I/O                                       |  |  |

| OTS                 | CMOS<br>Input, 20 kΩ<br>Pull-up                    | CMOS<br>Input, 20 kΩ<br>Pull-down                        | OTS Input<br>or User I/O                               | OTS Input<br>or User I/O                               | OTS Input<br>or User I/O                       | OTS Input<br>or User I/O                       |  |  |

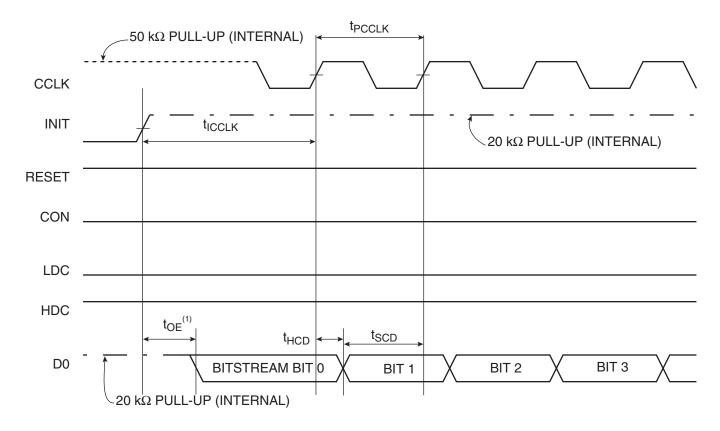

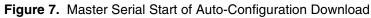

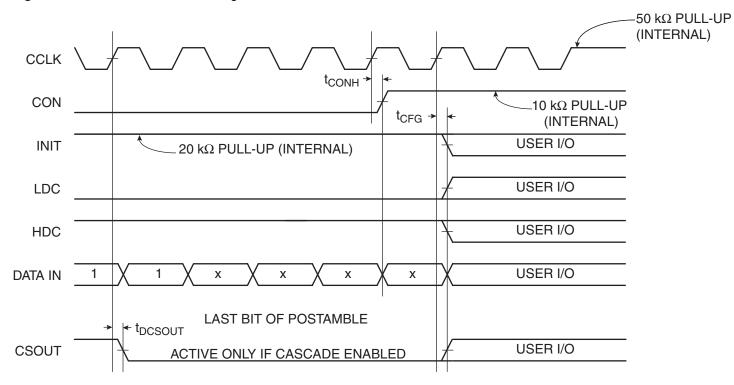

| CCLK  | CCLK is the configuration clock pin. It is an input or an output depending on the mode of operation. During power-on-reset or manual reset, it is a tri-stated output. During configuration download in Mode 0, it is an output with a nominal frequency of 1 MHz. During configuration download in all other modes, it is a Schmitt trigger input. It is an input during configuration idle, but is ignored. It is pulled to VDD with a nominal 50 k $\Omega$ internal resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET | RESET is the FPSLIC manual reset pin. It is available during all configuration states. It initiates a configuration clear cycle and, if operating in Mode 0, an auto-configuration. It is a dedicated Schmitt trigger. It is pulled to VDD with a nominal 50 k $\Omega$ internal resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| INIT  | INIT is a multi-function pin. During power-on-reset and manual reset, the pin functions as an open drain bi-directional I/O which releases high when the configuration clear cycle is complete, but can be held low during reset to hold the device in a reset state. Once released, the FPSLIC will proceed to either configuration download or idle, as appropriate. During configuration download, the INIT pin is again an open drain bi-directional pin which signals if an error (driven low) is encountered during the download of a configuration bitstream. In addition, during the Check Function, the INIT pin drives low for any configuration SRAM mismatch (see the description of the Check Function on page 21 for more details). While in open drain mode, the pin is pulled to VDD with a nominal 20 k $\Omega$ internal resistor. When not configuring, the INIT pin becomes a fully functional user I/O.                                                                                                                                                                                |

| CON   | CON is the FPSLIC configuration start and status pin. It is a dedicated open drain bi-<br>directional pin. During power-on-reset or manual reset, CON is driven low by the<br>FPSLIC. In Slave Modes 1 or 4, when the FPSLIC has finished the configuration clear<br>cycle, CON is released to indicate the device is ready for a configuration download. The<br>user may then drive CON low to initiate a configuration download. After three clock<br>cycles when the preamble has been recognized, CON is then driven low by the FPSLIC<br>until it finishes the download, and it is then released. In Mode 0, CON is not released by<br>the FPSLIC at the end of power-on-reset or manual reset. Instead, CON is controlled by<br>the FPSLIC until the end of the auto-configuration process. CON is released at the end<br>of configuration download in Mode 0, and the user may then leave the device in Mode 0<br>or change the mode and initiate a configuration download by driving CON low. While in<br>open drain mode, the pin is pulled to VDD with a nominal 10 k $\Omega$ internal resistor. |

| HDC   | <ul> <li>HDC is the FPSLIC high during configuration pin. It is an output driven high by the FPSLIC during manual reset and configuration download. During configuration idle, the pin is a fully functional user I/O. During power-on-reset, HDC is an input with a normal 20 kΩ internal pull-down resistor.</li> <li>Note: All user I/O default to inputs with pull-ups "on". The HDC pin transitions from driving a strong "1" to a pull-up "1" after manual reset. The HDC pin will transition from driving a strong "1" to the user programmed state at the end of configuration download. If it is not programmed, the default state is input with pull-up.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LDC                              | LDC is the FPSLIC low during configuration pin. It is an output, driven low by the FPSLIC during manual reset and configuration download. During configuration idle, the pin is a fully functional user I/O. During power-on-reset, LDC is an input pull-down with a nominal 20 k $\Omega$ internal pull-down resistor.<br>Note: All user I/O pull-ups and pull-downs are programmed by the user. The LDC pin transi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | tions from driving a strong "0" to a weak "1" after reset. The LDC pin will transition from<br>driving a strong "0" to the user programmed state at the end of configuration download. If<br>it is not programmed, the default state is input with pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| D <sub>0</sub>                   | $D_0$ is the FPSLIC configuration data line used to download configuration data to the device. The $D_0$ is a dedicated CMOS input with a nominal 20 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TD <sub>0</sub> :TD <sub>7</sub> | $TD_0:TD_7$ are the 8 bits of the parallel data bus used in Synchronous RAM mode to download configuration data to the device. During manual reset, $TD_0:TD_7$ are controlled by the configuration SRAM. The $TD_0:TD_7$ pins will transition from the user programmed state to CMOS inputs with nominal 20 k $\Omega$ internal pull-up resistors as the SRAM at those locations is cleared by the configuration clear cycle. During power-on-reset, $TD_0:TD_7$ are inputs with nominal 20 k $\Omega$ internal pull-down resistors switching to nominal 20 k $\Omega$ internal pull-up resistors at the end of the configuration clear cycle. $TD_0:TD_7$ are not used in the serial Modes 0 and 1.                                                                                                                                                                                                            |

| A <sub>0</sub> :A <sub>29</sub>  | $A_0:A_{29}$ are used to control the FPSLIC configuration SRAM, the Data SRAM, and the AVR Program SRAM addressing in Mode 4 configuration downloads. During manual reset, $A_0:A_{29}$ are controlled by the configuration SRAM. The $A_0:A_{29}$ pins will transition from the user programmed state to CMOS inputs with nominal 20 k $\Omega$ internal pull-up resistors as the SRAM at those locations is cleared by the configuration clear cycle. $A_0:A_{29}$ are used only in Mode 4 Synchronous RAM mode. During power-on-reset, $A_0:A_{29}$ are inputs with nominal 20 k $\Omega$ internal pull-down resistors switching to nominal 20 k $\Omega$ internal pull-up resistors at the end of the configuration clear cycle. Bits $A_{24}:A_{29}$ are for future memory expansion and are consistently ignored.                                                                                          |

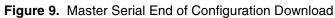

| CS <sub>0</sub>                  | $\rm CS_0$ is an FPSLIC configuration chip select. It is active low. The $\rm CS_0$ pin is dedicated to a CMOS input with a nominal 20 k $\Omega$ internal pull-up resistor. In Mode 1, it is used as a chip select to enable configuration to begin. It is most often used as the chip select of the downstream device in a cascade chain, and is usually driven by CSOUT of the upstream device. Releasing CS_0 during configuration causes the Mode 1 FPSLIC to abort the download and release CON. $\rm CS_0$ is used only in Mode 1.                                                                                                                                                                                                                                                                                                                                                                        |

| CSOUT                            | CSOUT is the configuration pin used to enable the downstream device in a cascade chain. During configuration download, CSOUT becomes an optional output. It is enabled by default after reset, and may be enabled or disabled via the configuration control register. If the user has disabled the cascade function, control of CSOUT is turned over to the AVR (INTP3.) If the cascade function is enabled, the CSOUT pin is driven high at the start of configuration download. At the end of the device's portion of the cascade bitstream, the CSOUT pin is driven low (and into the CS <sub>0</sub> of the downstream device) to enable the downstream device. CSOUT is released by the device at the end of the cascade bitstream and becomes a fully functional user I/O. Note: AVR I/O default to inputs with nominal 20 k $\Omega$ internal pull-up resistors following manual reset or power-on-reset. |

## AIMEL

| CHECK        | CHECK is a configuration control pin used to control the Check Function. The Check Function takes a bitstream and compares it to the contents of a previously loaded bitstream and notifies the user of any differences. Any differences causes the INIT pin to go low. During configuration download, CHECK becomes an optional input. It is enabled by default after reset, and may be enabled or disabled via the configuration control register. If the user has disabled the Check Function, is turned over to the AVR (PE7 - PortE, bit 7).<br>Note: AVR I/O default to inputs with nominal 20 k $\Omega$ internal pull-up resistors following manual                                                                                                                                                                                                               |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | reset or power-on-reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| OTS          | OTS is an input pin used to immediately tri-state all user I/O. It is enabled by a bit in the configuration control register. Once activated in the configuration control register, it is always an input. The OTS tri-state control of Dual Use pins is superseded by the configuration logic's claim on those pins. If the user has disabled the OTS function, the pin remains as User I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

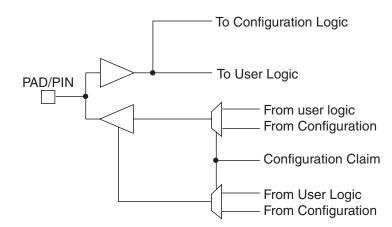

| Dual Use I/O | Any pin which functions as user I/O and configuration I/O is a Dual Use I/O pin. INIT, HDC, LDC, $TD_0$ : $TD_7$ , $A_0$ : $A_{29}$ , CSOUT, CHECK, and OTS are all Dual Use I/O pins. It must be noted that while the configuration logic controls Dual Use I/O pins during a particular mode of operation, the configuration logic does not control the pull-up, pull-down, CMOS/TTL threshold select or Schmitt trigger selects. The user must be cautioned to avoid possible system problems with the use of Dual Use I/O pins. For example, turning off the internal pull-up resistor for the open drain INIT pin would not apply the weak high required of an open drain driver. Conversely, disabling the pull-up and enabling the pull-down of the HDC pin might be a good idea, since the user may then actually see the pin go low at the end of configuration. |

|              | Dual Use pins share input buffers. It should be noted that even when the configuration has claimed a pin for its own purposes, the user input buffer is still fully functional. This implies that any internal user logic tied to the input buffers of the pins in question will remain operational (see Figure 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Figure 1. Dual Use IO

## **Configuration States**

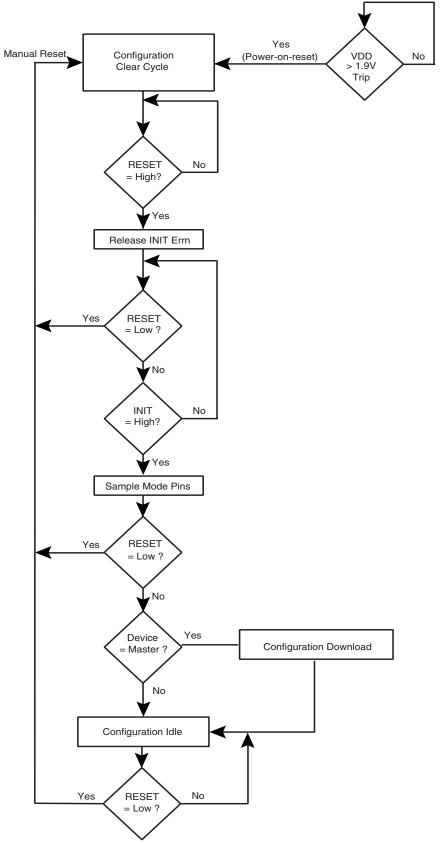

When power is first applied to an AT94K Series FPSLIC device, an internal power-onreset circuit senses VDD and activates at approximately 1.9V. The FPSLIC then enters the power-on-reset state. During this state, INIT is pulled low, CON is driven low, LDC is pulled low (input), HDC is pulled low (input), and all user I/O are tri-stated pulled low. I/O thresholds are at an indeterminate state. The FPSLIC configuration clear cycle begins and the configuration SRAM is reset. The configuration clear cycle is repeated a nominal 150 ms to allow VDD to rise to the minimum operational level for the device.

This additional delay is only applied at power-on-reset, (not required for manual reset.)

Once the configuration clear cycle is complete, INIT is driven low, CON remains driven low, LDC is driven low (output), HDC is driven high (output) and all user I/O are tri-stated (input) and pulled high; then RESET is sampled. If high, INIT is released. This open drain pin is sampled to make sure all other devices (if any) in a cascade chain are also done with the configuration clear cycle. Once INIT goes high the mode pins are sampled.

If Mode 0 is detected, the part proceeds to the configuration download state. CON is held low by the FPSLIC, HDC remains high, LDC remains low and CCLK is now driven by the FPSLIC at a nominal frequency of approximately 1 MHz. The appropriate configuration interface pins for Mode 0 become active.

If a Slave mode is detected (i.e., Mode 1), then CON is released and pulled high with the internal pull-up resistor. Once CON goes high, the part proceeds to the idle state and LDC and HDC are released. The internal oscillator stops running. The part is now available for configuration download.

When RESET is lowered, the manual reset state is entered. An internal oscillator begins running, INIT is driven low, CON is driven low, LDC is driven low and HDC is driven high. During this state, the FPSLIC configuration clear cycle begins and the configuration SRAM is reset. All user I/O, will transition from their user programmed state to a CMOS input with nominal 20 k $\Omega$  internal pull-up resistor as the SRAM at that location is cleared. Once this cycle is complete, RESET is sampled and the reset state machine proceeds as above. The configuration reset state diagram is shown in Figure 2.

After a configuration clear cycle, the user logic in the FPGA array of the FPSLIC is set to a benign state. The following chart shows the various types of user circuitry and their default states.

There is no activity in either the user logic or the configuration logic and the device is in a low power state.

|         | FPGA Array | FPGA SRAM | Clear Cycle Time |     |      |       |

|---------|------------|-----------|------------------|-----|------|-------|

| Device  | Size       | Size      | Min              | Тур | Max  | Units |

| AT94K05 | 16 x 16    | 2048      | 137              | 228 | 365  | μs    |

| AT94K10 | 24 x 24    | 4096      | 197              | 328 | 525  | μs    |

| AT94K40 | 48 x 48    | 18432     | 377              | 628 | 1005 | μs    |

Table 3. Configuration Clear Cycle Times

| User Circuitry       | Default State                                                                 |

|----------------------|-------------------------------------------------------------------------------|

| Core                 | Inputs Tied Off<br>Local Drivers Off<br>DFF Set                               |

| Repeater             | All Drivers Off<br>Passgates Off                                              |

| I/O                  | Output Drivers Off<br>CMOS Threshold<br>Pull-up Enabled<br>Pull-down Disabled |

| Clocks               | Tied High                                                                     |

| Resets               | Tied Low (Active)                                                             |

| FreeRAM <sup>™</sup> | Disabled<br>Contents Cleared                                                  |

Table 4.

User Circuitry and Default States

The AT94K FPSLIC allows complete reconfigurability down to the byte level. The Cache Logic<sup>®</sup> architecture lets users reconfigure part of the FPSLIC while the rest of the FPSLIC continues to operate unaffected.

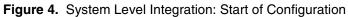

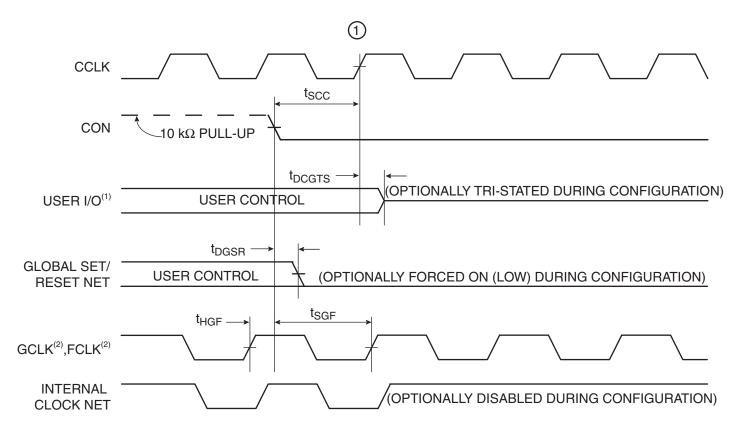

Control of the FPSLIC system level interface is possible on an AT94K Series FPSLIC. User I/O, internal Global Set/Reset, and Global and Fast Clocks can be enabled or disabled during configuration downloads by setting bits in the system control register (SCR.)

User I/O become active as soon as the relevant I/O configuration SRAM is loaded. To aid system level integration, a bit in the system control register ( $SCR_{31}$ ) may be set to command all I/O pins that are not part of the configuration interface to tri-state. This bit is set at the start of configuration so the very first download can be affected.

Another bit in the system control register ( $SCR_{30}$ ) may be set to enable (drive low) the global reset net during configuration download, allowing the user to post all configured logic into a known state.

Another set of bits in the system control register ( $SCR_{25}$ : $SCR_{16}$ ) may be set to disable (drive high) each of the Global and Fast Clock input buffers which drive the FPGA clock nets. The user I/O portion of these buffers is not affected.

| Holding off Auto-<br>configuration | There are two methods by which the user may delay a master Mode 0 auto-configuration. The first is to drive RESET low during power-on-reset or manual reset and hold the signal low until the user is ready to proceed with auto-configuration. The second is to drive INIT low with an open drain driver during power-on-reset or manual reset and release when the user is ready to proceed with auto-configuration. Both are valid in a AT94K Series device. Assuming the device has completed its configuration clear cycle and that INIT and RESET are inactive (high), a Mode 0 FPSLIC starts CCLK and configuration download. |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

System Control The first 4 bytes of the 8-byte System Control Register (bits SCR[31:0]) are set in the header portion of the bitstream. The remaining 4 bytes (bits SCR[63:32]) must be set in Register a bitstream window. Each 4-byte block is treated separately by the configuration logic so the System Control Register has been broken down into two tables, see Table 5 and Table 6. The System Designer software allows to set the system control register in the bitstream utilities.

Figure 2. Configuration Reset State Diagram

**AT94K Series Configuration**

| SCR Bit | Scope                        | Comment                                                |

|---------|------------------------------|--------------------------------------------------------|

| 31      | I/O Tri-state                | 1 = I/O Tri-state Active During Configuration          |

| 30      | Global Set/Reset             | 1 = Global Set/Reset (active low) During Configuration |

| 29      | AVR Real Time Monitor        | 1 = Enable AVR Real Time Monitor                       |

| 28      | Reserved                     |                                                        |

| 27      | Reserved                     |                                                        |

| 26      | Reserved                     |                                                        |

| 25      | Fast Clock 1                 | 1 = Fast Clock 1 Disabled During Configuration         |

| 24      | Fast Clock 0                 | 1 = Fast Clock 0 Disabled During Configuration         |

| 23      | Global Clock 8               | 1 = Disabled During Configuration                      |

| 22      | Global Clock 7               | 1 = Disabled During Configuration                      |

| 21      | Global Clock 6               | 1 = Disabled During Configuration                      |

| 20      | Global Clock 5               | 1 = Disabled During Configuration                      |

| 19      | Global Clock 4               | 1 = Disabled During Configuration                      |

| 18      | Global Clock 3               | 1 = Disabled During Configuration                      |

| 17      | Global Clock 2               | 1 = Disabled During Configuration                      |

| 16      | Global Clock 1               | 1 = Disabled During Configuration                      |

| 15      | Reserved                     |                                                        |

| 14      | Reserved                     |                                                        |

| 13      | Reserved                     |                                                        |

| 12      | Reserved                     |                                                        |

| 11      | Reserved                     |                                                        |

| 10      | Reserved                     |                                                        |

| 9       | Reserved                     |                                                        |

| 8       | Reserved                     |                                                        |

| 7       | Reserved                     |                                                        |

| 6       | OTSn Pin Enable              | 1 = Enable OTSn Pin Special Function                   |

| 5       | Reserved                     |                                                        |

| 4       | Configuration Memory Lockout | 1 = Configuration Memory Lockout Enabled               |

| 3       | Check Function               | 1 = Check Function Disabled (Checkn Inactive)          |

| 2       | Cascade Control              | 1 = Cascade Disabled (Csoutn Inactive)                 |

| 1       | Reserved                     |                                                        |

| 0       | Reserved                     |                                                        |

Table 5.

System Control Register Bytes [3:0]

## Table 6. System Control Register Bytes [7:4]

| SCR | Scope                             | Comment                                             |

|-----|-----------------------------------|-----------------------------------------------------|

| 63  | Frame Interface                   | 1 = Enable Frame Interface                          |

| 62  | AVR Cache Interface               | 1 = Enable AVR Cache Interface                      |

| 61  | Global Clock 6 Mux Select Bit 1   |                                                     |

| 60  | Global Clock 6 Mux Select Bit 0   |                                                     |

| 59  | Reserved                          |                                                     |

| 58  | Reserved                          |                                                     |

| 57  | TOSC Internal Bias Resistor       | 1 = Enable Internal Bias Resistor                   |

| 56  | XTAL Internal Bias Resistor       | 1 = Enable Internal Bias Resistor                   |

| 55  | AVR Port E Drive                  | 1 = Full 20 mA Drive                                |

| 54  | AVR Port D Drive                  | 1 = Full 20 mA Drive                                |

| 53  | UART1 Tx/Rx Pins                  | 1 = TX1/RX1; 0 = UART1 Tx/Rx Shared with PE2/PE3    |

| 52  | UART0 Tx/Rx Pins                  | 1 = TX0/RX0; 0 = UART0 Tx/Rx Shared with PE0/PE1    |

| 51  | External Interrupt 3 Pin          | 1 = INTP3; 0 = External Interrupt 3 Shared with PE7 |

| 50  | External Interrupt 2 Pin          | 1 = INTP2; 0 = External Interrupt 2 Shared with PE6 |

| 49  | External Interrupt 1 Pin          | 1 = INTP1; 0 = External Interrupt 1 Shared with PE5 |

| 48  | External Interrupt 0 Pin          | 1 = INTP0; 0 = External Interrupt 0 Shared with PE4 |

| 47  | Reserved                          |                                                     |

| 46  | Reserved                          |                                                     |

| 45  | Reserved                          |                                                     |

| 44  | Reserved                          |                                                     |

| 43  | Reserved                          |                                                     |

| 42  | Reserved                          |                                                     |

| 41  | AVR Shared Program/Data Bit 1     | (See AVR Program/Data SRAM Partitioning)            |

| 40  | AVR Shared Program/Data Bit 0     | (See AVR Program/Data SRAM Partitioning)            |

| 39  | Reserved                          |                                                     |

| 38  | Frame Clock Phase Select          | 1 = Non-inverted Frame Clock                        |

| 37  | Program Boot Sector Write Protect | 1 = Disable Write Protect During Frame Writes       |

| 36  | Program SRAM Write Protect        | 1 = Disable Write Protect During Frame Writes       |

| 35  | AVRResetn Pin                     | 1 = Enable AVRResetn Pin (Active Low)               |

| 34  | Reserved                          |                                                     |

| 33  | Reserved                          |                                                     |

| 32  | Reserved                          |                                                     |

### **Quick Facts**

- Configuration download overrides the AVR Program memory write protect bits in SCR (refer to the "System Control Register" on page 9). Write protect bits only limit access from the AVR or FPGA interface and not the configuration interface. Write protect bits are ignored by the configuration control logic.

- The configuration control logic has no access to the AVR core registers or the AVR IO registers.

## System Control Register Bits [63:0]

Byte 7

| SCR[63]: | Frame Interface                               |

|----------|-----------------------------------------------|

|          | 0 = Disable FPGA Read/Write FPSLIC (AVR) SRAM |

|          | 1 = Enable FPGA Read/Write FPSLIC (AVR) SRAM  |

| SCR[62]: | AVR Cache Interface                           |

|          | 0 = Disable AVR Write FPGA Configuration SRAM |

|          | 1 = Enable AVR Write FPGA Configuration SRAM  |

|          |                                               |

SCR[61:60]: Global Clock 6 Mux Select Bits

Table 7. Global Clock 6 Mux Select

| SCR61 | SCR60 | Global Clock 6              |  |

|-------|-------|-----------------------------|--|

| 0     | 0     | "1"                         |  |

| 0     | 1     | AVR System Clock (osc)      |  |

| 1     | 0     | Timer Counter Clock (tosc)  |  |

| 1     | 1     | Watchdog Timer Clock (iosc) |  |

| SCR[59]: | Reserved                           |

|----------|------------------------------------|

| SCR[58]: | Reserved                           |

| SCR[57]: | TOSC Internal Bias Resistor        |

|          | 0 = Disable Internal Bias Resistor |

|          | 1 = Enable Internal Bias Resistor  |

| SCR[56]: | XTAL Internal Bias Resistor        |

|          | 0 = Disable Internal Bias Resistor |

|          | 1 = Enable Internal Bias Resistor  |

| Byte | 6 |

|------|---|

|------|---|

| SCR[55]: | AVR Port E Drive                                                  |

|----------|-------------------------------------------------------------------|

|          | 0 =6 mA Drive                                                     |

|          | 1 =20 mA Drive                                                    |

| SCR[54]: | AVR Port D Drive                                                  |

|          | 0 =6 mA Drive                                                     |

|          | 1 =20 mA Drive                                                    |

| SCR[53]: | UART1 Tx/Rx Pins                                                  |

|          | 0 = UART1 Tx Pin Shared with PE2; UART1<br>Rx Pin Shared with PE3 |

|          | 1 = UART1 Tx Pin is TX1; UART1 Rx Pin is RX1                      |

| SCR[52]: | UART0 Tx/Rx Pins                                                  |

|          | 0 = UART0 Tx Pin Shared with PE0; UART0<br>Rx Pin Shared with PE1 |

|          | 1 = UART0 Tx Pin is TX0; UART0 Rx Pin is RX0                      |

| SCR[51]: | External Interrupt 3 Pin                                          |

|          | 0 = External Interrupt 3 Pin is Shared with PE7                   |

|          | 1 = External Interrupt 3 Pin is INTP3                             |

| SCR[50]: | External Interrupt 2 Pin                                          |

|          | 0 = External Interrupt 2 Pin is Shared with PE6                   |

|          | 1 = External Interrupt 2 Pin is INTP2                             |

| SCR[49]: | External Interrupt 1 Pin                                          |

|          | 0 = External Interrupt 1 Pin is Shared with PE5                   |

|          | 1 = External Interrupt 1 Pin is INTP1                             |

| SCR[48]: | External Interrupt 0 Pin                                          |

|          | 0 = External Interrupt 0 Pin is Shared with PE4                   |

|          | 1 = External Interrupt 0 Pin is INTP0                             |

## SCR[47:42]: Reserved

SCR[41:40]: AVR Program/Data SRAM Partitioning Bits

## Table 8. AVR Program / Data SRAM Partitioning

| <b>SCR41</b><br>0 |                                                                                                                                            | SCR40                             | Program/Data Partitioning     |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------|--|--|

|                   |                                                                                                                                            | 0                                 | 16K x 16/4K x 8               |  |  |

|                   | 0                                                                                                                                          | 1                                 | 14K x 16/8K x 8               |  |  |

|                   | 1                                                                                                                                          | 0                                 | 12K x 16/12K x 8              |  |  |

|                   | 1                                                                                                                                          | 1                                 | 10K x 16/6K x 8               |  |  |

| SCR[39]:          | Reserved                                                                                                                                   |                                   |                               |  |  |

| SCR[38]:          | Frame Clock P                                                                                                                              | hase Select                       |                               |  |  |

|                   | 0 = Inverted Fr                                                                                                                            | ame Clock                         |                               |  |  |

|                   | 1 = Non-inverte                                                                                                                            | ed Frame Clock                    |                               |  |  |

|                   | By default, the user-selected Frame Clock is inverted at the FPSLIC (AVR) SRAM. By setting this bit (one) the inversion stage is bypassed. |                                   |                               |  |  |

| SCR[37]:          | AVR Program Boot Sector Write Protect Disable                                                                                              |                                   |                               |  |  |

|                   | 0 = AVR SRAM                                                                                                                               | A Boot Sector is Protecte         | d from FPGA Writes            |  |  |

|                   | 1 = AVR SRAM                                                                                                                               | A Boot Sector is NOT Pro          | otected from FPGA Writes      |  |  |

|                   | This Bit is Ove                                                                                                                            | rridden During Configura          | tion Download                 |  |  |

| SCR[36]:          | AVR Program                                                                                                                                | SRAM Write Protect Disa           | able                          |  |  |

|                   | 0 = AVR SRAM                                                                                                                               | I is Protected from FPG           | A Writes (Excludes Boot Secto |  |  |

|                   | 1 = AVR SRAM<br>(excludes Boot                                                                                                             | I is NOT Protected from t Sector) | FPGA Writes                   |  |  |

|                   | This Bit is Ove                                                                                                                            | rridden During Configura          | tion Download                 |  |  |

| SCR[35]:          | AVRResetn Pin Enable                                                                                                                       |                                   |                               |  |  |

|                   | 0 = Disable AV                                                                                                                             | RResetn Pin Function              |                               |  |  |

|                   | 1 = Enable AV                                                                                                                              | RResetn Pin Function              |                               |  |  |

| SCR[34]:          | Reserved                                                                                                                                   |                                   |                               |  |  |

| SCR[33]: Reserved |                                                                                                                                            |                                   |                               |  |  |

| SCR[32]:          | Reserved                                                                                                                                   |                                   |                               |  |  |

Byte 5

Byte 4

| Byte 3 | SCR[31]:    | I/O Tri-state                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |             | 0 = Disable I/O Tri-state During Configuration                                                                                                                                                                                                                                                                                                                                                                                      |

|        |             | 1 = Enable I/O Tri-state – forces all user defined I/O pins to tri-state during configuration download. Tri-state is released at the end of configuration download on the rising edge of CON.                                                                                                                                                                                                                                       |

|        | SCR[30]:    | Global Set/Reset                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |             | 0 = Global Set/Reset NOT Controlled by User During Configuration                                                                                                                                                                                                                                                                                                                                                                    |

|        |             | 1 = Global Set/Reset Controllable by User(Active Low) – allows the Global Set/Reset to hold the core DFFs in reset during configuration download. The Global Set/Reset is released at the end of configuration download on the rising edge of CON.                                                                                                                                                                                  |

|        | SCR[29]:    | AVR Real Time Monitor                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |             | 0 = Disable AVR Real Time Monitor                                                                                                                                                                                                                                                                                                                                                                                                   |

|        |             | 1 = Enable AVR Real Time Monitor                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |             | Real Time Monitor allows the user to externally visualize the AVR instruction bus and program counter in real time. The AVR must be placed into Debug Mode by setting the DBG bit in the Software Control Register (SFTCR).                                                                                                                                                                                                         |

|        | SCR[28]:    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                            |

|        | SCR[27]:    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                            |

|        | SCR[26]:    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                            |

|        | SCR[25:24]: | Fast Clock [1:0] Configuration Disable                                                                                                                                                                                                                                                                                                                                                                                              |

|        |             | 0 = Enable Fast Clock [1:0]                                                                                                                                                                                                                                                                                                                                                                                                         |

|        |             | 1 = Disable Fast Clock [1:0] During Configuration – allows the user to disable the input buffers driving the Fast Clocks. The clock buffers are enabled and disabled synchronously with the rising edge of the respective FCLK [1:0] signal, and stop in a high ("1") state. Setting the bit disables the appropriate FCLK [1:0] input buffer only and has no effect on the connection from the input buffer to the FPGA array.     |

| Byte 2 | SCR[23:16]: | Global Clocks [8:1] Configuration Disable                                                                                                                                                                                                                                                                                                                                                                                           |

|        |             | 0 = Enable Global Clock [8:1]                                                                                                                                                                                                                                                                                                                                                                                                       |

|        |             | 1 = Disable Global Clock [8:1] During Configuration – allows the user to disable the input buffers driving the Global Clocks. The clock buffers are enabled and disabled synchronously with the rising edge of the respective GCLK [8:1] signal, and stop in a high ("1") state. Setting the bit disables the appropriate GCLK [8:1] input buffer only and has no effect on the connection from the input buffer to the FPGA array. |

| Byte 1                     | SCR[15:14]: | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | SCR[13]:    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            | SCR[12]:    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            | SCR[11]:    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            | SCR[10]:    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            | SCR[9]:     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            | SCR[8]:     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Byte 0                     | SCR[7]:     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            | SCR[6]:     | OTS Pin Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                            |             | 0 = Disable OTS Pin Special Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                            |             | 1 = Enable OTS Pin Special Function – makes the OTS pin an active low input which controls global tri-state for all user I/O.                                                                                                                                                                                                                                                                                                                                                                                                 |

|                            | SCR[5]:     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            | SCR[4]:     | Configuration Memory Lockout (FPSLIC Security Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                            |             | 0 = Disable Memory Lockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                            |             | 1 = Enable Memory Lockout – any <i>subsequent</i> configuration download<br>initiated by the user, whether a normal download or a Check function<br>download, causes the InitnErrn pin to immediately activate. CON is<br>released, and no further configuration actively takes place. The download<br>sequence during which SCR[4] is set is NOT affected. Further<br><i>subsequent</i> writes to the System Control Register are also prohibited,<br>so bit SCR[4] may only be cleared by a power on reset or manual reset. |

|                            | SCR[3]:     | Check Function Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                            |             | 0 = Enable Check Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |