# Integrated Development System - Figaro User Guide

June 2002

Welcome to the Integrated Development System (IDS) from Atmel Corporation. This versatile system works with a variety of CAE platforms, providing a range of design entry and simulation options when designing an Atmel field programmable gate array (FPGA). ViewLogic's Workview Office and Powerview products, and OrCAD Express for Windows are supported for schematic entry and simulation. Simulation platforms supported also include Vital VHDL systems from Model Technology, and the Verilog-XL simulator.

Synthesis tools from Synopsys, Viewlogic, Everest Design Systems and Exemplar Logic are integrated into the system to provide optimum results. Atmel's IDS lets designers create fast, efficient, and predictable designs with AT40k Series FPGAs.

IDS has integrated an HDL planning environment to create efficient, technology independent VHDL and Verilog designs on Atmel FPGAs. Currently Synopsys, Exemplar, and Everest synthesis software is supported.

IDS also supports designs in the Xilinx XNF format. It provides the user with the ability to translate a Xilinx XC3000, XC4000, or XC5200 family design into an AT40k device. Most of the XBLOX components in a XNF design are automatically mapped to Atmel *Macro Generator* components. XNF import is integrated into the Viewlogic design flow.

Operation of the IDS is controlled by a single graphical interface, the Figaro Desktop. Figaro integrates the programs, links them through a unified data base, and provides a seamless working environment that allows the user to move easily among the programs. While the system is configured to help the user design and layout the chip by invoking the appropriate design modules, the user can also run programs independently from the Shell Window command-line.

It is recommended that the user also browse through the *AT40k IDS Tutorial*. The manual details steps to set up and implement sample designs using Figaro and the supported CAE interfaces. It also discusses ways to optimize designs for the AT6000 and AT40k architecture, so the user can create the chip in the most efficient manner.

# **Conventions Used in This Manual**

The following typographical conventions are used in this guide:

- File names, and program names are in Helvetica type, e.g. atmel.ini, PLA2Cdb

- Variables are in *italics*, e.g. *DesignName*.lib

- Text to be entered in input boxes are enclosed in "", e.g. "4bitalu"

- Italic text is used for names of buttons on the Flow Bars, e.g. *Open*

- Keyboard functions are shown as *<Key>*, e.g. *<Enter>*

- Buttons to execute functions are shown as pictograms, e.g.

Run

### **Product Updates**

Updates are made available to users during the maintenance period at no charge to the user. Each update comes with its own installation program, release notes, and any special instructions that might be necessary to make the transition to the new software version.

### Sales Representatives

Atmel sales representatives are ready to assist with pre-sales questions, product literature, price information, and product availability. To contact a local sales representative, please call Atmel at 408.441.0311 during normal business hours.

### **Customer Service**

Atmel Corporation Customer Service provides software and hardware support and assists customers in uploading and downloading files.

Assistance with any matter related to the IDS can be obtained by the following methods:

- 1. Calling Customer Service at 408.436.4119 between 9 am and 5 pm, Pacific Standard Time

- 2. Sending electronic mail to fpga@atmel.com

- 3. Accessing Atmel's web site at http://www.atmel.com

- 4. Faxing to 408.436.4200

- 5. Writing to:

Atmel Customer Service 2325 Orchard Parkway San Jose, CA 95131 USA

iii

iv

# **System Basics**

The Integrated Development System (IDS), otherwise known as Figaro, is designed to provide push-button capability in the design of Atmel FPGAs. This allows the user to either automate the design process, or optimize the design by invoking manual placement and routing options.

IDS supports many forms of design entry which include schematics, equation entry, and high-level language design. The system then automatically places, routes and optimizes the design to fit into the target device. Once that is completed, the user has a choice of either downloading the data onto the FPGA, Serial Configuration Memory, or creating a library of user defined macros (UDMs) for future applications. Expanded design analysis features provide delay estimates across the chip, as well as export timing reports and back annotation files for many different simulators.

The general concepts and organization of the design phases are discussed in this chapter, along with the following topics. To learn how to enter, simulate, compile, and back annotate a sample design with different menu options, refer to the *IDS Tutorial* for more information.

- IDS Design Flow

- Designs and User Libraries

- Common Design Information

- On-line Help

- The Transcript Window

- The Shell Window

- Starting and Ending a Session

# **IDS Design Flow**

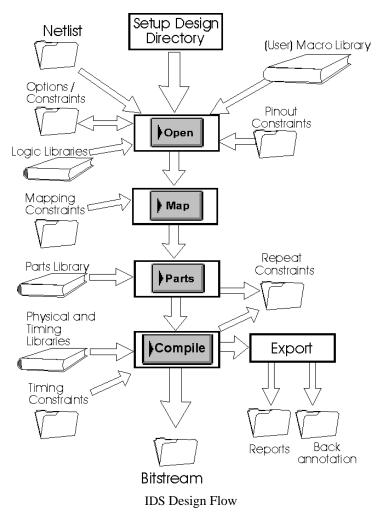

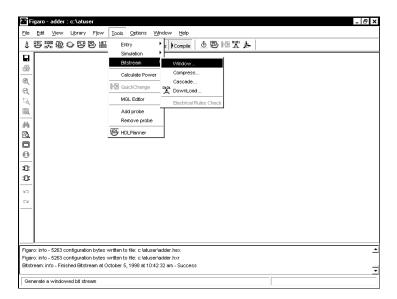

The following diagram summarizes the IDS design flow functions for bitstream creation.

### **Designs and User Libraries**

The design directory holds all files related to the design. This directory allows grouping of related designs and provides a consistent structure so that Figaro can handle design management tasks for the user. By Viewlogic and Intergraph convention, the design directory is analogous to the project directory.

Design files include all schematic-related and Figaro data base files. A design directory must be set up before schematic entry, simulation, or layout of a design can commence. This directory is the only place searched by Figaro for the design files.

See the *IDS Tutorial* for details on setting up a design. As a part of the process, the directory for storing all the design data must be identified to the system.

#### **User Libraries**

IDS supports the application of user libraries. The user library management features are intended to facilitate design reuse and help create high performance circuits. These libraries are repositories for user defined components which have been created by the *Macro Generators*, user schematics, or language-based entry. The system allows the user to specify as many libraries as needed. A common practice is to set up a design-specific library and maintain another that contains common macros shared by different designs.

A library consists of several parts which include the layout files, the CAE system specific files (schematics, symbols, etc.), and any related files that were used to produce the layout. Figaro will maintain all files that go into and out of libraries as well as set up the appropriate control files for the CAE system to access the libraries.

The *Library*>*Library Setup* dialog box is used to create a user library. Once specified, Figaro will create the layout library file as well as the library sub-directory for storing the rest of the library information. The *Figaro* chapter in the *IDS Tutorial* will provide details on this structure. Also refer to specific platforms under "CAE Interfaces" in the *Tutorial* for details on design related files that are stored in the library.

Sample structures for the PC and Workstation environments are provided below.

For the PC

If a layout library was defined as c:\*AtUser*\4bitalu\*user*.lib the following structure would be created:

c:AtUser4bitalu

user.lib

user\

*macro1*\ *macro1* design files

CAE system files

macro2

macro2 design files

CAE system files

CAE system files\

For the Workstation

/AtUser/4bitalu/

user.lib

user/

macro1/ macro1 design files CAE system files macro2/ macro2 design files CAE system files/

### **Common Design Information**

#### Figaro.ini

The user can customize projects by configuring such items as pin package specifications, design check rules, automatic place and route performance, design analysis parameters, bitstream format, and numerous ancillary screen output functions. The user can determine the default setting each time when beginning a new design.

In the design settings, the user can define such things as libraries for design data, and where output is to be stored for each design.

Figaro utilizes two configuration files, the figaro.ini and *DesignName*.ini files, to store user and design settings.

The user environment is defined in the figaro.ini file. This file contains such information as individual user defined (or default) display threshold and color assignments, and tracks all designs from a single location. The contents of the figaro.ini file can be changed under the *Options>Options* and *Options>Display Options* menus. This file is stored in the directory where Figaro is run from. The user should ensure that the program is started from the same directory each time so the required setup information can be reloaded.

### DesignName.ini

The *DesignName*.ini file contains design settings that directly affect the design data, independent of the user's environment. This file is maintained as needed. It is updated when changes to any design specific setting, such as defining a user library, are made.

The *DesignName*.ini file is stored in the design directory. It will be loaded whenever the design is selected via the *File>Design Setup* or *Open Design* menu options. The file is given the same name as the design. For the example design called "4bitalu", there will be a file named 4bitalu.ini in its design directory.

The following output files contain information that reflect the operations of the software:

#### DesignName.log

The *DesignName*.log file contains a list of all operations initiated for a design. Diverse information about the design setup, design checks done when a design is opened, placement and routing statistics and many other details are stored in this file. All information that is displayed in the transcript window will be stored in the log as well. A toolbar button is available for viewing of the log file. This file should be reviewed when any problem is encountered during execution of the design flow.

#### **Program Output Files**

The Integrated Design System is composed of many different programs, and the user will encounter a good variety of files in the design directory. A detailed list of all program output files will be found in the following documentation:

- IDS Tutorial, Figaro Figaro Files.

- Technical Reference & Release Notes, Design Files.

### **Backup Files**

Programs that modify the data base files generate a backup file. When a new copy of most any file in the design is produced, the previous copy is saved, with a "~" character as the last character of the file extension. For example 4BITALU.LOG, would be saved as 4BITALU.LO~.

### **On-line Help**

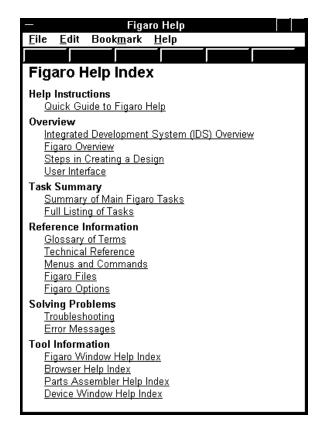

The *Help* function contains detailed information on all parts of the IDS. This function is context sensitive, but can also be invoked directly from the menu bar. The "Figaro" section of the *IDS Tutorial* contains detailed information on how to invoke and get *Help* on specific topics. An example of the *Help* window is shown below.

The Help Window

### The Transcript Window

All information about processes within IDS is displayed in the transcript window. The information displayed here is also stored in the design log file. Normal design information will be displayed in a standard font in black. All warnings are displayed in a bold font in blue. All errors are displayed in the same bold font in red. The user should check this window first to determine the progress of a design.

Refer to the "Figaro" section of the *IDS Tutorial* for more details on the transcript window.

### The Shell Window

The *New Shell Window* button in the vertical menu bar will create a window for manipulation of files in the design directory. Common operations such as editing simulation command files or creating constraint files can easily be done, as the shell is invoked in the design directory.

## Starting a Session

Before beginning a session, verify that the appropriate environment variables are set for Figaro and the selected CAE system. These variables are discussed in the "Installation Guide" as well as the Tutorial for the specific CAE System.

To invoke Figaro from within Windows, double click on its icon, or enter the command "figaro" if in UNIX. Set the active design by using the  $\boxed{4}$  icon or *File>Design Setup* menu option.

Subsequent chapters will discuss each design phase or activity represented by the Flowbar buttons.

### **Ending a Session**

Select the *File>Exit* menu option to end the Figaro session. A prompt will be displayed to confirm exiting from the Desktop. If a design has been modified in any way, an additional prompt will be issued to save the design.

# **Design Entry**

The Integrated Development System (IDS) offers a wide array of interfaces to work with design input processes such as schematic capture, equation entry, macro generation, and HDL planning and entry. Once the design is entered, it can be simulated. A netlist can then be created and the layout completed based on the specified CAE system.

Figaro supports Viewlogic tools for schematic capture. This platform is fully integrated with IDS so the interface is transparent to the user when moving between Figaro and the third party system during all phases of the design.

Designs requiring equation entry are also supported by IDS. Although ABEL and CUPL users must run these tools on PCs outside of Figaro they can bring the resulting \*.tt1, \*.tt2, or \*.pla, formatted files into IDS for optimization and/or conversion into schematics or components for the user library in the PC. The macros created can optionally be simulated with any of the supported CAE tools.

The user can also take advantage of the *Macro Generators* in IDS to create efficient and optimized building blocks for the design. These functions range in complexity from simple gates to complex parallel pipelined multipliers. The vast array of *Generators* will provide more opportunities and flexibility when implementing a design.

Another possible method of design input is via high level design language (HDL) entry. HDLPlanner offers an environment that fosters code portability and facilitates the use of optimized macros. The user can take advantage of functional modules previously optimized for the AT40k architecture and apply them to current or future designs.

To support HDL Entry, the Atmel macro library has been translated for third party vendors of synthesis tools such as Viewlogic, Synopsys, Everest, and Exemplar Logic. These synthesis tools are integrated into Figaro to facilitate the high level design entry process. As a result, performance can be optimized through operator inferencing and use of the Atmel *Macro Generators*. The AT40k library of components can be divided into 2 types of macros: functional and dynamic. Functional macros are components with fixed functions, such as the 2 input AND gate. Dynamic macros are designed to allow user specification of any desired function, to be attached as an attribute via an equation string, on the symbol. This should be used only when a specific function for an AT40k core cell is required. Designs targeted to AT40k can use a mix of dynamic and functional macros. Please refer to the *AT40k Macro Library* for more details on the list of all macros and the attributes available.

Once a design has been entered and synthesized with optional tools, a netlist can be generated and used for placement and routing.

# Schematic Entry

The Integrated Development System is set up to provide the user direct access to a variety of schematic capture tools from the Figaro Desktop. The products supported are:

- Viewlogic PC products Workview Office, PROSeries, and WorkviewPlus; Sun workstation products Powerview, and Workview

- OrCAD Express for Windows

To start schematic entry from Figaro, click on the *Schematic Entry* button on the Flowbar as shown. The CAE tool of choice will be brought up within the Figaro environment.

| File     | igaro<br>Edit | - 4bital<br>View | u : c:\ati  |            | Tools     | Options    | Windov | w <u>H</u> elp |         |          |        |   |      |      | -    | 8 |

|----------|---------------|------------------|-------------|------------|-----------|------------|--------|----------------|---------|----------|--------|---|------|------|------|---|

|          | -             | _                | 09          |            | -         |            |        | Compile        | Ō       | 롼        | 1.1 12 | 4 |      |      |      |   |

|          |               |                  |             |            |           |            |        |                |         |          |        |   |      | <br> | <br> |   |

| 8        |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

| Ð        |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

| Q<br>R   |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

| Щ.       |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

| 44       |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

| <u>0</u> |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

| 8        |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

| 20:      |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

| ÷        |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

| кЭ       |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

| CH       |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

|          |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

|          |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

| 1. Berry |               | ultere led       | o - Library | Maria      | /         |            |        |                |         |          |        |   | <br> | <br> | <br> |   |

| Ven      | dorCon        | figuratic        | n: info - S | ource ven  | dor atmel |            |        | ry at40000     |         |          |        |   |      |      |      |   |

| Libra    | aryCom        | piler: inf       | o - Library | file at40k | no longe  | r found or | search | path - usin    | g cache | ed libra | ry     |   |      |      |      |   |

|          |               |                  |             |            |           |            |        |                |         |          |        |   |      |      |      |   |

Schematic Entry

# System Setup

Figaro automatically sets up the paths and directories needed for the Atmel libraries, user libraries, and the design directory to interface with the CAE system specified.

The Atmel FPGA library is used to reference logical and timing models for every cell in the library, while the user libraries contain custom macros created for functions specific to current or prior designs. The design directory houses all the output files from both the schematic tool and Figaro that are related to the design.

Figaro also automatically calls up the CAE tools in the IDS environment and integrates the process into the design flow for netlist creation.

### Viewlogic

IDS controls the complete process of entering schematics with the Viewlogic tool. Once a design has been set up via the  $\boxed{\underline{A}}$  icon or *File>Design Setup* dialog box, the *Schematic Entry* button can be used to bring up the schematic editor on the current design.

As part of the process, Figaro will update the project.vpj, registry, and viewdraw.ini files for Workview Office, or the project.lst and viewdraw.ini files for other Viewlogic systems. It will also invoke the appropriate Viewlogic tool for schematic entry. The following table lists the platform and the tool invoked:

| CAE Platform    | Tool       |

|-----------------|------------|

| Workview Office | Viewdraw   |

| PROSeries       | PROcapture |

| WorkviewPlus    | Viewdraw   |

| Powerview       | Viewdraw   |

| Workview        | Workview   |

Once in the schematic tool, all macros used must be: a) Atmel FPGA library components, b) user library components, or c) hierarchical blocks that have been created with the Atmel FPGA library. Viewlogic BUILTIN library elements cannot be used as the Figaro placement and routing tools will not recognize them.

Once the design has been captured, the user can proceed to simulate or compile. For compilation, the Viewlogic Wir files are read directly by Figaro using the *Open* button.

### **OrCAD Express for Windows**

IDS controls the complete process of entering schematics with the OrCAD tool. Once a design has been set up via the  $\boxed{\frac{1}{2}}$  icon or *File>Design Setup* dialog box, the *Schematic Entry* button can be used to bring up the schematic editor on the current design.

Once in the schematic tool, all macros used must be: a) Atmel FPGA library components, b) user library components, or c) hierarchical blocks that have been created with the Atmel FPGA library.

It is important to attach "hierarchical ports" to all input and output pins at all levels of the design. The user should also change the name and type for each port used. This ensures proper creation of the ports and corresponding directions by the netlist generator for Figaro to perform placement and routing.

Once the design has been captured, the user can proceed to compile (Pre-layout Functional Simulation is not supported for designs using the dynamic macros). For compilation, the OrCAD EDIF files are read directly by Figaro using the *Open* button.

A VITAL VHDL library is supported for Post-layout Simulation of OrCAD designs. For more details please refer to the OrCAD tutorial.

# **PLA Optimization**

The Integrated Development System provides the interface to PLA formatted designs from the Figaro Desktop. Before invoking this function the user needs to enter, edit, and translate their equation based designs to the PLA format. Equation entry provides a compact way of transferring logic descriptions to the Atmel FPGA design tools. The PLA optimization function allows the user to perform logic minimization, technology mapping, and layout optimization from Figaro. The resulting output can be converted into a hard macro or a schematic for use in the design and simulated as needed. The PLA compilers supported are:

- DATA I/O ABEL

- CUPL

The ABEL and CUPL compilers are PC based products, and the resulting files can be set up to interface directly with the Figaro software on either the PC or the workstation.

Click on the *PLA Optimization* button on the Flowbar as shown to initiate the optimization and conversion process.

| <b>F</b>     | igaro | 4bital | u : c:\atı | user    |          |           |                              |            |     |         |         |         |        |        | _   |     |   | _ | _ 6 |

|--------------|-------|--------|------------|---------|----------|-----------|------------------------------|------------|-----|---------|---------|---------|--------|--------|-----|-----|---|---|-----|

| Eile         | Edit  | ⊻iew   | Library    | Flow    | Tools    | Options   | <u>Window</u>                | / Help     | ,   |         |         |         |        |        |     |     |   |   |     |

| ۵            | 野     | 見趣     | 09         | 12 (13) | ) top    | en Map    | Parts                        | Compil     | e   | ð 🖗     | 5 HO    | щи<br>Д | 1      |        |     |     |   |   |     |

|              |       |        |            |         |          |           |                              |            |     |         |         |         |        |        |     |     |   |   |     |

| 8            |       |        |            |         |          |           |                              |            |     |         |         |         |        |        |     |     |   |   |     |

| Ð            |       |        |            |         |          |           |                              |            |     |         |         |         |        |        |     |     |   |   |     |

| Q            |       |        |            |         | PLA 0    | ptimizati | on and Ma                    | apping     |     |         |         |         |        |        | - 1 | ⊐ × | 1 |   |     |

| 13,<br>      |       |        |            |         | ctive P  | roject:   |                              |            |     |         |         |         |        |        |     |     |   |   |     |

| <u>III</u> , |       |        |            |         |          | c:\atus   | er                           |            |     |         |         |         |        |        |     |     | L |   |     |

| ÅÅ<br>R      |       |        |            |         | lesign I |           |                              |            |     |         |         |         |        |        |     | _   | L |   |     |

| ð.<br>8      |       |        |            |         | iesign i | ame:      | 4bitalu                      |            |     |         |         |         |        |        |     |     | L |   |     |

| 0            |       |        |            | 1       | echnol   | ogy:      | ANDOR                        |            |     |         |         |         |        |        |     | •   | L |   |     |

| 1            |       |        |            | 1       | -        |           |                              |            | _   |         |         |         |        |        |     |     | L |   |     |

| :0:          |       |        |            |         | 🗹 Ins    | entiu     | 🗆 cu                         | <i>n</i> . |     | Gener   | ate Vie | wLogi   | c sch  | ematic |     |     | L |   |     |

| кЭ           |       |        |            |         |          |           | ок                           | 1          | Car | - nel   | L       |         | elp    | 1      |     |     | L |   |     |

| Си           |       |        |            |         |          | _         | OK                           |            | Cal | IC8I    |         |         | ah     |        |     |     |   |   |     |

| _            |       |        |            | _       |          |           |                              |            |     |         |         |         |        |        |     |     |   |   |     |

|              |       |        |            |         |          |           |                              |            |     |         |         |         |        |        |     |     |   |   |     |

|              |       |        |            |         |          |           |                              |            |     |         |         |         |        |        |     |     |   |   |     |

|              |       |        | info - Ena |         |          |           |                              |            |     |         |         |         |        |        |     |     |   |   |     |

|              |       |        |            |         |          |           | cture library<br>not be supp |            |     | brarv h | nas bee | in spei | cified |        |     |     |   |   |     |

|              |       |        | , our o    |         |          |           |                              |            |     |         |         |         |        |        |     |     |   |   |     |

|              |       |        |            |         |          |           |                              |            |     |         |         |         |        |        |     |     |   |   |     |

PLA Optimization Dialog Box

# **Design Flow**

This module is invoked as another means of design entry when an optimized equation-based function is needed for a design.

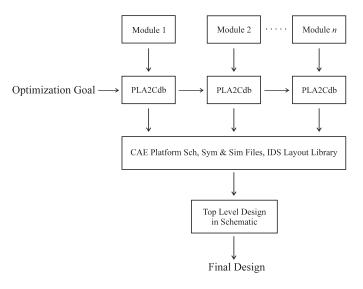

The Figaro design flow allows a mixed method of design entry. The design sub-modules are specified in ABEL or CUPL format, optimized individually, and become sub-blocks or complete designs. The individual sub-modules are then instantiated in a top level schematic with the appropriate I/Os added to form a complete design. Optionally the PLA description can constitute a complete design with I/Os automatically inserted by this tool.

The design flow utilizing PLA entry is illustrated and described in detail below.

PLA Design Flow in IDS

# System Setup

*PLA Optimization* is tailored for compiling optimized user-defined blocks. To ensure that the ABEL or CUPL PLA outputs are sent to the correct directories, the design files should be in place prior to initiating *Optimize PLA*. Refer to the *CAE Interfaces* section in the *IDS Tutorial* for a detailed description of the Setup process.

# Conversion and Optimization

The process of creating a design starts with the design and library setup as already mentioned. The design is partitioned into submodules and an ABEL or CUPL description is written for each of them. This is done independent of the Figaro environment. The user should run the appropriate program and options to generate the files needed. These files should be stored in the design directory. When the *Optimize PLA button* is selected, a dialog box appears in the Figaro Desktop which looks like the following.

| PLA Optimiza     | tion and Mappin | g _ 🗆 🗙                        |

|------------------|-----------------|--------------------------------|

| Active Project:  |                 |                                |

| 4bitalu : c:\atu | ser             |                                |

| Design Name:     | 4bitalu         |                                |

| Technology:      | ANDOR           | •                              |

| ✓ Insert IO      |                 | ☐ Generate ViewLogic Schematic |

| _                | ок              | Cancel Help                    |

The PLA Optimization and Mapping Dialog Box

The options in the dialog box are explained in detail below.

**Insertio** The user can invoke the automatic pad insertion algorithm by selecting this option. By default, ITTL, OD and ODEN pad buffers are inserted. However, if the file *designName*.pin is placed in the design directory, it can be specified to override the default pad types. This file should contain a signal name and a pad type, each on a separate line. An example .pin file is given below.

IN1 ITTLP IN2 ITTLP OUT1 ODF OUT2 ODF

**Generate ViewLogic Schematic** This switch is used to create a ViewLogic Schematic.

**CUPL** This switch is used to read \*.pla files produced by the CUPL compiler. By default, the \*.tt1 or \*.tt2 files produced by ABEL compilers are used.

**Technology** If *Technology* is set to AND XOR, pre-optimized PLA files (\*.tt1 for ABEL and \*.pla for CUPL) are taken as input and AND-XOR optimization is performed

Some designs can be more efficiently optimized as AND-OR equations instead of AND-XOR equations. Although AND-OR minimization is not done using PLA optimization, it will still accept files that are optimized within the ABEL environment. After such optimization in ABEL, a PLA file with the extension \*.tt2 will be created and should be placed in the design directory. This file will be used for technology mapping of AND-OR equations.

# Note to Users of ABEL 5.X Software

The ABEL compiler version 5.1 onwards does not produce a \*.tt1 file. Therefore, a \*.tt1 file cannot be used for AND-XOR optimization. If AND-XOR optimization is needed, users can copy and rename the \*.tt2 file as \*.tt1 and perform AND-XOR optimization.

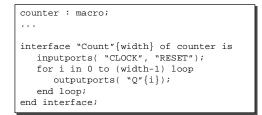

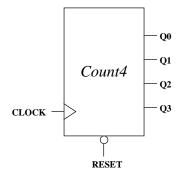

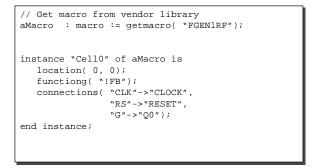

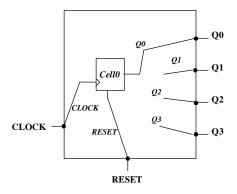

# **Macro Generators**

The *Macro Generators* module provides the user with the ability to construct highly efficient counters, adders, and other structured blocks. It is designed to allow easy inclusion of new *Generators* from Atmel and other third party vendors in the future. The core set of *Generators* is based on the EIA Library of Parameterized Macros (LPM) standard. This core set has been enhanced to achieve a superset to this specification.

A complete explanation of each Generator available at the time of release is provided in the *Technical Reference & Release Notes*. Because of continuous additions to the *Macro Generators*, some new functions may not be covered in the manual. On-line *Help* provides the most current information, and is discussed in this chapter. Both on-line *Help* and the *Technical Reference* manual provide information on the parameters available, pin type descriptions, and truth tables. Statistics on speed, delay, size, gates per cell, and power consumption are also addressed.

The basic user interface and details of how to get more information about a specific Generator are explained below. A step by step description on how to run a Generator is also available in the *AT40K IDS Tutorial* manual.

# **Design Flow**

A design and its associated user library must be set up prior to the initiation of this module. Once the *Macro Generators* button is selected, the following dialog box will appear in the Figaro Desktop as shown below.

| AT40K Macro Generators                | _   □   ×                    |

|---------------------------------------|------------------------------|

| Width 0                               | Absolute Value               |

|                                       | Accumulator                  |

|                                       | Adder-Carry Select           |

|                                       | Adder-Ripple Carry           |

|                                       | Comparator                   |

|                                       | Deductor                     |

|                                       | Increment/Decrement by 1     |

|                                       | Increment/Decrement by value |

|                                       | Multiplier-Serial Parallel   |

|                                       | Multiplier-Signed            |

|                                       | Multiplier-Unsigned          |

| Arithmetic Counters DSP 1/0 Logic Men | Options                      |

| Macro Name                            | Hard Macro                   |

| Pin Map File Name                     | Generate Schematic           |

| User Library                          | Browse Batch                 |

| Add to Batch Generate Cancel          | Help View Batch 0            |

Macro Generators Dialog Box

The tabs along the bottom represent the various categories of *Macro Generators* available. The arrow buttons along the bottom allow the user to scroll through the entire selection. The tabs along the side display the *Generator* functions. A function may be available for more than one category. The arrow buttons along the side allow the user to scroll through the entire selection.

The user must enter the name of the macro to be created before the Generators can put it into the library. Specify the appropriate values for the parameters such as the input or output widths of the function. If any required field is not filled in prior to selecting the Generate button an error message will be displayed.

| ×                                                                              | ( |

|--------------------------------------------------------------------------------|---|

| The following fields must have values before pressing Generate:<br>Macro Name, |   |

| User Library                                                                   |   |

|                                                                                |   |

Macro Generators Error Message

To get details on component functionality and the associated parameters, press the Help button.

Verify the library path in the *User Library* list box or specify a new library by pressing the *Browse* button.

When *Macro Generators* is run, IDS will typically create a schematic automatically for the specified CAE system. However, for certain CAE platforms, a schematic is not required and so schematic generation is an optional step which is controlled through a check box in the *Macro Generators* dialog box.

The *Macro Generators* create a fixed layout hard macro for Figaro and the corresponding CAE systems symbol and simulation models. In the *Macro Generators* dialog box, the user has an option to generate just a schematic and simulation model for the desired macro by clearing the *Hard Macro* check box. This allows the user to edit the schematic and change the logic of the macro generated. However, the layout for the macro is not generated. It is most efficient to use the output of the *Macro Generators* as a hard macro.

The default pin names on the components generated by the *Macro Generators* can be changed by specifying the user defined pin names in a file and providing the name of that file as the value for the *Pin Map File Name* option in the *Macro Generators* dialog box. The optional pin map file allows alternate pin names to be specified.

Press the Help button in the dialog box to get information on the default pin names of the component. The pin map file syntax is as follows:

map default\_pin\_name user\_defined\_pin\_name

As an example, the default pin names generated for a 4 bit adder component are DATAA[3:0], DATAB[3:0], SUM[3:0], CIN, COUT. To change these pins to A[3:0], B[3:0], Q[3:0], RCI, RCO respectively the corresponding pin map file should contain the following lines.

map DATAA A map DATAB B map CIN RCI map COUT RCO

#### map SUM Q

Several macros can be generated in batch mode by using *the Add To Batch* function in the *Macro Generators* dialog box. To use the Macro Generators *Add To Batch* function follow the steps below.

- Store the macro settings in the batch by pressing Add To Batch after specifying the parameters for each macro. The Batch Size on the lower right corner of the Macro Generators dialog box will get incremented by one.

- Review the macros by pressing *View Batch* to bring up the following dialog box. To remove a macro from the batch list, select a macro and press *Remove*. Press *Close* to return to the *Macro Generator* dialog box.

| Batch Run Macro | Generators |                    |       |                | ×        |

|-----------------|------------|--------------------|-------|----------------|----------|

| Component Name  |            | Selected Options   |       |                |          |

| ab8             | <b>_</b>   | Name               |       | Value          |          |

| acc4<br>comp4   |            | Generator          |       | Absolute Value | <b>_</b> |

| mult8           |            | Pin Map File       |       |                |          |

|                 |            | Hard Macro         |       | true           |          |

|                 |            | Generate Schematic |       | false          |          |

|                 |            | width              |       | 8              |          |

|                 | -          |                    |       |                | <b>-</b> |

| •               | ▶          | 4                  |       |                | ▶        |

|                 | Remove     |                    | Close | ,              |          |

View Batch Dialog Box

• Press Generate when all macros are configured to the appropriate settings and *Batch Size* shows the final count. After each macro is generated and stored in the user library, the *Batch Size* counter is decremented accordingly. The following dialog box appears after successful completion of the *Macro Generators* batch run.

Completed Batch Run Dialog Box

# **User Library Structure**

Although user libraries are discussed at great length elsewhere, some important information that relate to the *Macro Generators* are highlighted below.

### **Output Files**

Once all of the needed information is specified, *Macro Generators* can be invoked to create a complete user library component with the associated output files as follows:

**Layout** Except for the I/O modules, all *Generators* create a hard layout by default which is stored in the Figaro format user library. Clearing the *Hard Macro* option instructs Figaro to leave the circuit as a soft macro.

**Schematic** The *Generators* produce schematics for the Viewlogic platform. For Viewlogic, the schematic is optional as the actual connectivity information is provided in the netlist (wir) files.

**Simulation** All *Generators* produce information which can be used to provide correct functional simulation. For Viewlogic, this is contained in the design specific wir file. For all other tool flows, either a Verilog or vhdl file is produced to provide the functional model.

**Symbol** To facilitate design entry using the *Generators*, symbols are automatically created for all supported schematic entry tools. The symbols will contain all the interface pins for the macros generated, with inputs on the left and outputs on the right.

**HDL Support** To support users who enter their designs with VHDL, a template of the macro is created. This template will contain the macro name and a list of the input and output pins in VHDL syntax. It can be found in the library directory inside the component's sub-directory with the extension \*.vht. Structural Verilog and VHDL descriptions of the macros are provided for *Tool Flows* that require them. These will be found in the library directory under the verilog and vhdl sub-directories. The postsim directory contains descriptions with buses flattened in order to facilitate *Post-layout Simulation*.

### **Statistics**

After the *Macro Generator* has completed running, a dialog box will be displayed showing statistics of the macro. It will look like the following.

| Macro – abs4                          |                                |  |  |  |  |  |  |

|---------------------------------------|--------------------------------|--|--|--|--|--|--|

| Aacro Performance (using -<br>Speed : | -2 speed grade) —<br>178.6 MHz |  |  |  |  |  |  |

| Critical Path Delay :                 | 5.6 ns                         |  |  |  |  |  |  |

| Power Consumption :                   | 0.0346 mA/MHz                  |  |  |  |  |  |  |

| Aacro Dimensions                      |                                |  |  |  |  |  |  |

| •                                     | 1x3 logic cells                |  |  |  |  |  |  |

| Acro Dimensions                       | •                              |  |  |  |  |  |  |

Macro Generators Statistics Box

The information displayed in this dialog box can also be found in a file, identically named as the user library directory, with the \*.sts extension. For example a library named *user*.lib will have a statistics file named *user/user*.sts. Additionally in the library directory under each component will be a file called *macro*.lst. This file will contain details of the parameters used to generate the macro. It will also contain a file called *macro*.sts with the above statistics for the macro.

2-16

# HDL Planner

This section presents a design development environment, called HDLPlanner, for planning and creating HDL designs for Atmel FPGAs. Special HDLPlanner features allow the incorporation of technology specific information during the early planning stages so a 100% technology independent design can be maintained. Additionally, HDLPlanner prepares the input data to take advantage of the synthesis software for optimum results.

The software's interface can define and instantiate pre-verified VHDL/Verilog modules in the design files quickly. The modules can be parameterized for bit-widths and clock/reset schemes.

The HDL Planner software is tightly integrated with the back-end layout generation engines. Using the *Macro Generators*, design modules can be automatically translated into hard macros with efficient implementation in Atmel FPGAs. On-line module statistics on area and delays can be accessed easily and used to estimate design performance.

Finally, HDL Planner is an open system. Using its IPEditor user interface, users can integrate their modules within HDL Planner and access them as if macros were supplied from the factory

It is an open knowledge archival system. Previously synthesized modules become an effective resource because they can be reused in future designs.

### Synthesis Technology Limitations

The benefits of hardware description languages (HDL) include the ability to parameterize modules and create technology independent designs. Parameterization allows generic definition of a module to be defined once but used multiple times with different parameters. The support for parameterization encourages design reuse and simplifies design maintenance. Technology independence in HDL also allows designs to be written once and then targeted to a large number of FPGAs or ASICs.

However HDL descriptions must be synthesized and optimized to realize their gate level implementation for placement and routing. Often, that means relying on synthesis software capabilities for module inferencing and logic optimization. Unlike manually entered circuits, HDL designs are more inefficient because of the inability of synthesis tools to fully incorporate technology specific information during optimization. A notable improvement is operator inferencing. This methodology identifies arithmetic and boolean operators from a design and links them to their preferred implementation from the technology library. However operator inferencing does not guarantee optimal results, as illustrated below.

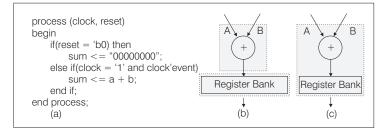

(a) VHDL template of registered adder, (b) Optimized implementation, (c) Preferred implementation.

#### **Operator Inferencing Limitations**

Additionally, only operators that are supported in the language can be inferred. Macros such as counters and FIFOs cannot be inferred. They must be instantiated using modules defined in a technology specific library, and technology independence is compromised in the process.

# FPGA Technology Specific Considerations

Synthesis tools perform architecture specific optimization without considering the technology contents of the FPGA. Such items include clocks and resets, tri-states, wired logic, I/O buffers, on-chip configurable memory resources and their address decoding circuitry. A cost driven optimization of these resources, unavailable from synthesis tools, is important for achieving optimum performance from the underlying FPGA technology.

HDL Planner's design planning environment encourages the users to follow *meet-in-the-middle* methodology for creating HDL designs. It contains a set of well defined methodologies that can be used to create technology independent descriptions. The graphical interface allows the user to address architecture, technology, and layout specific issues earlier in the design process, resulting in a simplified and shortened design cycle. It also provides area and delay statistics for corresponding performance estimates.

### **Graphical User Interface**

HDL Planner Graphical user interface can be divided into three separate components as outlined below.

| HDL Planning Software For AT40K FPGAs: untitled                                                        | _ 6 ×       |

|--------------------------------------------------------------------------------------------------------|-------------|

| Elle Edit VHDL Tools Exemplar Views Reports Help                                                       |             |

| │♥│D♥₽@│४६७0│००₩₩│∓±→│⊞⊞₩│                                                                             |             |

| Text: Category: Component: Register IdatchOen-Transparent Latch, with output Define                    | Instance    |

| •                                                                                                      | -           |

| LIBPARY ieee ;<br>USS ieee.std_logic_l164.all;<br><br>Do not delete following library and use clauses. |             |

| - bioc delete following library and use clauses.<br><br>library work;                                  |             |

| use work.components.components.all;                                                                    |             |

| ENTITY entityName IS<br>PORT (                                                                         |             |

| END entityName;                                                                                        |             |

| ARCHITECTURE behaviour of entityName IS                                                                |             |

| Add SIGNAL definitions here                                                                            |             |

| BECIN                                                                                                  |             |

| Define the architecture here                                                                           |             |

| END behaviour;                                                                                         |             |

|                                                                                                        | Ŧ           |

| File: untitled Ln 1 Co                                                                                 | I 1 EDITING |

HDL Planner Graphical User Interface

**Design Editor**

The built-in editor contains buttons to create and save projects, as well as support basic text editing operations such as cut, copy, paste, search, and find etc. This UI specification conforms to the Windows 97 standard.

Module Definition and Instantiation Panes

Special list boxes and buttons are provided to select, define, and instantiate modules. (Refer to the Graphical User Interface above). Select a module and press the *Define* button. This inserts a generic definition of the module in the text window. Use the *Instance* button to instantiate a macro selected from the *Component* list box. Once the macro is instantiated, its parameters can be set by modifying the instantiation statement in the file.

| THDL Planner                         |                    |

|--------------------------------------|--------------------|

| Top Level Design averager            | ОК                 |

| Clock Signal                         | Revert to Defaults |

| Clock Signal CLK<br>Reset Signal RST | Cancel             |

|                                      | Help               |

| Clock Edge posedge                   |                    |

| Set or Reset                         |                    |

| Set or Reset                         |                    |

| Set / Reset Polarity                 |                    |

| Set / Reset Polarity                 |                    |

|                                      |                    |

HDL Planner Dialog Box

A module can be parameterized to account for the clock edge (positive or negative), as well as the set or reset pins and their polarities (high or low). The appropriate options should be selected before the component is defined or instantiated.

Resource Estimation and Automatic Macro Generation

Menu buttons are provided to access area and macro statistics of the component selected. Refer to the Table *Description of Important Menu Buttons* for further details.

The menu button *Invoke Macro Generators* is provided to create layouts for all components instantiated in the design. The *Macro Generators* dialog box is shown below.

NOTE Only those options that determine the physical properties can be supplied by the user. All other options are grayed out.

| acro Generators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |      |                 |            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-----------------|------------|

| Width 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pitch 0             |      | :hOen_prl_WIDTI | H_8        |

| Tri-state control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | in O Individual OEp | ins  |                 |            |

| Active Low Set/Reset     Asynchronous initialization     None     Reset     Set     Denset     Denset | - [-                | Hex  |                 |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nsparent Latch      |      | 🗌 🗆 Updated     |            |

| Pin Map File Name 📘                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |      | Compone         | ent Exists |

| User Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     | -    | Browse          | Batch size |

| Add to Batch Genera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | te Cancel           | Help | View Batch      | 0          |

Macro Generators Dialog Box

| Menu Item         | Menu Button          | Brief Description                      |

|-------------------|----------------------|----------------------------------------|

| VHDL <sup>1</sup> | Entity               | Add HDL template for VHDL entity       |

|                   | Architecture         | Add HDL template for VHDL architecture |

|                   | Comp Declaration     | Add component declaration statement    |

|                   | Comp Instantiation   | Add component instantiation statement  |

|                   | Process              | Add a process Statement                |

|                   | Clocked Process      | Add a clocked process statement        |

|                   | lf                   | Add if statement                       |

|                   | Case                 | Add case statement                     |

|                   | While Loop           | Add while loop statement               |

|                   | For Loop             | Add for loop                           |

|                   | Signal               | Add signal definition statement        |

|                   | Variable             | Add variable definition statement      |

|                   | Constant             | Add constant definition statement      |

|                   | Туре                 | Add type declaration statement         |

|                   | library              | Add library statement                  |

|                   | Package              | Add package statement                  |

| Verilog           | Module Definition    | Add a module definition statement      |

|                   | Module Instantiation | Add module instantiation statement     |

|                   | Always               | Add an always statement                |

|                   | Clocked Always       | Add clocked always statement           |

|                   | lf                   | Add if statement                       |

|                   | Case                 | Add case statement                     |

|                   | CaseX                | Add casex statement                    |

|                   | Casez                | Add casez statement                    |

|                   | For                  | Add for loop                           |

|                   | Repeat               | Add repeat loop                        |

<sup>&</sup>lt;sup>1</sup> This item will be overlaid with Verilog if Verilog HDL is selected

<sup>2-22</sup>

| Menu Item             | Menu Button                  | Brief Description                                   |

|-----------------------|------------------------------|-----------------------------------------------------|

|                       | While                        | Add while loop                                      |

|                       | Continuous Assignment        | Add continuous assignment statement                 |

|                       | Blocking Assignment          | Add blocking assignment statement                   |

|                       | Non Blocking<br>Assignment   | Add non blocking assignment statement               |

|                       | Register                     | Add reg statement                                   |

|                       | Wire                         | Add wir statement                                   |

|                       | Tristate                     | Add tri statement                                   |

|                       | Define                       | Add define statement                                |

|                       | Parameter                    | Add parameter statement                             |

|                       | Defparam                     | Add defparam statement                              |

|                       | include                      | Add include statement                               |

| Design                | Invoke Macro<br>Generators   | Invoke layout generator GUI                         |

|                       | Report Macro<br>Information  | Report information on modules used in design        |

|                       | Generate Synthesis<br>Script | Generate synthesis script                           |

| Exemplar <sup>2</sup> | Synthesis Tips               | Access synthesis experience                         |

|                       | Integrate a User Macro       | Invoke a software to integrate macro in HDL PLanner |

| Views                 | Behavioral                   | Display a behavioral description of a module        |

|                       | Structural                   | Display structural description of a module          |

|                       | Layout                       | Display a layout of a module layout in MGL          |

| Reports               | Area                         | Display area information for a module               |

|                       | Delay                        | Display delay information for a module              |

Description of Important Menu Buttons

<sup>&</sup>lt;sup>2</sup> Item Synopsys will be displayed if Synopsys synthesis software is selected

#### Planning HDL Designs

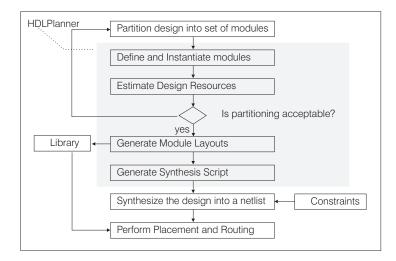

The process begins with a well thought out partitioning of a system into a set of modules as illustrated below. HDL Planner integrates the design planning philosophy into the process so the user can write a modular and hierarchical design description. Upon synthesis, a gate level netlist that is optimized for the target technology will be created. HDL Planner allows the user to estimate design resources and help avoid assumption changes late in the design cycle.

HDL Planner Design Flow

#### **HDL Planner Features and Benefits**

Important features of the HDL Planner software and its built in methodology are outlined below.

#### **Design Entry Specific**

Design Editing The software has an editing environment for planning, entering, and maintaining HDL descriptions. Its comprehensive set of pre-verified templates of complex HDL constructs can be used to speed up design entry. Refer to the Table *Description of Important Menu Buttons* above. HDL templates can also be used to facilitate the learning of VHDL and Verilog language syntax.

Technology Independent Design Entry Designs created in HDL Planner are 100% technology independent, conform to vendor laid out synthesis guidelines, and contain complete simulation models (so there are no black boxes).

Design Reuse HDL Planner has a User Interface to easily define and instantiate pre-verified functional modules. These modules can be parameterized for bit-widths as well as clock and reset schemes.

#### **Technology Specific**

Links to Layouts The *Macro Generators* interface of HDL Planner translates functional modules into layouts that are highly optimized for the architecture and technology.

Management of Clock and Reset Resources HDL Planner simplifies the task of managing the vast clock, set/reset resources on the FPGA. This feature is especially useful as no known synthesis system supports module parameterization around clocks and resets.

#### Synthesis Tools Specific

Overcomes Synthesis Technology Limitations HDL Planner can set up the data for synthesis to obtain the best output.

Tightly integrated with Synthesis Tools Synthesis scripts generated by HDL Planner do not require user knowledge of technology specific directives that are needed for efficient synthesis.

#### **Productivity Specific**