# FPSLIC Training Series (FPGA based designs)

### Software Requirements

CPS

### Hardware Requirements

- System Designer -Exemplar – Leonardo Spectrum -Modelsim Simulator

- ATSTK94 Starter Kit

- LAB 1 Synthesis with No Macro Generators andgate.vhd

- LAB 2 Synthesis with Automatic Macro Generators adder.vhd

- LAB 3 Synthesis with Macros for Simulation Counter.vhd

- LAB 4 Synthesis with Black Box Macro Generators ramdesign.vhd

# LAB 1 : LeonardoSpectrum flow with No Macro Generators

### Creating a New Project in System Designer

- 1. Go to Start > Programs > Atmel > System Designer 3.0 to open System Designer .

- 2. From the "Project" menu select "New..."

- 3. Select "New Project Wizard". This will open the New Project Wizard, which allows you to choose your project directory, select which part you want to design with and configure the design tool flow.

- 4. Press "Next >"

- 5. Set-up the Design Directory C:\TRAINING\AVR\LAB1

- 6. Setup the Design File Name LAB1

- 7. Press "Next >"

- In the "New Project Wizard Parts Dialog" select the AT94K40-25DQC, this is the 208-pin TQFP device on the ATSTK94.

- 9. Press "Next >"

- 10. In the "New Project Wizard Tool Flow Dialog select "Mentor VHDL"

- 11. Press "Next >"

- 12. It is possible to add multiple parts to work on using the New Project Wizard Add More Parts Dialog, but for this lab session we will focus on a single AT94K device.

- 13. Press "Next >"

- 14. Press "Finish" on the New Project Wizard Congratulations Dialog.

- 15. Upon clicking the "Finish" button, the "Device View" will be present, click on the part to enter the "Design Flow View".

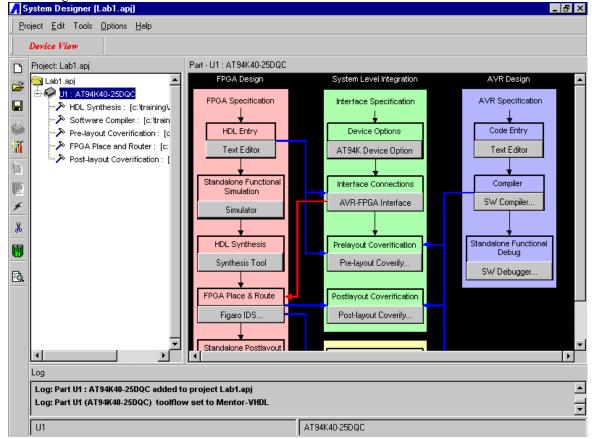

Figure 1: System Designer Design Flow

The Design Flow view shows the steps required to do a design for FPSLIC, using System Designer and coverification. The arrows on the diagram show dependencies between the steps. So for example if you want to run Pre-layout Coverification, you have to do HDL Entry, Code Entry and define the interface between the AVR and FPGA first.

In this lab we only concentrate on FPGA part of FPSLIC (FPGA Standalone) not on AVR/Coverification part of it. To do FPGA design entry we can either follow the pink path or use the HDL Planner with in FPGA Place and Route tool (**Figaro IDS**), we will choose the later part.

# FPGA Place and Route (Figaro IDS) and HDL Planner

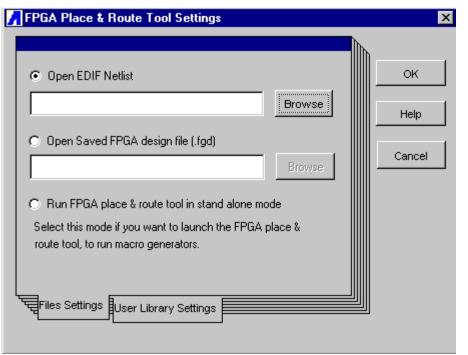

1. Press Figaro IDS, the FPGA Place and Route Tool Settings dialog box opens, see Figure 01.

| FPGA Place & Route Tool Settings                                                             | ×      |

|----------------------------------------------------------------------------------------------|--------|

|                                                                                              |        |

| O Open EDIF Netlist                                                                          | ок     |

| Browse                                                                                       | Help   |

| O Open Saved FPGA design file (.fgd)                                                         |        |

| Browse                                                                                       | Cancel |

| Run FPGA place & route tool in stand alone mode                                              |        |

| Select this mode if you want to launch the FPGA place & route tool, to run macro generators. |        |

| Files Settings                                                                               | ]      |

Figure 01. FPGA Place and Route Tool Settings

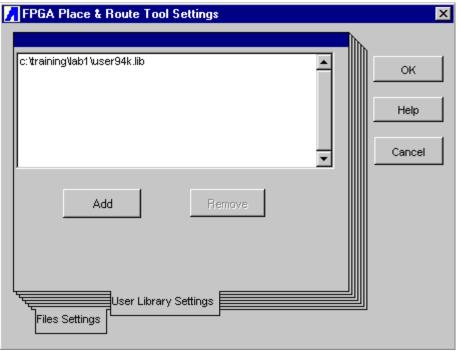

2. Select **Run FPGA place & route tool in stand alone mode**, another FPGA Place and Route Tool Settings dialog box appears, see **Figure 02**.

Figure 02. FPGA Place and Route Tool Settings

- 3. Take the default user library

- 4. Press OK. Figaro window pops up, follow the steps below to set up the design

- 5. Go to the File and choose Design Setup, see Figure 03.

| Design Directory Setup                                                 |                                                                              | ×          |

|------------------------------------------------------------------------|------------------------------------------------------------------------------|------------|

| Design Name:                                                           | Configuration:                                                               |            |

| dummydes                                                               | AT94K 💌                                                                      | ОК         |

| Design Directory:                                                      |                                                                              | Cancel     |

| c:\training\lab1                                                       | ×                                                                            | Help       |

| T                                                                      | ▼<br>▶                                                                       | New Design |

| Tools Flow:                                                            | Tools Flow Description:                                                      | Remove     |

| Exemplar-MTI<br>Exemplar-Verilog<br>Everest-VHDL<br>FPGA Express -VHDL | Import Net : EDIF<br>Export Net : Flat VHDL<br>Export Delay : Flat/Hier. SDF |            |

Figure 03. Design Directory Setup

6. Press New Design...

7. Complete the fields as shown in **Figure 04**.

| New Design                         |                                      | ×        |

|------------------------------------|--------------------------------------|----------|

| Design Name:                       | Design Directory:                    | ок       |

| andgate                            | c:\trainingVab1                      | Cancel   |

| <u> </u>                           | <ul> <li>c:\<br/>training</li> </ul> |          |

|                                    | lab1                                 | Help     |

| I I                                |                                      | <u> </u> |

| Files of Type:                     | Drives:                              |          |

| EDIF Netlist (*.edf)               | c:\t                                 | •        |

| Configuration:                     |                                      |          |

| AT94K                              |                                      | •        |

| Tools Flow:                        | Tools Flow Description:              |          |

| Exemplar-MTI                       | Import Net : EDIF                    |          |

| Everest-VHDL<br>FPGA Express -VHDL | Export Net : Flat VHDL               |          |

| Orcad                              | Export Delay : Flat/Hier. SDF        |          |

Figure 04 New Design

8. Press OK

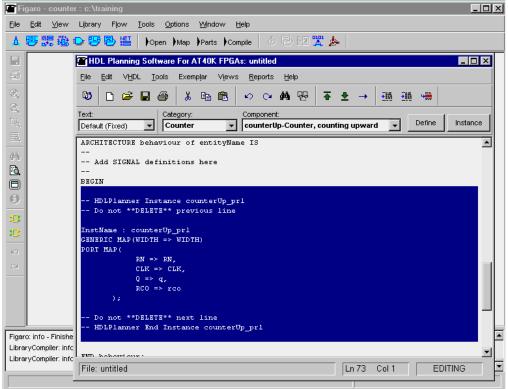

### HDL Planner

- Double-click on the HDL Planner icon or go to Tools → HDLPlanner in the figaro window to open the HDL planner.

- U X Figaro - andgate : c:\training Edit HDL Planning Software For AT94K FPGAs: andgate.vhd <u>F</u>ile \_ 🗆 × 4 <u>E</u>dit V<u>H</u>DL <u>T</u>ools Exemplar Views File <u>R</u>eports <u>H</u>elp 🔊 🖓 👭 🖳 85 🗅 🖻 🖶 🎒 🗈 🛍 **₹ ±** → 👬 👬 🦛 Text: Category: Component: Define Instance Register • -Default (Fixed) \* LIBRARY ieee ; USE ieee.std\_logic\_1164.all; -- Do not delete following library and use clauses. 楢 0 library work; use work.components.all; θ ENTITY entityName IS PORT ( 2 A, B : IN std\_logic; : OUT std\_logic Q ); END entityName; ARCHITECTURE behaviour of entityName IS SIGNAL dmmy\_din : STD\_LOGIC\_VECTOR(7 downto 0) := (others => 'Z' ); SIGNAL dummy : STD\_LOGIC := 'Z'; -- Add SIGNAL definitions here BEGIN VendorCo  $Q \leq A$  and B;٠ END behaviour; User Libra LibraryCo File: c:\training\andgate.vhd Ln 3 Col 1 EDITING •

- 2. Edit the template as shown in Figure 05.

#### Figure 05 HDLPlanner

- 3. Go to the File menu and select Save As. Name your project andgate.vhd in the directory created above.

- 4. Close HDL Planner

- 5. Close Figaro.

# Functional Simulation using Modelsim simulator for Lab1

- 1. Press the **Simulation** button. ModelSim opens

- 2. Go to the **Design** menu and choose **Create a New Library**, a dialog box appears, see **Figure 06**.

| 📓 Create a New Library                                        |  |  |  |

|---------------------------------------------------------------|--|--|--|

| Create                                                        |  |  |  |

| <ul> <li>a new library and a logical mapping to it</li> </ul> |  |  |  |

| O a map to an existing library                                |  |  |  |

| Library Name                                                  |  |  |  |

| work                                                          |  |  |  |

| Library Maps to:                                              |  |  |  |

| work Browse                                                   |  |  |  |

|                                                               |  |  |  |

| OK Cancel                                                     |  |  |  |

Figure 06. New Library

- 3. Take the default and press OK

- 4. Go to the **Design** menu and choose **Compile**, a browser window appears, select **andgate.vhd** and **by atmel.vhd**

- 5. Press Compile

- 6. Press Done

**Note:** *atmel.vhd* file contains the package information that was created by Figaro when andgate.vhd is saved in HDL planner

- 7. Follow next two steps to load the design

- 8. Go to the **Design** menu and choose **Load Design**, the Load Design window appears, see **Figure 07**.

| 📓 Load Design 📃 🗆 🗙                         |

|---------------------------------------------|

| Design \ VHDL \ Verilog \ Libraries \ SDF \ |

| Library: work                               |

| ⊕-E entityname                              |

|                                             |

|                                             |

|                                             |

|                                             |

|                                             |

|                                             |

|                                             |

|                                             |

| Simulate Simulator Resolution               |

| work.entityname Add default                 |

|                                             |

| Load Exit Save Cancel                       |

|                                             |

Figure 07. Load Design

- 9. Select entityname

- 10. Press Add

- 11. Press **Load.** Ignore the following comments:

#Cannot change directory while a simulatiion is in progress. #Use the "quit –sim" command to unload the design first.

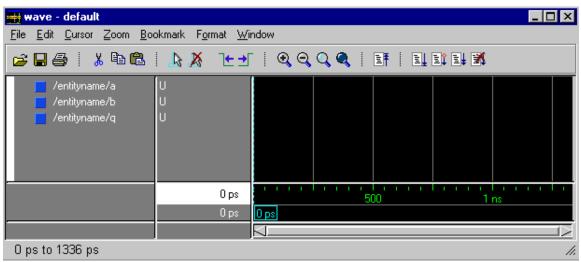

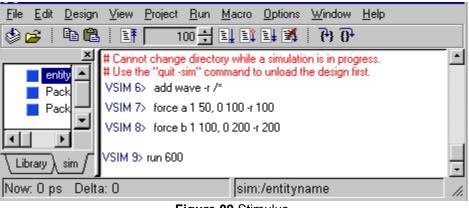

12. Type add wave -r /\* to open the wave window, see Figure 08.

Figure 08. Wave

13. Apply the following stimulus in the Modelsim window, see Figure 09. force a 1 50, 0 100 -r 100 force b 1 100, 0 200 -r 200 run 600

The force command forces "a" to value 1at 50 ns after the current time;

then to "0" 100 ns from now; and repeat this cycle for every 100 ns

The run command will simulate until 600 ns

Figure 09 Stimulus

14. Watch wave window for the expected results, see Figure 10.

| <del>= wave</del> - default                     |                                   |          |

|-------------------------------------------------|-----------------------------------|----------|

| <u>File Edit Cursor Zoom Bo</u>                 | okmark F <u>o</u> rmat <u>W</u> i | ndow     |

| 🗃 🖬 🚑 🕴 👪 🛍                                     | 上 🕺 🕒                             |          |

| /entityname/a<br>/entityname/b<br>/entityname/q | 0<br>0<br>0                       |          |

|                                                 | 600 ps                            | 500 1 ns |

|                                                 | 0 ps                              | 0 ps     |

|                                                 |                                   |          |

| 0 ps to 1125 ps                                 |                                   | 1.       |

Figure 10 Wave

- 15. Go to the Run menu and select Run –All.

- 16. Press the **Break** button after few seconds to stop running. Watch wave window for the expected results, see **Figure 11**.

| <del>==</del> wave - default                             |                                   |                 |

|----------------------------------------------------------|-----------------------------------|-----------------|

| <u>File E</u> dit <u>C</u> ursor <u>Z</u> oom <u>B</u> o | okmark F <u>o</u> rmat <u>W</u> i | indow           |

| 🗃 🖬 🍯 🕴 🖁 🛍                                              | 🕒 🕺 🕒                             |                 |

| /entityname/a<br>/entityname/b<br>/entityname/q          | 1<br>0<br>0                       |                 |

|                                                          | 2712250 ps                        | 2711500 2712 ns |

|                                                          | 0 ps                              |                 |

|                                                          |                                   |                 |

| 2711181 ps to 2712306 ps                                 | 3                                 | 1.              |

Figure 11 Wave

17. Go to the **Run** menu and select **Restart**, this clears the waveform window as shown in **Figure** 12.

| <del>= -</del> wave - default                            |                                   |         |                 |                 | _       |      |

|----------------------------------------------------------|-----------------------------------|---------|-----------------|-----------------|---------|------|

| <u>File E</u> dit <u>C</u> ursor <u>Z</u> oom <u>B</u> o | okmark F <u>o</u> rmat <u>W</u> i | indow   |                 |                 |         |      |

| 🗃 🖬 🍯 👗 🖻 🛍                                              | 🛯 📐 💥 🕒                           | -   Q Q | Q Q             |                 | 11 I¥ 🕺 |      |

| /entityname/a<br>/entityname/b<br>/entityname/q          | U<br>U<br>U                       |         |                 |                 |         |      |

|                                                          | 0 ps                              |         | 1 i i i i<br>50 | 1 i i i i<br>DO | 1 1     | ns i |

|                                                          | 0 ps                              | 0 ps    |                 |                 |         |      |

|                                                          |                                   |         |                 |                 |         |      |

| 0 ps to 1125 ps                                          |                                   |         |                 |                 |         | 11.  |

Figure 12 Wave

The values can also be forced by:

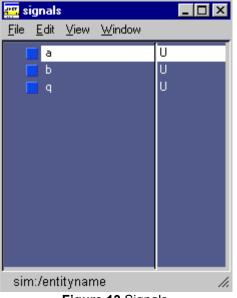

1. Go to the View menu and choose Signals, the signals window appears, see Figure 13.

Figure 13 Signals

- 2. Select **a**.

- 3. Go to the Edit menu and choose Force.

- 4. Force the value 1 for a

- 5. Press OK

- 6. Force the value **0** for **b** the same way.

- 7. Press OK

- 8. In the wave window single step by pressing [1] (Run) button a few times and watch the expected results.

- 9. Continue forcing different values during the simulation to see all the possibilities.

- 10. Close Modelsim window

# Exemplar Leonardo Spectrum Synthesis

1. Press the Synthesis Tool button, a dialog appears, see Figure 14.

| ×                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VHDL files are not added to the 'HDL Synthesis' Tool in the project tree view pane on the left hand side.<br>The VHDL files should be added in the bottom-up order i.e file with the top level entity should be selected last in the file selection browser. Do you want to Add VHDL files now? |

| yes no                                                                                                                                                                                                                                                                                          |

Figure 14 VHDL Files

2. Pess yes. A browser window appears, see Figure 15.

| Compile HDL                                                                 | . Source Files                              |

|-----------------------------------------------------------------------------|---------------------------------------------|

| Library:                                                                    | work                                        |

| Look jn:                                                                    | 🔁 lab1 💽 🖻 📺 📰                              |

| i work<br>i andgate.vi<br>i atmel.vhd iii i i i i i i i i i i i i i i i i i | hd                                          |

| File <u>n</u> ame:                                                          | "atmel.vhd" "andgate.vhd"                   |

| Files of <u>type</u> :                                                      | HDL Files (*.v;*.vl;*.vhd;*.vho;*.hdl;*.vo) |

|                                                                             | Default Options Edit Source                 |

Figure 15 Browser

- 3. Select andgate.vhd and atmel.vhd. Leonardo automatically lists the two selected input files, AT94K as technology and Output file as c:\training\labl\andgate.edf

- 4. Press the **Run Flow** button.

- 5. Close Leonardo.

# Place and Route IDS (Figaro)

1. Press the Figaro IDS button, a dialog appears, see Figure 16.

Figure 16 FPGA Place and Route Tool Settings

- 2. Select Open EDF Netlist and press Browse to select c:\training\lab1\andgate.edf.

- 3. Press OK, the Figaro Batch Options window appears, see Figure 17.

| Figaro Batch Options                                                                                                                                                                                                |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Design Constraints                                                                                                                                                                                                  |  |

| Click here to edit/assign pin locks> Assign Pin Locks                                                                                                                                                               |  |

| □ Place and Route                                                                                                                                                                                                   |  |

| Quality O1 © 2 O 3 O 4 O 5 O Auto                                                                                                                                                                                   |  |

| Timing Driven Design Edit Timing Constraints                                                                                                                                                                        |  |

| Click on Compile button to run through the entire FPGA design flow. To run individual steps in the design flow or to do manual place and route, click on OK and select Window->New Compile window on Figaro desktop |  |

| OK Compile Help                                                                                                                                                                                                     |  |

Figure 17 Figaro Batch Options

4. Select Assign Pin Locks, this will open the assign pin locks dialog box, see **Figure 18**.

| 🖀 Assign Pin Locks                           |                                                                       |            |

|----------------------------------------------|-----------------------------------------------------------------------|------------|

| Design I./Os                                 | Usable Pins <purpose></purpose>                                       |            |

| a (-> A.202)<br>b (-> A.198)<br>q (-> A.200) | A.196<br>A.197<br>A.198 (-> b)<br>A.199<br>A.299 (+, r)               | Cancel     |

|                                              | A.200 (-> q)<br>A.201<br>A.202 (-> a)<br>A.203<br>A.204 <gck8></gck8> | Help       |

| •                                            | N N                                                                   | 3          |

|                                              | < Lock >>                                                             | Lock All   |

| Unlock                                       | Unlock                                                                | Unlock All |

Figure 18 Assign Pin Locks

- 5. Select 'a' under Design I/O and 'A.202' under Usable Pins

- 6. Press Lock.

- 7. Follow same procedure for all the I/Os as shown above.

- 8. Press OK

- 9. Press the **Compile** button. This will partition, place and route the design and export the bitstream.

- 10. If the routing is successful compile button in Figaro turns green or red if unsuccessful.

- 11. Exit Figaro, save the design.

# Postlayout Simulation using Modelsim simulator for Lab1

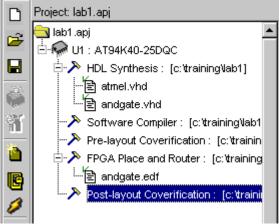

1. Double-click on **Post-layout Coverification** under the Project list to add the back annotated files, see **Figure 19**.

Figure 19. Project Window

2. The Test Bench Manager window appears, see Figure 20.

| 🖌 Test Bench Manager                                                                                                    | ×             |

|-------------------------------------------------------------------------------------------------------------------------|---------------|

| Please select the test bench file to be included with Post-Layout Co<br>To edit the file, click on the Edit File button | overification |

| c:\training\lab1\figba\andgate_posttb.vhd                                                                               | Browse        |

| OK Edit File Cancel                                                                                                     |               |

Figure 20 Test Bench Manager

#### 3. Select Edit File

### Note:

Since we are using only FPGA portion of FPSLIC, it is necessary to delete avr\_ram\_int component.

4. Highlight the stimulus syntax as shown in **Figure 21.**

| 🗉 andgate_posttb.vhd - WordPad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _ 🗆 🗵  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| <u>File E</u> dit <u>V</u> iew Insert F <u>o</u> rmat <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| <pre>signal sig_EXT_INT1: STD_LOGIC;<br/>signal sig_EXT_INT2: STD_LOGIC;<br/>signal sig_EXT_INT3: STD_LOGIC;<br/>signal sig_UART0_TX0: STD_LOGIC;<br/>signal sig_UART1_TX1: STD_LOGIC;<br/>signal sig_TOSC2: STD_LOGIC;<br/>signal sig_SDA_OUT: STD_LOGIC;<br/>signal sig_SDA_OUT: STD_LOGIC;<br/>signal sig_PORTD: STD_LOGIC;<br/>signal sig_PORTD: STD_LOGIC VECTOR (7 downto 0);<br/>signal sig_PORTE: STD_LOGIC VECTOR (7 downto 0);<br/>signal one : STD_LOGIC := '1';<br/>signal zero : STD_LOGIC := '0';</pre> | ×      |

| BEGIN<br>inst_andgate:entityname<br>port map (<br>a => sig a,                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| b => sig_b,<br>q => sig_q<br>);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| stimulus_process: process<br>begin<br>**** Add your stimulus values here ****<br>end process stimulus_process;<br>end arch_test_bench;                                                                                                                                                                                                                                                                                                                                                                                |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| For Help, press F1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | NUM // |

| Figure 21 Stimulus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

Figure 21 Stimulus

#### 5. Copy the following stimulus:

stimulus\_process: process begin sig\_a <= '0'; sig\_b <= '0'; wait for 100 ns; sig\_a <= '1'; wait for 100 ns; sig\_b <= '1'; wait for 200 ns; end process stimulus\_process;

The edited file is shown in **Figure 22**.

| 🗒 andgate_posttb.vhd - WordPad                                                                                                                                                                              | _ 🗆 🗵 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| <u>File E</u> dit <u>V</u> iew <u>I</u> nsert F <u>o</u> rmat <u>H</u> elp                                                                                                                                  |       |

|                                                                                                                                                                                                             |       |

| signal sig_SDA_OUT: STD_LOGIC;<br>signal sig_PORTD: STD_LOGIC_VECTOR (7 downto 0);<br>signal sig_PORTE: STD_LOGIC_VECTOR (7 downto 0);<br>signal one : STD_LOGIC := '1';<br>signal zero : STD_LOGIC := '0'; | ×     |

| BEGIN                                                                                                                                                                                                       |       |

| <pre>inst_andgate:entityname port map (     a =&gt; sig_a,     b =&gt; sig_b,     q =&gt; sig_q );</pre>                                                                                                    |       |

| stimulus process: process<br>begin<br>sig_a <= '0';<br>sig_b<='0';<br>wait for 100 ns;<br>sig_a <= '1';                                                                                                     |       |

| wait for 100 ns;<br>sig_b <= '1';<br>wait for 200 ns;<br>end process stimulus_process;                                                                                                                      |       |

| end arch_test_bench;                                                                                                                                                                                        | -     |

| For Help, press F1                                                                                                                                                                                          |       |

Figure 22 Edited Stimulus

- 6. Go to the File menu and choose Save.

- 7. Press **OK** to close the Test Bench Manager, the *select top level entity of the VHDL test bench* dialog box appears, see **Figure 23**.

| <mark>/</mark>             | ×                       |

|----------------------------|-------------------------|

| Select the top level entit | y of the VHDL testbench |

| entityname                 | <b></b>                 |

| post_test_bench            |                         |

|                            |                         |

|                            | •                       |

| ОК                         | Cancel                  |

Figure 23 Top Level Entity

8. Select post\_test\_bench and press OK, the SDF timing value dialog appears, see Figure 24.

| <mark>/</mark> |                                      |                                | ×        |

|----------------|--------------------------------------|--------------------------------|----------|

|                | F timing value «<br>on the design ir | (minimum, typical,<br>Instance | maximum> |

| minimum        |                                      |                                | <b>A</b> |

| typical        |                                      |                                |          |

| maximum        |                                      |                                | -        |

| 1              | []                                   |                                |          |

|                | OK                                   | Cancel                         |          |

Figure 24 SDF Timing Value

9. Select typical and press OK, ModelSim opens, see Figure 25.

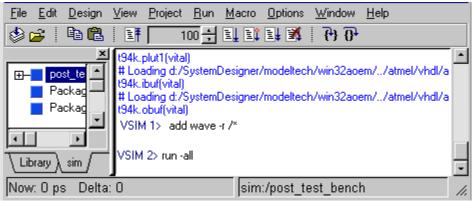

Figure 25 ModelSim

- 10. Minimize the DOS window

- 11. Type add wave -r /\*

- 12. Type run -all

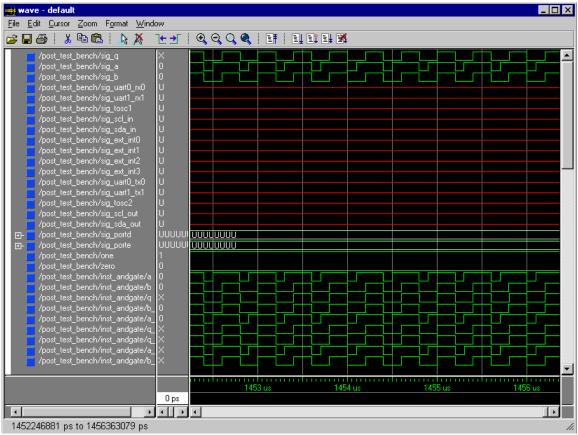

- 13. Press the break button after few seconds to see the results, see Figure 26.

Figure 26 Wave Results

14. Go to the File menu and select Quit .

# Programming the Device

### Hardware Setup

- 1. Connect the 25-pin parallel cable to the 25-pin Male connector of the ATDH2225 download cable, the 10-pin female header plugs into 10-pin male header (J1) on ATDH94STKB board.

- 2. Connect the power supply from an AC outlet to the 9V DC connector (P3) on ATDH94STKB

- 3. Make sure to set the jumpers that are located in between LEDs and Switches to FPGA side.

- 4. Adjust SW10 to PROG.

- 5. Adjust SW14 to ON position.

# Software Setup

- 1. Launch CPS

- 2. Make sure to set the fields as shown below

|                                                                    | (Please select Fam                                                         | -                |                                                                                            | edure menu)                                                                               |                                                                                                                                       |

|--------------------------------------------------------------------|----------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Files<br>Input File: C:\tra                                        | artition, program and veri<br>ining\lab1\andgate.bst<br>ining\lab1\out.bst | ify from an Atme | Info<br>One or more At<br>subsequent do<br>checksum can<br>each programm<br>HEX values are | wnload session<br>be obtained fro<br>ing session. In<br>only appender<br>e been partition | nay be generated for<br>s. The optional<br>m the log output of<br>this version of CPS,<br>d to the .BST output<br>ed. The output file |

| Family:<br>Device:<br>Reset Polarity:<br>Address [hex]:<br>Console | FPSLIC<br>ATFS40<br>Low                                                    | •           •    | COMM Port:<br>Data Rate:<br>A2 Bit Level:                                                  | LPT1<br>Fast<br>Low                                                                       |                                                                                                                                       |

|                                                                    |                                                                            | Start Pr         | rocedure Res                                                                               | store Defaults                                                                            | View Log File                                                                                                                         |

Figure 27 CPS

- Click Start Procedure, if everything goes OK you should see "Number of Fatal Errors

Check if AT94K40 configuration is successful:

- - Press Reset switch (SW12) on the right hand board edge.

- Make sure to adjust **SW10** to **RUN** position.

- Press SW1 and SW2 to check if andgate is working as expected.

# LAB 2 – LeonardoSpectrum with Automatic Macro Generators

In this lab, the test bench file adder\_tb is used for functional simulation. Copy the file from SystemDesigner/examples/fpga to c:\training\lab1

# Creating a Project

• Follow Section1 in Lab1 to Set up the c:\training\lab2\lab2.apj Project in System Designer.

# FPGA Place and Route (Figaro IDS) and HDL Planner

1. Press Figaro IDS, the FPGA Place and Route Tool Settings dialog box opens, see Figure 28.

| FPGA Place & Route Tool Settings                        | ×      |

|---------------------------------------------------------|--------|

|                                                         |        |

| O Open EDIF Netlist                                     | ок     |

| Browse                                                  | Help   |

| <ul> <li>Open Saved FPGA design file (.fgd)</li> </ul>  |        |

| Browse                                                  | Cancel |

| Run FPGA place & route tool in stand alone mode         |        |

| Select this mode if you want to launch the FPGA place & |        |

| route tool, to run macro generators.                    |        |

|                                                         |        |

| Files Settings                                          |        |

|                                                         |        |

Figure 28. FPGA Place and Route Tool Settings

- 2. Select **Run FPGA place & route tool in stand alone mode**, another FPGA Place and Route Tool Settings dialog box appears.

- 3. Take the default user library

- 4. Press **OK.** Figaro opens.

- 5. Go to the File menu and choose Design Setup.

- 6. Press New Design...

- 7. Complete the fields as shown below:

- Design Directory: C:\training\lab2

- Design Name: adder

- Files of Type EDIF Netlist (\*.edf)

- Configuration AT94K

- Tools Flow

Exemplar-MTI

- 8. Press OK

- 9. Press OK

#### HDL Planner

• Edit the template to match the adder (Adder.vhd) design file below:

#### Adder.vhd

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_signed.all;

_ _

-- Do not delete following library and use clauses.

---

library work;

use work.components.all;

ENTITY entityName IS

PORT (

А, В

: IN std_logic_vector(3 downto 0);

: OUT std logic vector(3 downto 0)

Q

);

END entityName;

ARCHITECTURE behaviour of entityName IS

_ _

--Add SIGNAL definitions here

BEGIN

Q \leq A + B;

END behaviour;

```

10. Go to the File menu and choose Save As adder.vhd in the directory created above.

11. Close Figaro.

# Functional Simulation using test bench file (adder\_tb.vhd)

- 1. Copy adder\_tb to c:\training\lab2

- 2. Click on the Simulator button. ModelSim opens.

- 3. Go to the Design menu and choose Create a New Library, take the default

- 4. Go to the Design menu and choose Compile, select compile atmel.vhd, adder.vhd and adder\_tb.vhd

- 5. Press Done

- 6. Go to the Design menu and choose Load New Design, select entityname\_tb

- 7. Press Add

- 8. Press Load

- 9. Type add wave -r /\*

- 10. Type run –all

- 11. Click on break button after a few seconds.

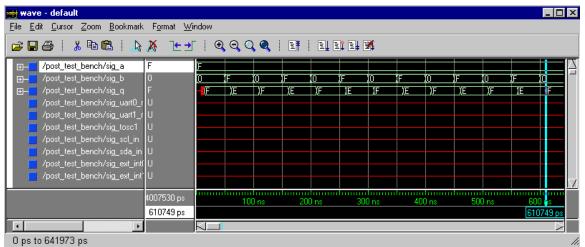

12. In the wave window, go to the **Zoom** menu and choose **Zoom Full**. The results are as shown in Figure 29.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <del>패</del> wave - default            |                            |                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------|--------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u>File Edit Cursor Zoom Bookman</u>   | k F <u>o</u> rmat <u>W</u> | indow                                                                                |

| B→       /entityname_tb/sig_b       0000       0000       0011       0100       0000       0010       0000       0011       0100       0000       0011       0100       0000       0011       0110       0000       0011       0110       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 🗃 🖬 🧉 👗 🖻 🛍 🕴 🙏                        | t 👗 📜 🛨                    |                                                                                      |

| B+       /entityname_tb/sig_q       0000       0000       00110       0011       01110       0101       1110       0110       1001       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000 <td< th=""><th>⊕–<mark>–</mark> /entityname_tb/sig_a</th><th>0000</th><th><u>10000 X0001 X0010 X0011 X0100 X0101 X0110 X0111 X0000 X1001 X1010 X1011 X1100</u></th></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ⊕– <mark>–</mark> /entityname_tb/sig_a | 0000                       | <u>10000 X0001 X0010 X0011 X0100 X0101 X0110 X0111 X0000 X1001 X1010 X1011 X1100</u> |

| B+       /entityname_tb/uut/a       0000       0000       0001       0010       0011       0110       0111       0000       1001       1010       1010       1011       10000       1001       1011       1000       1001       1011       1000       1000       1001       1011       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000       1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                        | 0000                       | 0000 20011 20100 20000 20010 20000 21000 20000 20110 20000                           |

| B+       /entityname_tb/uut/b       0000       0000       0010       0000       1000       0000       0110       0000         Im+       /entityname_tb/uut/q       0000       0000       0110       0001       0110       0000       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010       1010 <td></td> <td>0000</td> <td><u>0000 X0100 X0110 X0011 X0110 X0101 X1110 X0111 X0110 X1001 X1010 X1011 X1100</u></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        | 0000                       | <u>0000 X0100 X0110 X0011 X0110 X0101 X1110 X0111 X0110 X1001 X1010 X1011 X1100</u>  |

| Image: The state of the st |                                        | 0000                       | <u>0000 X0001 X0010 X0011 X0100 X0101 X0110 X0111 X0000 X1001 X1010 X1011 X1100</u>  |

| D000000 ps         200 ns         400 ns         600 ns           0 ps         0 ps         0 ps         0 ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                        | 0000                       | 0000 20011 20100 20000 20010 20000 21000 20000 20110 20000                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        | 0000                       | <u>10000 X0100 X0110 X0011 X0110 X0101 X1110 X0111 X0110 X1001 X1010 X1011 X1100</u> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |                            |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |                            |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |                            |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |                            |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |                            |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |                            |                                                                                      |

| O ps O ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                        | 000000 ps                  |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        | Û DS                       |                                                                                      |