# Am79R70

## **Ringing Subscriber Line Interface Circuit**

### DISTINCTIVE CHARACTERISTICS

- Ideal for ISDN-TA and set top applications

- On-chip ringing with on-chip ring-trip detector

- Low standby state power

- **■** Battery operation:

- V<sub>BAT1</sub>: -40 V to -67 V

- V<sub>BAT2</sub>: -19 V to V<sub>BAT1</sub>

- On-chip battery switching and feed selection

- On-hook transmission

- Polarity reversal option

- Programmable constant-current feed

- Programmable Open Circuit voltage

- Programmable loop-detect threshold

- Current gain = 1000

- Two-wire impedance set by single component

- Ground-key detector

- Tip Open state for ground-start lines

- Internal V<sub>EE</sub> regulator (no external –5 V power supply required)

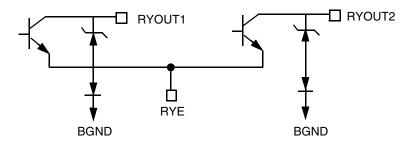

- Two on-chip relay drivers and snubber circuits

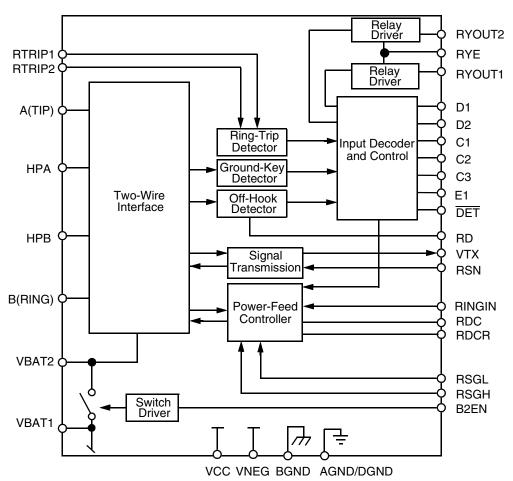

### **BLOCK DIAGRAM**

### **GENERAL DESCRIPTION**

The AMD family of subscriber line interface circuit (SLIC) products provide the telephone interface functions required throughout the worldwide market. AMD SLIC devices address all major telephony markets including central office (CO), private branch exchange (PBX), digital loop carrier (DLC), fiber-in-the-loop (FITL), radio-in-the-loop (RITL), hybrid fiber coax (HFC), and video telephony applications.

The AMD SLIC devices offer support of BORSHT (battery feed, overvoltage protection, ringing, supervision, hybrid, and test) functions with features including current limiting, on-hook transmission, polarity reversal, tip-open, and loop-current detection. These features allow reduction of linecard cost by minimizing component count, conserving board space, and supporting automated manufacturing.

The AMD SLIC devices provide the two- to four-wire hybrid function, DC loop feed, and two-wire supervision. Two-wire termination is programmed by a scaled impedance network. Transhybrid balance can be achieved with an external balance circuit or simply programmed using a companion AMD codec device, the Am79C02/03/031 DSLAC™ device, the Am79Q02/021/031 Programmable Quad SLAC (QSLAC™) device, or the Am79Q5457/4457 Nonprogrammable QSLAC device.

The Am79R70 Ringing SLIC device is a bipolar monolithic SLIC that offers on-chip ringing. Now designers can achieve significant cost reductions at the system level for short-loop applications by integrating the ringing function on chip. Examples of such applications would be ISDN Terminal Adaptors and set top boxes. Using a CMOS-compatible input waveform and wave shaping R-C network, the Am79R70 Ringing SLIC can provide trapezoidal wave ringing to meet various design requirements.

In order to further enhance the suitability of this device in short-loop, distributed switching applications, AMD has maximized power savings by incorporating battery switching on chip. The Am79R70 Ringing SLIC device switches between two battery supplies such that in the Off-hook (active) state, a low battery is used to save power. In order to meet the Open Circuit voltage requirements of fax machines and maintenance termination units (MTU), the SLIC automatically switches to a higher voltage in the On-hook (standby) state.

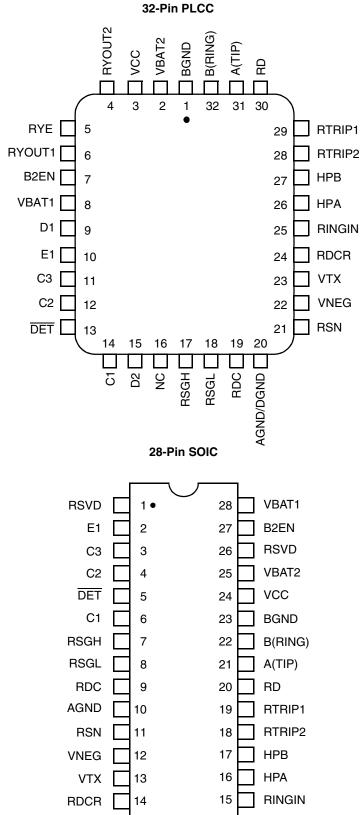

Like all of the AMD SLIC devices, the Am79R70 Ringing SLIC device supports on-hook transmission, ringtrip detection and programmable loop-detect threshold. The Am79R70 Ringing SLIC device is a programmable constant-current feed device with two on-chip relay drivers to operate external relays. This unique device is available in the proven AMD 75 V bipolar process in 32-pin PLCC packages.

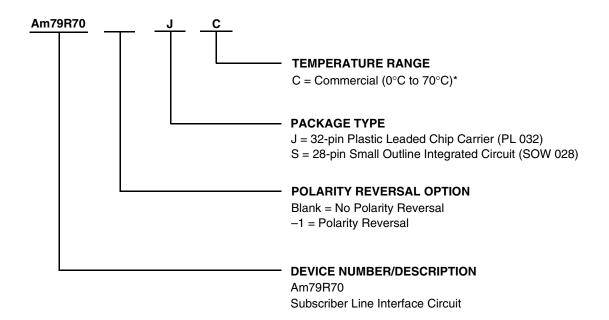

## **ORDERING INFORMATION**

## **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

| Vali    | d Combination | ons      |

|---------|---------------|----------|

| Am79R70 | -1            | JC<br>SC |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### Note:

<sup>\*</sup> Functionality of the device from 0°C to +70°C is guaranteed by production testing.

## **CONNECTION DIAGRAMS**

## **Top View**

### Notes:

- 1. Pin 1 is marked for orientation.

- 2. NC = No connect

- 3. RSVD = Reserved. Do not connect to this pin.

## **PIN DESCRIPTIONS**

| Pin Names | Туре      | Description                                                                                                                                                                                                                 |

|-----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND/DGND | Gnd       | Analog and digital ground are connected internally to a single pin.                                                                                                                                                         |

| A(TIP)    | Output    | Output of A(TIP) power amplifier.                                                                                                                                                                                           |

| B2EN      | Input     | $V_{BAT2}$ enable. Logic Low enables operation from $V_{BAT2}$ . Logic High enables operation from $V_{BAT1}$ . TTL compatible.                                                                                             |

| BGND      | Gnd       | Battery (power) ground                                                                                                                                                                                                      |

| B(RING)   | Output    | Output of B(RING) power amplifier.                                                                                                                                                                                          |

| C3-C1     | Input     | Decoder. TTL compatible. C3 is MSB and C1 is LSB.                                                                                                                                                                           |

| D1        | Input     | Relay1 control. TTL compatible. Logic Low activates the Relay1 relay driver.                                                                                                                                                |

| D2        | Input     | (Option) Relay2 control. TTL compatible. Logic Low activates the Relay2 relay driver.                                                                                                                                       |

| DET       | Output    | Detector. Logic Low indicates that the selected detector is tripped. Logic inputs C3–C1 and E1 select the detector. Open-collector with a built-in 15 $k\Omega$ pull-up resistor.                                           |

| E1        | Input     | (Option) A logic High selects the off-hook detector. A logic Low selects the ground-key detector. TTL compatible.                                                                                                           |

| HPA       | Capacitor | High-pass filter capacitor. A(TIP) side of high-pass filter capacitor.                                                                                                                                                      |

| HPB       | Capacitor | High-pass filter capacitor. B(RING) side of high-pass filter capacitor.                                                                                                                                                     |

| RD        | Resistor  | Detect resistor. Threshold modification and filter point for the off-hook detector.                                                                                                                                         |

| RDC       | Resistor  | DC feed resistor. Connection point for the DC-feed current programming network, which also connects to the receiver summing node (RSN). V <sub>RDC</sub> is negative for normal polarity and positive for reverse polarity. |

| RDCR      |           | Connection point for feedback during ringing.                                                                                                                                                                               |

| RINGIN    | Input     | Ring Signal Input. Pin for ring signal input. Square-wave shaped by external RC filter. Requires 50% duty cycle. CMOS-compatible input.                                                                                     |

| RSGH      | Input     | Saturation Guard High. Pin for resistor to adjust Open Circuit voltage when operating from $V_{\text{BAT1}}$ .                                                                                                              |

| RSGL      | Input     | Saturation Guard Low. Pin for resistor to adjust the anti-saturation cut-in voltage when operating from both $V_{BAT1 \text{ and }} V_{BAT2}$ .                                                                             |

| RSN       | Input     | The metallic current (AC and DC) between A(TIP) and B(RING) is equal to 1000 x the current into this pin. The networks that program receive gain, two-wire impedance, and feed resistance all connect to this node.         |

| RTRIP1    | Input     | Ring-trip detector. Ring-trip detector threshold set and filter pin.                                                                                                                                                        |

| RTRIP2    | Input     | Ring-trip detector threshold offset (switch to $V_{BAT1}$ ). For power conservation in any nonringing state, this switch is open.                                                                                           |

| RYE       | Output    | Common Emitter of RYOUT1/RYOUT2. Emitter output of RYOUT1 and RYOUT2. Normally connected to relay ground.                                                                                                                   |

| RYOUT1    | Output    | Relay/switch driver. Open-collector driver with emitter internally connected to RYE.                                                                                                                                        |

| RYOUT2    | Output    | (Option) Relay/switch driver. Open-collector driver with emitter internally connected to RYE.                                                                                                                               |

| VBAT1     | Battery   | Battery supply and connection to substrate.                                                                                                                                                                                 |

| VBAT2     | Battery   | Power supply to output amplifiers. Connect to off-hook battery through a diode.                                                                                                                                             |

| VCC       | Power     | Positive analog power supply.                                                                                                                                                                                               |

| VNEG      | Power     | Negative analog power supply. This pin is the return for the internal VEE regulator.                                                                                                                                        |

| VTX       | Output    | Transmit Audio. This output is a 0.5066 gain version of the A(TIP) and B(RING) metallic AC voltage. VTX also sources the two-wire input impedance programming network.                                                      |

## **ABSOLUTE MAXIMUM RATINGS**

| Storage temperature55°C to +150°C                                                             |

|-----------------------------------------------------------------------------------------------|

| $V_{CC}$ with respect to AGND/DGND 0.4 V to +7 V                                              |

| $V_{\mbox{\scriptsize NEG}}$ with respect to AGND/DGND 0.4 V to $V_{\mbox{\scriptsize BAT2}}$ |

| V <sub>BAT2</sub> V <sub>BAT1</sub> to GND                                                    |

| V <sub>BAT1</sub> with respect to AGND/DGND:                                                  |

| Continuous                                                                                    |

| BGND with respect to AGND/DGND +3 V to -3 V                                                   |

| A(TIP) or B(RING) to BGND:                                                                    |

| ContinuousV <sub>BAT1</sub> –5 V to +1 V                                                      |

| 10 ms (f = 0.1 Hz) $V_{BAT1}$ -10 V to +5 V                                                   |

| 1 $\mu s$ (f = 0.1 Hz)V <sub>BAT1</sub> -15 V to +8 V                                         |

| 250 ns (f = 0.1 Hz) $V_{BAT1}$ –20 V to +12 V                                                 |

| Current from A(TIP) or B(RING)±150 mA                                                         |

| RYOUT1, RYOUT2 current75 mA                                                                   |

| RYOUT1, RYOUT2 voltage RYE to +7 V                                                            |

| RYOUT1, RYOUT2 transient RYE to +10 V                                                         |

| RYE voltage BGND to V <sub>BAT1</sub>                                                         |

| C3-C1, D2-D1, E1, B2EN, and RINGIN                                                            |

| Input voltage0.4 V to V <sub>CC</sub> + 0.4 V                                                 |

| Maximum power dissipation, continuous,                                                        |

| $T_A = 70^{\circ}C$ , No heat sink (See note):                                                |

| In 32-pin PLCC package1.67 W                                                                  |

| In 28-pin SOIC package1.25 W                                                                  |

| Thermal Data: $\theta_{JA}$                                                                   |

| In 32-pin PLCC package45°C/W typ                                                              |

| In 28-pin SOIC package 60°C/W typ                                                             |

**Note:** Thermal limiting circuitry on chip will shut down the circuit at a junction temperature of about 165°C. The device should never see this temperature and operation above 145°C junction temperature may degrade device reliability. See the SLIC Packaging Considerations for more information.

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability.

## **OPERATING RANGES**

## **Commercial (C) Devices**

| Ambient temperature            | 0°C to +70°C*               |

|--------------------------------|-----------------------------|

| V <sub>CC</sub>                | 4.75 V to 5.25 V            |

| V <sub>NEG</sub>               | 4.75 V to V <sub>BAT2</sub> |

| V <sub>BAT1</sub>              | 40 V to -67 V               |

| V <sub>BAT2</sub>              | 19 V to V <sub>BAT1</sub>   |

| AGND/DGND                      | 0 V                         |

| BGND with respect to AGND/DGND | 100 mV to +100 mV           |

| Load resistance on VTX to grou | nd 20 k $\Omega$ min        |

The Operating Ranges define those limits between which the functionality of the device is guaranteed.

<sup>\*</sup> Functionality of the device from  $0^{\circ}$ C to +70°C is guaranteed by production testing.

## **ELECTRICAL CHARACTERISTICS**

| Description                                                                             | Test Conditions (See Note 1)                   | Min   | Тур   | Max             | Unit  | Note    |

|-----------------------------------------------------------------------------------------|------------------------------------------------|-------|-------|-----------------|-------|---------|

| Transmission Performance                                                                |                                                |       |       |                 | •     |         |

| 2-wire return loss                                                                      | 200 Hz to 3.4 kHz (Test Circuit D)             | 26    |       |                 | dB    | 1, 4, 6 |

| Z <sub>VTX</sub> , analog output impedance                                              |                                                |       | 3     | 20              | Ω     | 4       |

| V <sub>VTX</sub> , analog output offset voltage                                         |                                                | -50   |       | +50             | mV    |         |

| Z <sub>RSN</sub> , analog input impedance                                               |                                                |       | 1     | 20              | Ω     | 4       |

| Overload level, 2-wire and 4-wire, off hook                                             | Active state                                   | 2.5   |       |                 | Vpk   | 2a      |

| Overload level, 2-wire                                                                  | On hook, $R_{LAC} = 600 \Omega$                | 0.88  |       |                 | Vrms  | 2b      |

| THD (Total Harmonic Distortion)                                                         | +3 dBm, BAT2 = −24 V                           |       | -64   | -50             |       |         |

| THD, on hook, OHT state                                                                 | 0 dBm, $R_{LAC}$ = 600 $\Omega$ , BAT1 = -67 V |       |       | <del>-4</del> 0 | dB    | 5       |

| Longitudinal Performance (See Test Circ                                                 | cuit C)                                        |       | •     |                 | •     |         |

| Longitudinal to metallic L-T, L-4 balance                                               | 200 Hz to 3.4 kHz                              | 40    |       |                 | dB    |         |

| Longitudinal signal generation 4-L                                                      | 200 Hz to 800 Hz, Normal polarity              | 40    |       |                 | ub    |         |

| Longitudinal current per pin (A or B)                                                   | Active or OHT state                            | 12    | 28    |                 | mArms | 4       |

| Longitudinal impedance at A or B                                                        | 0 to 100 Hz, T <sub>A</sub> = +25°C            |       | 25    |                 | Ω/pin |         |

| Idle Channel Noise                                                                      |                                                |       |       |                 |       | •       |

| C-message weighted noise                                                                |                                                |       | +7    | +14             | dBrnC |         |

| Psophometric weighted noise                                                             |                                                |       | -83   | -76             | dBmp  | 4       |

| Insertion Loss and Four- to Four-Wire Balance Return Signal (See Test Circuits A and B) |                                                |       |       |                 |       |         |

| Gain accuracy 4- to 2-wire                                                              | 0 dBm, 1 kHz                                   | -0.20 | 0     | +0.20           |       |         |

| Gain accuracy 2- to 4-wire and                                                          | 0 dBm, 1 kHz                                   | -6.22 | -6.02 | -5.82           |       |         |

| 4- to 4-wire                                                                            |                                                |       | _     |                 |       |         |

| Gain accuracy 4- to 2-wire                                                              | OHT state, on hook                             | -0.35 | 0     | +0.35           |       | 3       |

| Gain accuracy 2- to 4-wire and 4- to 4-wire                                             | OHT state, on hook                             |       | dB    |                 |       |         |

| Gain accuracy over frequency                                                            | 300 to 3400 Hz<br>relative to 1 kHz            | -0.10 |       | +0.10           | Q.D   |         |

| Gain tracking                                                                           | +3 dBm to -55 dBm<br>relative to 0 dBm         | -0.10 |       | +0.10           |       | 3, 4    |

| Gain tracking                                                                           | 0 dBm to -37 dBm                               | -0.10 |       | +0.10           |       | 3, 4    |

| OHT state, on hook                                                                      | +3 dBm to 0 dBm                                | -0.35 |       | +0.35           |       | 3       |

| Group delay                                                                             | 0 dBm, 1 kHz                                   |       | 3     |                 | μs    | 1, 4, 6 |

# **ELECTRICAL CHARACTERISTICS (CONTINUED)**

| Description                                                                         | Test Conditions (See Note 1)                                                      | Min               | Тур                       | Max                      | Unit | Note |  |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------|---------------------------|--------------------------|------|------|--|

| Line Characteristics                                                                |                                                                                   |                   |                           |                          | •    |      |  |

| I <sub>L</sub> , Loop-current accuracy                                              | I <sub>L</sub> in constant-current region,<br>B2EN = 0                            | 0.9I <sub>L</sub> | ΙL                        | 1.11 <sub>L</sub>        |      |      |  |

| I <sub>L</sub> , Long loops, Active state                                           | $R_{LDC}$ = 600 $\Omega$ , RSGL = open<br>$R_{LDC}$ = 750 $\Omega$ , RSGL = short | 20<br>20          | 21.7                      |                          |      |      |  |

| I <sub>L</sub> , Accuracy, Standby state                                            | $I_{L} = \frac{\left V_{BATI}\right  - 10 \text{ V}}{R_{L} + 400}$                | 0.8I <sub>L</sub> | ΙL                        | 1.2l <sub>L</sub>        | mA   |      |  |

|                                                                                     | $I_L$ = constant-current region<br>$T_A$ = 25°C                                   | 18                | 27                        | 39                       |      |      |  |

| I <sub>L</sub> LIM                                                                  | Active, A and B to ground OHT, A and B to ground                                  |                   | 55<br>55                  | 110                      |      | 4    |  |

| I <sub>L</sub> , Loop current, Open Circuit state                                   | R <sub>L</sub> = 0                                                                |                   |                           | 100                      |      |      |  |

| I <sub>A</sub> , Pin A leakage, Tip Open state                                      | R <sub>L</sub> = 0                                                                |                   |                           | 100                      | μA   |      |  |

| I <sub>B</sub> , Pin B current, Tip Open state                                      | B to ground                                                                       |                   | 34                        |                          | mA   |      |  |

| V <sub>A</sub> , Standby, ground-start signaling                                    | A to $-48$ V = $7$ k $\Omega$ ,<br>B to ground = $100$ $\Omega$                   | -7.5              | <b>–</b> 5                |                          | V    | 4    |  |

| V <sub>AB</sub> , Open Circuit voltage                                              |                                                                                   | 42                |                           |                          |      | 7    |  |

| Power Supply Rejection Ratio (V <sub>RIPPLE</sub> = 100 mVrms), Active Normal State |                                                                                   |                   |                           |                          |      |      |  |

| V <sub>CC</sub>                                                                     | 50 Hz to 3400 Hz                                                                  | 33                | 50                        |                          |      |      |  |

| V <sub>NEG</sub>                                                                    | 50 Hz to 3400 Hz                                                                  | 30                | 40                        |                          | dB   | 5    |  |

| V <sub>BAT1</sub>                                                                   | 50 Hz to 3400 Hz                                                                  | 30                | 50                        |                          | uБ   |      |  |

| V <sub>BAT2</sub>                                                                   | 50 Hz to 3400 Hz                                                                  | 30                | 50                        |                          |      |      |  |

| Power Dissipation                                                                   |                                                                                   |                   |                           |                          |      |      |  |

| On hook, Open Circuit state                                                         | V <sub>BAT1</sub>                                                                 |                   | 48                        | 100                      |      |      |  |

| On hook, Standby state                                                              | V <sub>BAT2</sub>                                                                 |                   | 55                        | 80                       |      | 9    |  |

| On hook, OHT state                                                                  | V <sub>BAT1</sub>                                                                 |                   | 200                       | 300                      |      |      |  |

| On hook, Active state                                                               | V <sub>BAT1</sub>                                                                 |                   | 220                       | 350                      | mW   |      |  |

| Off hook, Standby state                                                             | $V_{BAT1}$ or $V_{BAT2}$ $R_L = 300 \Omega$                                       |                   | 2000                      | 2800                     |      | 9    |  |

| Off hook, OHT state                                                                 | $V_{BAT1}$ $R_L = 300 \Omega$                                                     |                   | 2000                      | 2200                     |      |      |  |

| Off hook, Active state                                                              | $V_{BAT2}$ $R_L = 300 \Omega$                                                     |                   | 550                       | 750                      |      |      |  |

| Supply Currents                                                                     |                                                                                   |                   |                           |                          |      |      |  |

| I <sub>CC</sub> , On-hook V <sub>CC</sub> supply current                            | Open Circuit state Standby state OHT state Active state—normal                    |                   | 3.0<br>3.2<br>6.2<br>6.5  | 4.5<br>5.5<br>8.0<br>9.0 |      |      |  |

| I <sub>NEG</sub> , On-hook V <sub>NEG</sub> supply current                          | Open Circuit state Standby state OHT state Active state—normal                    |                   | 0.1<br>0.1<br>0.7<br>0.7  | 0.2<br>0.2<br>1.1<br>1.1 | mA   |      |  |

| I <sub>BAT</sub> , On-hook V <sub>BAT</sub> supply current                          | Open Circuit state Standby state OHT state Active state–normal                    |                   | 0.45<br>0.6<br>2.0<br>2.7 | 1.0<br>1.5<br>4.0<br>5.0 |      |      |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

| Description                                         | Test Conditions (See Note 1)                                         | Min               | Тур   | Max            | Unit  | Note |

|-----------------------------------------------------|----------------------------------------------------------------------|-------------------|-------|----------------|-------|------|

| Logic Inputs (C3–C1, D2–D1, E1, and B               | 2EN)                                                                 |                   |       | •              |       |      |

| V <sub>IH</sub> , Input High voltage                |                                                                      | 2.0               |       |                | V     |      |

| V <sub>IL</sub> , Input Low voltage                 |                                                                      |                   |       | 0.8            | V     |      |

| I <sub>IH</sub> , Input High current                |                                                                      | <del>-</del> 75   |       | 40             | μA    |      |

| I <sub>IL</sub> , Input Low current                 |                                                                      | -400              |       |                | μА    |      |

| Logic Output DET                                    |                                                                      |                   |       |                |       |      |

| V <sub>OL</sub> , Output Low voltage                | $I_{OUT}$ = 0.8 mA, 15 k $\Omega$ to $V_{CC}$                        |                   |       | 0.40           | V     |      |

| V <sub>OH</sub> , Output High voltage               | $I_{OUT} = -0.1$ mA, 15 k $\Omega$ to $V_{CC}$                       | 2.4               |       |                | V     |      |

| Ring-Trip Detector Input                            |                                                                      |                   |       |                |       |      |

| Ring detect accuracy                                | IRTD = $\left(\frac{ BAT1  - 1}{RRT1} + 24 \mu A\right) \bullet 335$ | -10               |       | +10            | %     |      |

| Ring Signal                                         |                                                                      | L.                |       | <u> </u>       |       | 1    |

| V <sub>AB</sub> , Ringing                           | Bat1 = $-67$ V, ringload = 1570 $\Omega$                             | 57                | 61    |                | Vpk   |      |

| V <sub>AB</sub> Ringing offset                      | V <sub>RINGIN</sub> = 2.5 V                                          |                   | 0     |                | V     |      |

| $\Delta V_{AB}/\Delta V_{RINGIN}$ (RINGIN gain)     |                                                                      |                   | 180   |                | _     |      |

| Ground-Key Detector Thresholds                      |                                                                      |                   |       |                |       |      |

| Ground-key resistive threshold                      | B to ground                                                          | 2                 | 5     | 10             | kΩ    |      |

| Ground-key current threshold                        | B to ground                                                          |                   | 11    |                | mA    |      |

| Loop Detector                                       |                                                                      |                   |       |                |       |      |

| R <sub>LTH</sub> , Loop-resistance detect threshold | Active, V <sub>BAT1</sub><br>Active, V <sub>BAT2</sub><br>Standby    | -20<br>-20<br>-12 |       | 20<br>20<br>12 | %     | 8    |

| Relay Driver Output (RELAY1 and 2)                  |                                                                      |                   |       |                |       |      |

| V <sub>OL</sub> , On voltage (each output)          | I <sub>OL</sub> = 30 mA                                              |                   | +0.25 | +0.4           | V     |      |

| V <sub>OL</sub> , On voltage (each output)          | I <sub>OL</sub> = 40 mA                                              |                   | +0.30 | +0.8           | v<br> | 4    |

| I <sub>OH</sub> , Off leakage (each output)         | V <sub>OH</sub> = +5 V                                               |                   |       | 100            | μΑ    |      |

| Zener breakover (each output)                       | I <sub>Z</sub> = 100 μA                                              | 6.6               | 7.9   |                | V     |      |

| Zener on voltage (each output)                      | I <sub>Z</sub> = 30 mA                                               |                   | 11    |                | V     |      |

## **RELAY DRIVER SCHEMATIC**

#### Notes:

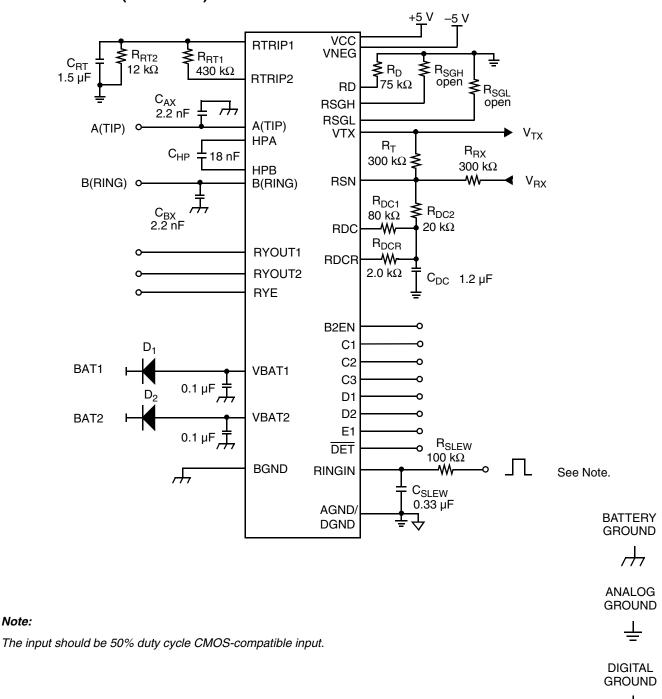

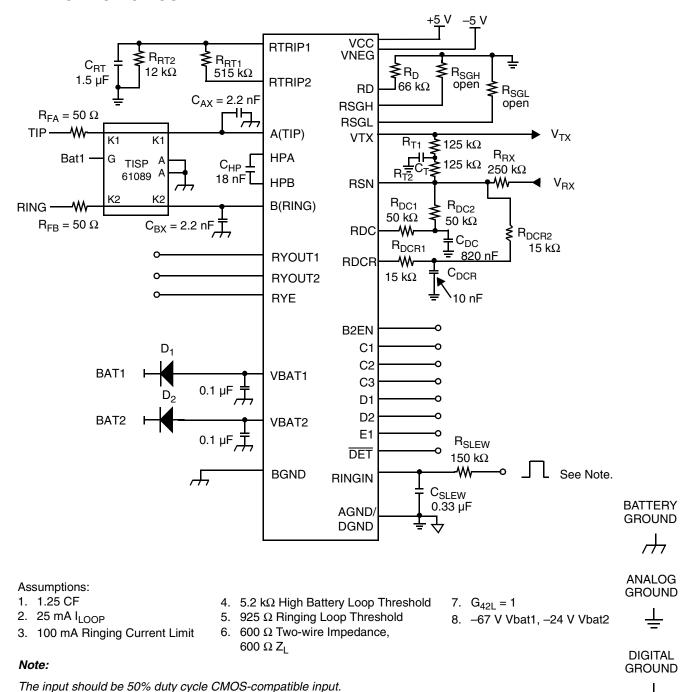

1. Unless otherwise noted, test conditions are BAT1 = -67 V, BAT2 = -24 V,  $V_{CC}$  = +5 V,  $V_{NEG}$  = -5 V,  $R_L$  = 600  $\Omega$ ,  $R_{DC1}$  = 80 k $\Omega$ ,  $R_{DC2}$  = 20 k $\Omega$ ,  $R_D$  = 75 k $\Omega$ , no fuse resistors,  $C_{HP}$  = 0.018  $\mu$ F,  $C_{DC}$  = 1.2  $\mu$ F,  $D_1$  =  $D_2$  = 1N400x, two-wire AC input impedance (ZSL) is a 600  $\Omega$  resistance synthesized by the programming network shown below.  $R_{SGL}$  = open,  $R_{SGH}$  = open,  $R_{DCR}$  = 2 k $\Omega$ ,  $R_{RT1}$  = 430 k $\Omega$ ,  $R_{RT2}$  = 12 k $\Omega$ ,  $C_{RT}$  = 1.5  $\mu$ F,  $R_{SLEW}$  = 150 k $\Omega$ ,  $C_{SLEW}$  = 0.33  $\mu$ F.

- 2. a. Overload level is defined when THD = 1%.

- b. Overload level is defined when THD = 1.5%.

- 3. Balance return signal is the signal generated at  $V_{TX}$  by  $V_{RX}$ . This specification assumes that the two-wire AC load impedance matches the programmed impedance.

- 4. Not tested in production. This parameter is guaranteed by characterization or correlation to other tests.

- 5. This parameter is tested at 1 kHz in production. Performance at other frequencies is guaranteed by characterization.

- Group delay can be greatly reduced by using a Z<sub>T</sub> network such as that shown in Note 1 above. The network reduces the group delay to less than 2 μs and increases 2WRL. The effect of group delay on linecard performance may also be compensated for by synthesizing complex impedance with the QSLAC or DSLAC device.

- 7. Open Circuit  $V_{AB}$  can be modified using RSGH.

- 8.  $R_D$  must be greater than 56  $k\Omega$ . Refer to Table 2 for typical value of  $R_{LTH}$ .

- 9. Lower power is achieved by switching into low-battery state in standby. Standby loop current is returned to V<sub>BAT1</sub> regardless of the battery selected.

Table 1. SLIC Decoding

|       |          |                          | (DET) Output  |            |                   |

|-------|----------|--------------------------|---------------|------------|-------------------|

| State | C3 C2 C1 | 2-Wire Status            | E1 = 1        | E1 = 0     | Battery Selection |

| 0     | 0 0 0    | Open Circuit             | Ring trip     | Ring trip  |                   |

| 1     | 0 0 1    | Ringing                  | Ring trip     | Ring trip  | B2EN              |

| 2     | 0 1 0    | Active                   | Loop detector | Ground key | DZEIN             |

| 3     | 0 1 1    | On-hook TX (OHT)         | Loop detector | Ground key |                   |

| 4     | 1 0 0    | Tip Open                 | Loop detector | Ground key | B2EN = 1**        |

| 5     | 1 0 1    | Standby                  | Loop detector | Ground key | V <sub>BAT1</sub> |

| 6*    | 1 1 0    | Active Polarity Reversal | Loop detector | Ground key | DOEN              |

| 7*    | 1 1 1    | OHT Polarity Reversal    | Loop detector | Ground key | B2EN              |

#### Notes

<sup>\*</sup> Only -1 performance grade devices support polarity reversal.

<sup>\*\*</sup> For correct ground-start operation using Tip Open, V<sub>BAT1</sub> on-hook battery must be used.

## **Table 2. User-Programmable Components**

| $Z_{\rm T} = 500(Z_{\rm 2WIN} - 2R_{\rm F})$                                                                                | $Z_T$ is connected between the VTX and RSN pins. The fuse resistors are $R_F, \mbox{ and } Z_{2WIN}$ is the desired 2-wire AC input impedance. When computing $Z_T,$ the internal current amplifier pole and any external stray capacitance between VTX and RSN must be taken into account.                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $Z_{\rm RX} = \frac{Z_{\rm L}}{G_{42\rm L}} \bullet \frac{1000 \bullet Z_{\rm T}}{Z_{\rm T} + 500(Z_{\rm L} + 2R_{\rm F})}$ | $Z_{RX}$ is connected from $V_{RX}$ to $R_{SN}.  Z_T$ is defined above, and $G_{42L}$ is the desired receive gain.                                                                                                                                                                                                                                                                    |

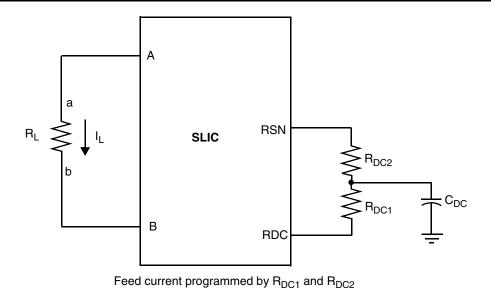

| $R_{DC1} + R_{DC2} = \frac{2500}{I_{LOOP}}$                                                                                 | $R_{DC1}$ , $R_{DC2}$ , and $C_{DC}$ form the network connected to the RDC pin. $I_{LOOP}$ is the desired loop current in the constant-current region.                                                                                                                                                                                                                                |

| $R_{DCR1} + R_{DCR2} = \frac{3000}{Iringlim}$                                                                               | $R_{DCR1}$ , $R_{DCR2}$ , and $C_{DCR}$ form the network connected to the RDCR pin. See Applications Circuit for these components.                                                                                                                                                                                                                                                    |

| $C_{DC} = 19 \text{ ms} \bullet \frac{R_{DC1} + R_{DC2}}{R_{DC1}R_{DC2}}$                                                   |                                                                                                                                                                                                                                                                                                                                                                                       |

| $C_{DCR} = \frac{R_{DCR1} + R_{DCR2}}{R_{DCR1}R_{DCR2}} \bullet 150 \ \mu s$                                                | $C_{DCR}$ sets the ringing time constant, which can be between 15 $\mu s$ and 150 $\mu s$                                                                                                                                                                                                                                                                                             |

| $R_{\rm D}$ = $R_{\rm LTH}$ • 12.67 for high battery state                                                                  | $R_D$ is the resistor connected from the RD pin to GND and $R_{LTH}$ is the loop-resistance threshold between on-hook and off-hook detection. $R_D$ should be greater than 56 $k\Omega$ to guarantee detection will occur in the Standby state. Choose the value of $R_D$ for high battery state; then use the equation for $R_{LTH}$ to find where the threshold is for low battery. |

| Loop-Threshold Detect Equations                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                       |

| $R_{LTH} = \frac{R_D}{12.67}$ for high battery                                                                              | This is the same equation as for ${\rm R}_{\rm D}$ in the preceding equation, except solved for ${\rm R}_{\rm LTH}.$                                                                                                                                                                                                                                                                  |

| $R_{LTH} = \frac{R_D}{11.37}$ for low battery                                                                               | For low battery, the detect threshold is slightly higher, which will avoid oscillating between states.                                                                                                                                                                                                                                                                                |

| $R_{LTH} = \frac{ V_{BAT1}  - 10}{915} \bullet R_D - 400 - 2R_F$                                                            | $R_{LTH}$ standby < $R_{LTH}$ active $V_{BAT1}$ < $R_{LTH}$ active $V_{BAT2}$ , which will guarantee no unstable states under all operating conditions. This equation will show at what resistance the standby threshold will be; it is actually a current threshold rather than a resistance threshold, which is shown by the Vbat dependency.                                       |

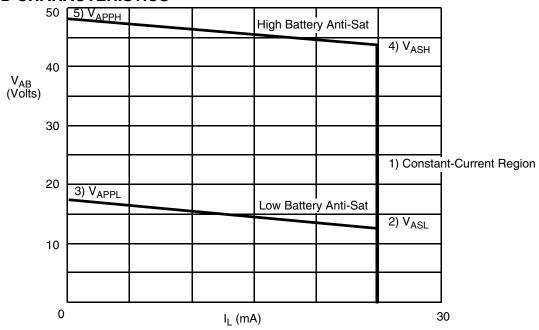

## DC FEED CHARACTERISTICS

Figure 1. Typical V<sub>AB</sub> vs. I<sub>L</sub> DC Feed Characteristics

$$\begin{split} R_{\rm DC} &= \, R_{\rm DC1} + R_{\rm DC2} = 20 \,\, \mathrm{k}\Omega + 80 \,\, \mathrm{k}\Omega = 100 \,\, \mathrm{k}\Omega \\ (V_{\rm BAT1} = \, -67 \,\, \mathrm{V}, \,\, V_{\rm BAT2} \,\, = \, -24 \,\, \mathrm{V}) \end{split}$$

#### Notes:

1. Constant-current region:

$$V_{AB} = I_L R_L = \frac{2500}{RDC} R_L$$

; where  $R_L = R_L + 2R_F$

2. Low battery

$$V_{ASL} = \frac{1000 \bullet (104 \bullet 10^3 + R_{SGL})}{6720 \bullet 10^3 + (80 \bullet R_{SGL})}; \text{ where } R_{SGL} = \text{resistor to GND, B2EN} = \text{logic Low.}$$

Anti-sat region:

$$V_{ASL} = \frac{1000 \bullet (R_{SGL} - 56 \bullet 10^3)}{6720 \bullet 10^3 + (80 \bullet R_{SGL})} \; ; \; \textit{where } R_{SGL} = \textit{resistor to } V_{CC}, \textit{B2EN} = \textit{logic Low}.$$

$R_{SGL}$  to  $V_{CC}$  must be greater than 100 k $\Omega$ .

$$V_{APPL} = 4.17 + V_{ASL}$$

$$I_{\text{LOOPL}} = \frac{V_{\text{APPL}}}{\frac{(R_{\text{DC1}} + R_{\text{DC2}})}{600} + 2R_{\text{F}} + R_{\text{LOOP}}}$$

4. High battery

$$V_{ASH} = V_{ASHH} + V_{ASL}$$

$$V_{\mathrm{ASHH}} = \frac{1000 \bullet (70 \bullet 10^{3} + \mathrm{R_{SGH}})}{1934 \bullet 10^{3} + (31.75 \bullet \mathrm{R_{SGH}})} \; ; \; \textit{where $\mathrm{R_{SGH}}$ = resistor to GND, B2EN = logic High.}$$

$$V_{ASHH} = \frac{1000 \bullet (R_{SGH} + 2.75 \bullet 10^3)}{1934 \bullet 10^3 + (31.75 \bullet R_{SGH})} \; ; \; \textit{where } R_{SGH} = \textit{resistor to } V_{CC}, \textit{B2EN} = \textit{logic High}.$$

$R_{SGH}$  to  $V_{CC}$  must be greater than 100 k $\Omega$ .

$$V_{APPH} = 4.17 + V_{ASH}$$

$$I_{\text{LOOPH}} = \frac{V_{\text{APPH}}}{\frac{(R_{\text{DC1}} + R_{\text{DC2}})}{600} + 2R_{\text{F}} + R_{\text{LOOP}}}$$

## **RING-TRIP COMPONENTS**

$$R_{RT2} = 12 \text{ k}\Omega$$

$$C_{RT} = 1.5 \mu F$$

$$R_{RT1} = 320 \bullet \text{CF} \bullet \frac{V_{\text{BAT1}}}{\text{Vbat} - 5 - (24 \ \mu\text{A} \bullet 320 \bullet \text{CF} \bullet (R_{LRT} + 150 + 2R_{\text{F}}))} \bullet (R_{LRT} + 150 + 2R_{\text{F}})$$

where  $R_{LRT}$  = Loop-detection threshold resistance for ring trip and CF = Crest factor of ringing signal ( $\approx$  1.25)

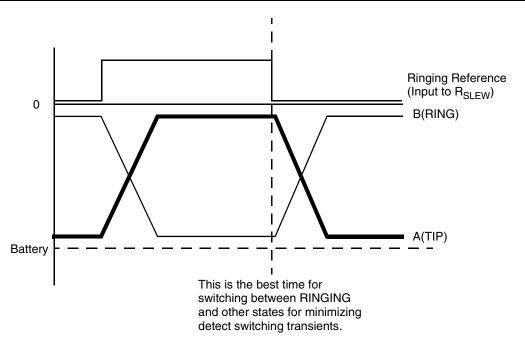

### R<sub>SLEW</sub>, C<sub>SLEW</sub>

Ring waveform rise time  $\approx$  0.214 • (R<sub>SLEW</sub> • C<sub>SLEW</sub>)  $\approx$  tr.

For a 1.25 crest factor @ 20 Hz, tr  $\approx$  10 mS.

$\therefore$  (R<sub>SLEW</sub> = 150 k $\Omega$ , C<sub>SLEW</sub> = 0.33  $\mu$ F.)

$C_{\mbox{\scriptsize SLEW}}$  should be changed if a different crest factor is desired.

Figure 2. Ringing Waveforms

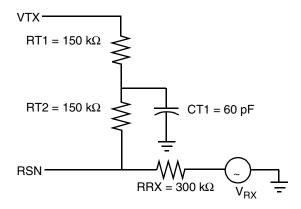

Figure 3. Feed Programming

## **TEST CIRCUITS**

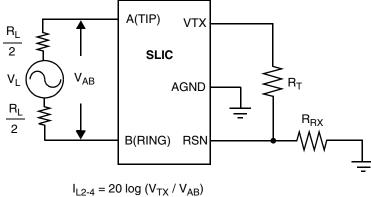

### A. Two- to Four-Wire Insertion Loss

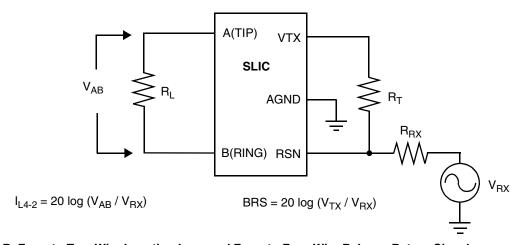

## B. Four- to Two-Wire Insertion Loss and Four- to Four-Wire Balance Return Signal

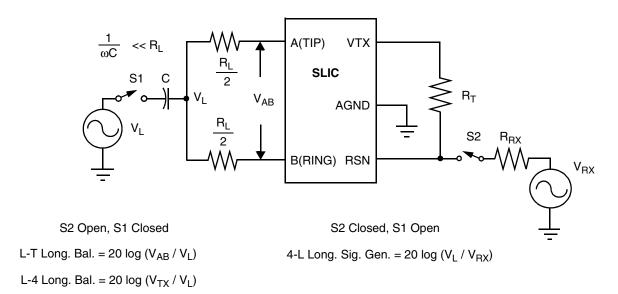

## C. Longitudinal Balance

## **TEST CIRCUITS (continued)**

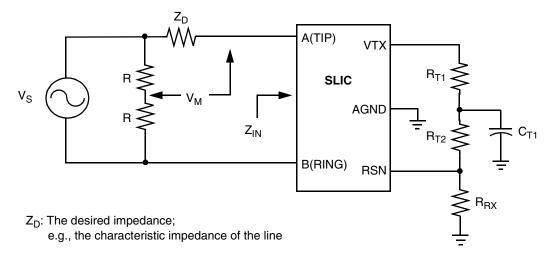

Return loss =  $-20 \log (2 V_M / V_S)$

### D. Two-Wire Return Loss Test Circuit

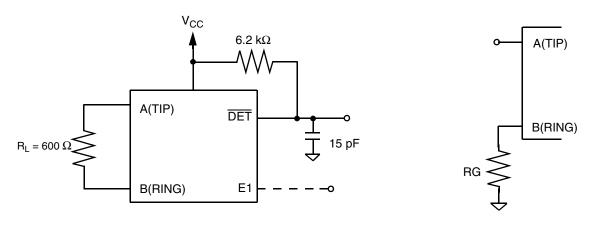

## E. Loop-Detector Switching

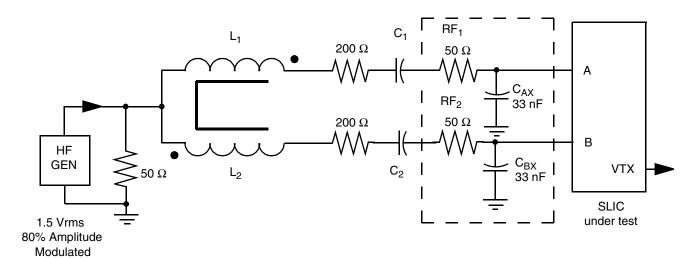

100 kHz to 30 MHz

## F. Ground-Key Switching

**G. RFI Test Circuit**

## **TEST CIRCUITS (continued)**

H. Am79R70 Test Circuit

Note:

## **APPLICATION CIRCUIT**

## I. Application Circuit

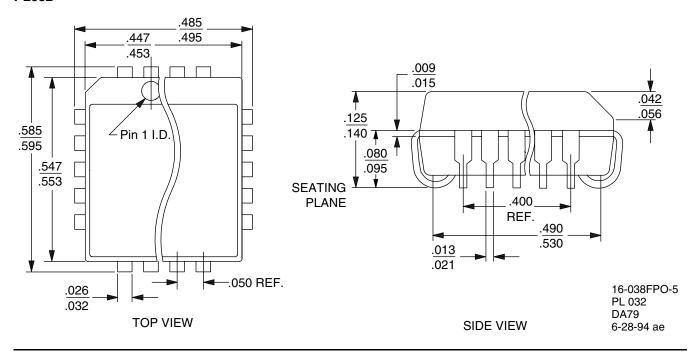

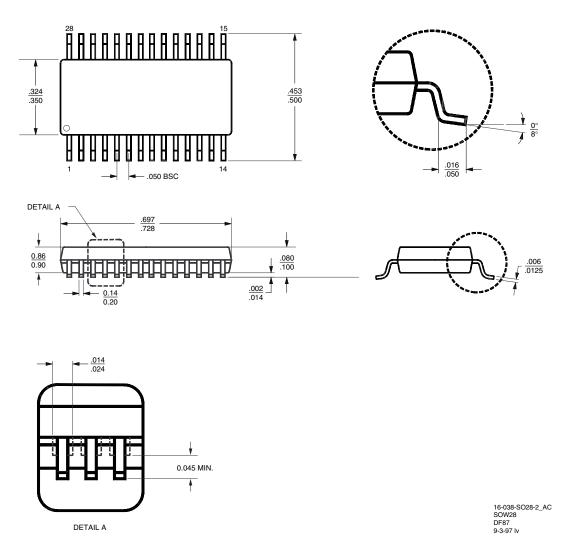

## **PHYSICAL DIMENSIONS**

## PL032

## SOW28

## **REVISION SUMMARY**

## **Revision A to Revision B**

• Minor changes were made to the data sheet style and format to conform to AMD standards.

### **Revision B to Revision C**

- The 28-pin SOIC information and package was added to the Ordering Information and the Connection Diagrams sections.

- The physical dimensions (PL032 and SOW28) were added to the Physical Dimensions section.

- Updated the Pin Description table to correct inconsistencies.

## **Revision C to Revision D**

Changed Ring-Trip Components equation from:

$$R_{RT1} = 300 \bullet \mathrm{CF} \bullet \frac{V_{\mathrm{BAT1}}}{V_{\mathrm{bat} - 3.5 - (15~\mu\mathrm{A} \bullet 300 \bullet \mathrm{CF} \bullet (R_{\mathrm{LRT}} + 150 + 2R_{\mathrm{F}}))}} \bullet (R_{\mathrm{LRT}} + 150 + 2R_{\mathrm{F}})$$

To:

$$R_{RT1} = 320 \bullet \text{CF} \bullet \frac{V_{\text{BAT1}}}{V_{\text{bat}-5} - (24 \ \mu\text{A} \bullet 320 \bullet \text{CF} \bullet (R_{LRT} + 150 + 2R_{\text{F}}))} \bullet (R_{LRT} + 150 + 2R_{\text{F}})$$

| The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. |

| AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.                                                                                                                                                                                                         |

| © 1999 Advanced Micro Devices, Inc. All rights reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Trademarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

AMD, the AMD logo, and combinations thereof, and DSLAC and QSLAC are trademarks of Advanced Micro Devices, Inc.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.